### **Screen Printing Process for High Density Flexible Electronics**

Robert Turunen and Dominique Numakura DKN Research, www.dknresearch.com Hisayuki Kawasaki and Masafumi Nakayama NY Industries, www.ny1.co.jp

A series of advanced screen-printing processes have been developed to build functional high density flexible electronic circuits. Not only do the single layer circuits have fine conductor traces, but double and multi-layer circuits are connected by micro via holes with embedded passives. Utilizing the whole process, an entire electronic circuit system can be built on a flexible substrate.

### Introduction

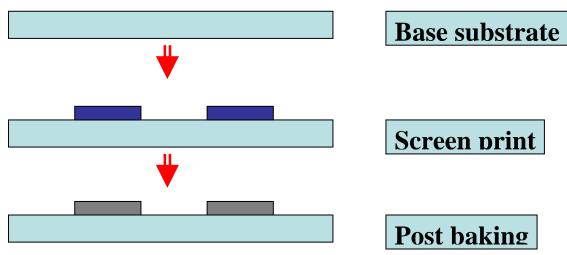

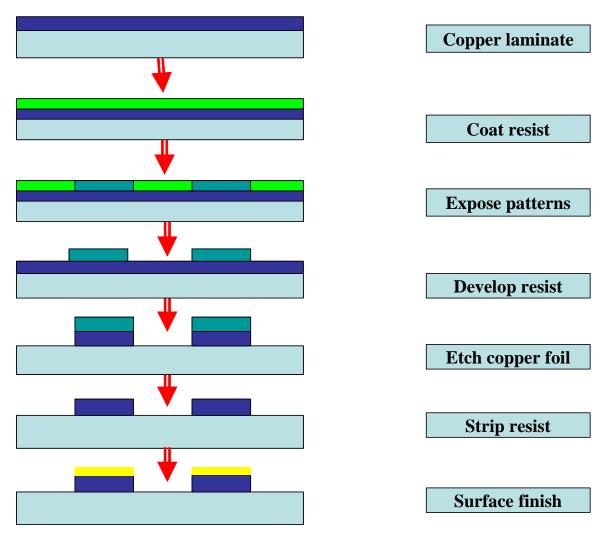

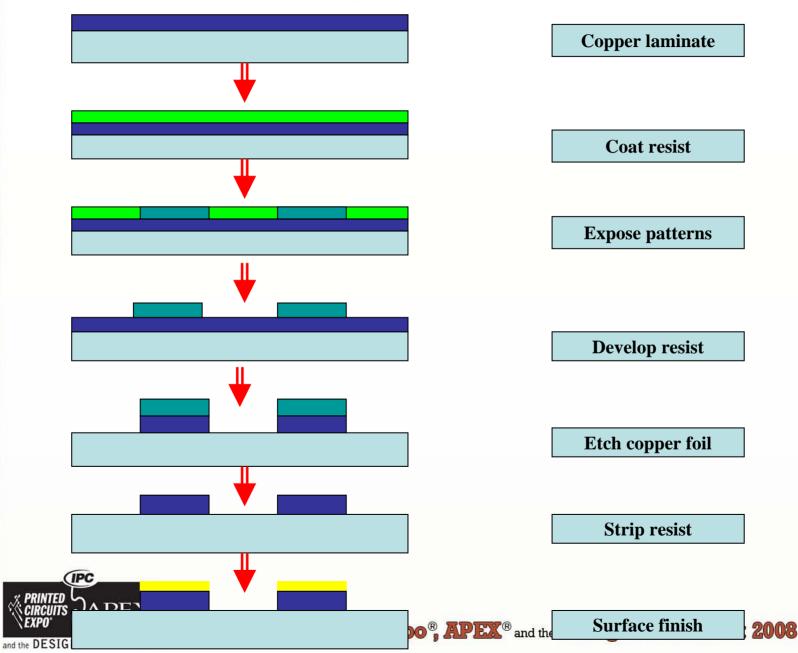

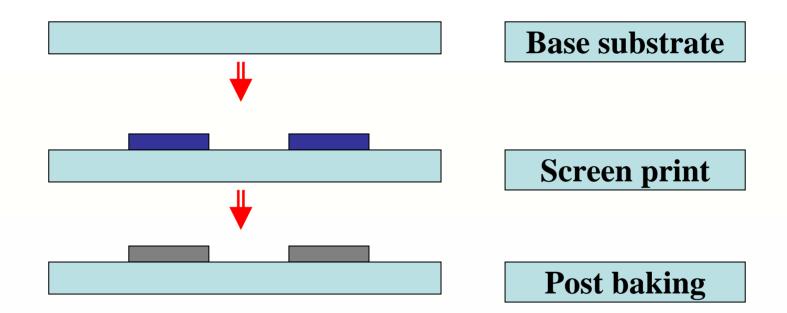

It was a great dream to build complete electronic circuits on a substrate by a simple printing process; this could be the reason why people named it "Printed Circuit Board". The process has been refined to screen-printing conductive pastes on flexible substrates. In the early era, the technology was applied to only low-end circuits because of low resolution of the process and low reliabilities of the materials. Instead, wet etching process with photolithography using copper clad laminates has been employed as the manufacturing process of fine and complicated printed circuit boards for the growing electronics industry. Screen-printing process with conductive paste is much simpler compared to the wet etching process with photolithography as shown in Fig. 1 and Fig. 2.

Figure 1 Basic process of screen-printing

Figure 2 Basic process of photolithography

Furthermore, the screen-printing process is capable of building more layers including insulation materials, resistance materials, dielectric materials for capacitance and more. Therefore, screen-printing process provides great opportunities to produce low cost solutions for embedded passives with multi-layer circuits. Some of the earliest flexible printed circuits were made by screening a conductive paste onto a dielectric base however, reliability concerns by the military lead to the adoption of photolithography on copper clad substrates as the industry standard. Screen-printing process had lower resolution and the available conductive paste materials had much lower conductivity compared to the etched copper traces. Accordingly, the process only found success in areas limited to some applications of consumer electronics.

In recent years a re-emergence of the printing process to mass produce electronic circuits has started to gain favor as the need to cut production costs continues to drive technical advances in the interconnect industry. Various processes including printing etch resists on copper substrates, dot matrix and screen printing conductive materials on dielectric base films have been developed or refined. These processes have been limited by the density they are capable of achieving in volume production.

### **Advanced Screen-Printing Technologies**

A series of advanced screen-printing processes have been developed as the basic manufacturing technologies of the "Printable Electronics" in this study. A new technology concept of "Advanced Screen-Printing Technologies" has been introduced with new manufacturing processes, new materials and new equipment. The new processes provide equivalent or more capabilities to build complicated circuit constructions compared to the traditional subtractive process of copper foils or laminates with the photolithography.

An optimized combination of the process condition and material is capable of generating 30 microns line/space on thin flexible substrates. Supplemental processes are able to generate 80 micron via holes for double sided and multi-layer circuits.

The basic process of the advanced screen-printing processes is the same as traditional screen-printing process as shown in Fig. 1. A paste material is printed on a thin flexible substrate by screen-printing and baked. If necessary, supplemental screen-printing is conducted on the conductor traces. The key of the advanced process is the optimized combination of the materials, screen-printers and screen masks. An optimized process condition generates 30 microns line and space on a thin, smooth substrate using an appropriate conductive paste. Printing machines and screen masks are already capable to screen-print 10 to 20 micron line and space. Research is underway to develop production quantities of conductive paste materials to realize the ultra fine conductors. Multiple RTR processing adds value to the advanced screen-printing process system by achieving low cost manufacturing for the valued flexible electronics.

### **Double & Multi-layer Process**

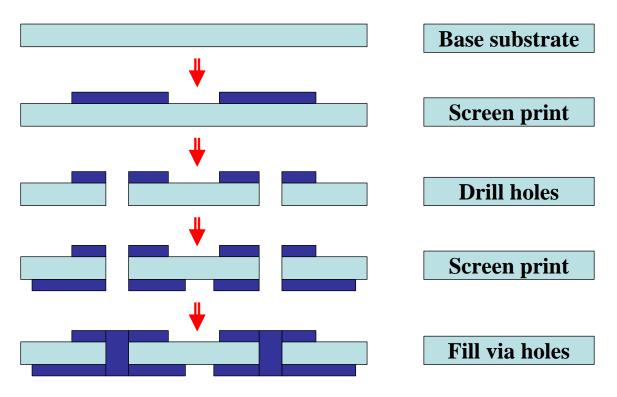

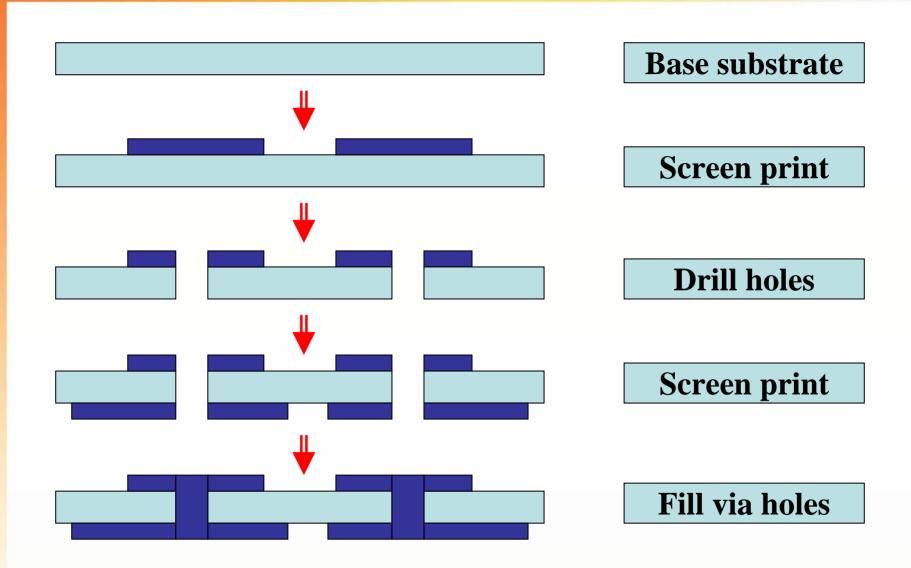

Multiple printing processes with appropriate via hole technologies are able to produce double side and multi-layer circuits. Fig. 3 shows one of the via-hole generation processes for the double side circuits.

Figure 3 Double side process with drilled via holes

First, a conductive paste is screen-printed on a thin plastic film as the first conductor layer. Secondly, small holes are drilled on the conductor pads. The piercing machine with a CCD alignment system minimizes the shifts to less than 50 microns. NC drilling and laser drilling are capable to generate equivalent micro holes on the thin films. Thirdly, the second conductor layer is screen-printed on the other side of the first conductor layer. One more screen-printing of the conductor paste is done to form the via-hole and increases reliability.

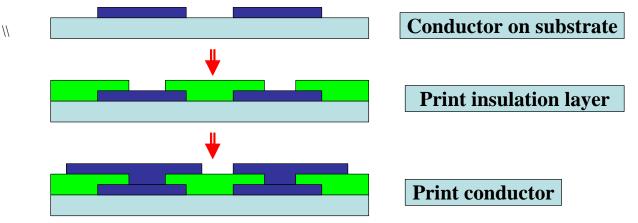

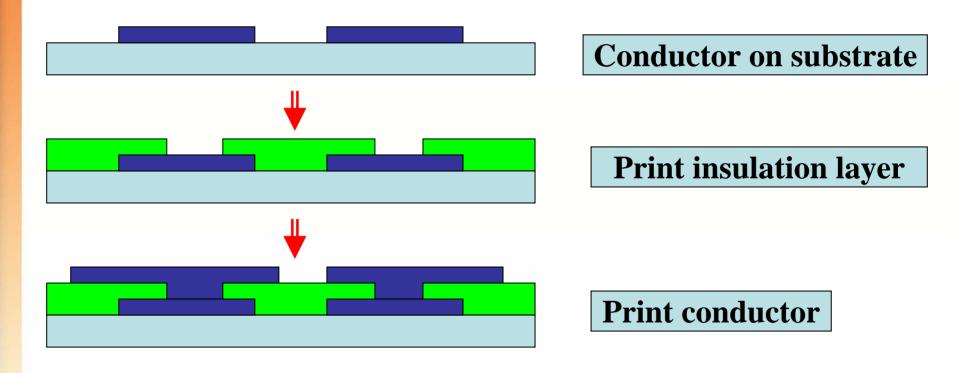

Fig. 4 shows the build-up process of the advanced screen-printing by adding more conductor layers on the basic construction of the flexible circuits.

Figure 4 Build-up process with printed via holes

An insulation layer is screen-printed on the conductor layer with small access openings followed by another screen-printing of the conductor paste. Screen-printer with a CCD alignment system minimizes the shift between layers.

### **Additional Functions by Screen-Printing**

The advanced printing process creates more functionality than copper foil circuits produced by the traditional etching process. The printing process is able to produce not only conductors on substrates but also insulations, capacitances, resistors, inductors and more as embedded components in the multi-layer circuits.

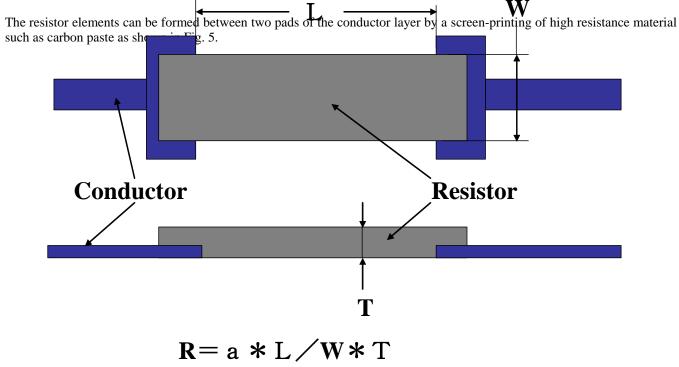

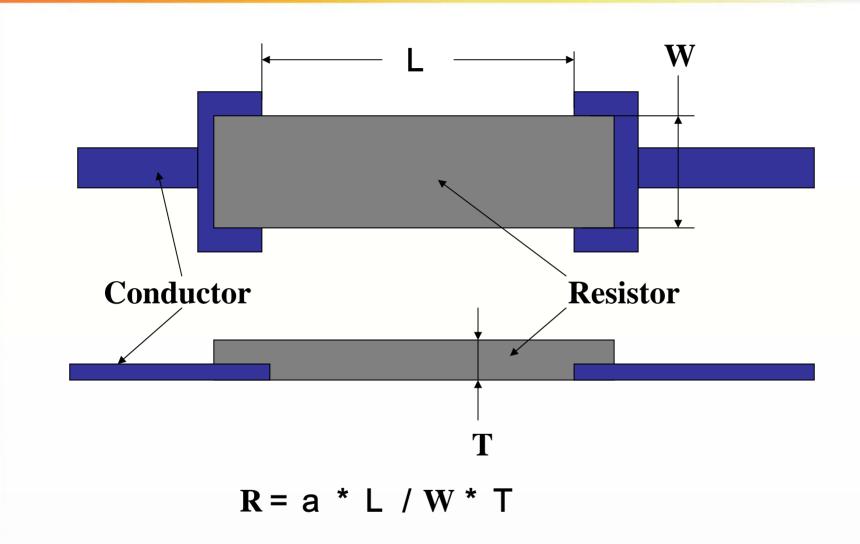

Figure 5 Construction of the printed resistor

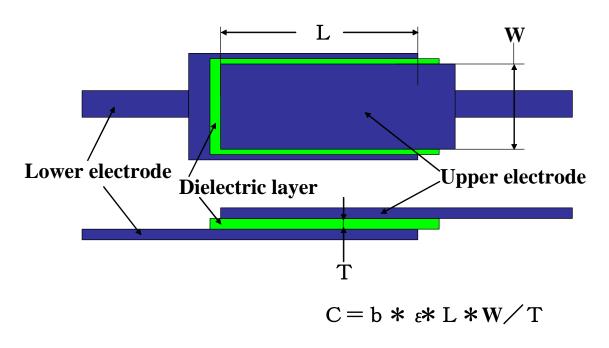

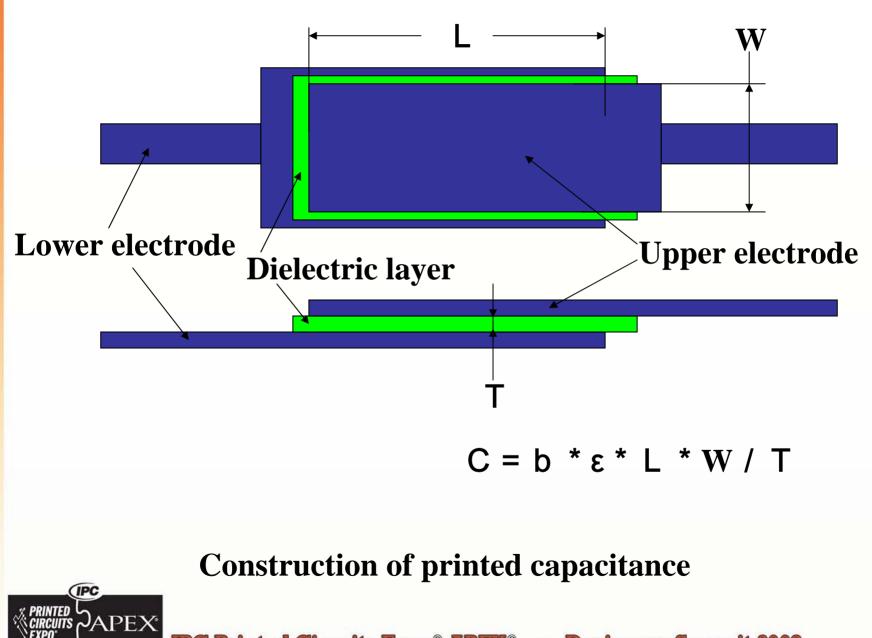

Highly accurate resistors have been made by high resolution screen-printing with suitable dimension control. The resistance value, R of the element is provided by the formula. The resistance of the conductor traces is provided by the same formula. The capacitance elements need three steps of screen-printing on the conductor layer. The capacitance materials with high dielectric constants are screen-printed between the two electrodes as shown in Fig. 6.

**Figure 6 Construction of printed capacitance**

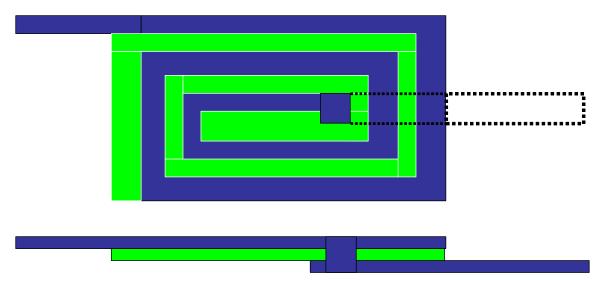

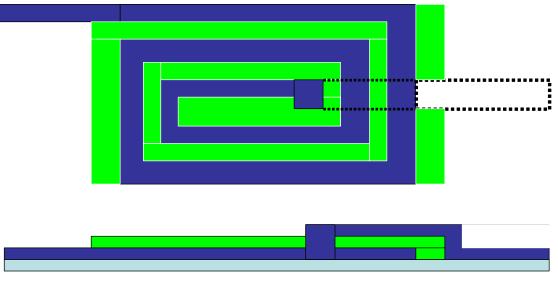

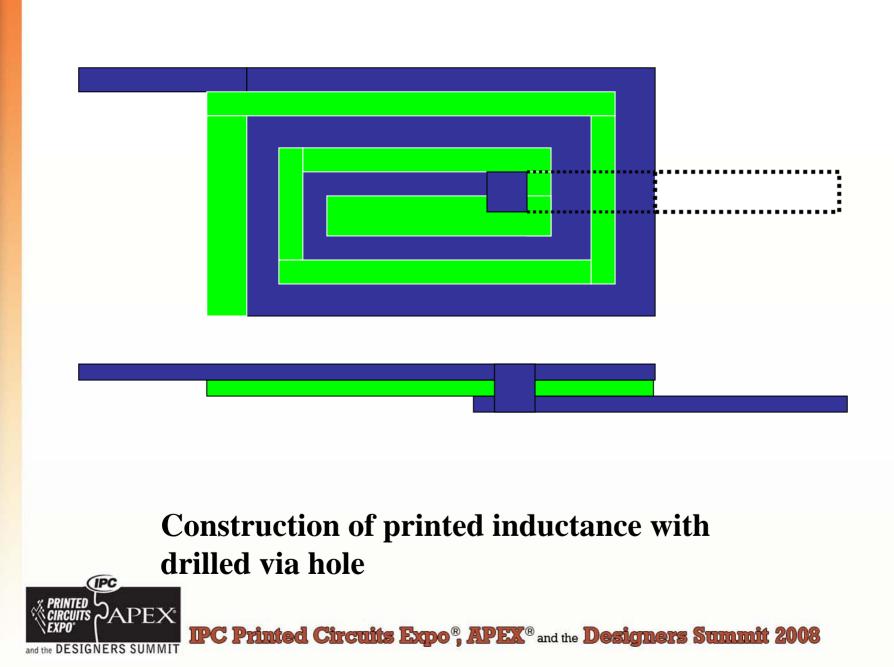

There two kinds of structures to build printed inductors as shown in Fig. 7 and Fig. 8. The first construction uses drilled via holes through the base substrate films.

Figure 7 Construction of printed inductance with drilled via hole

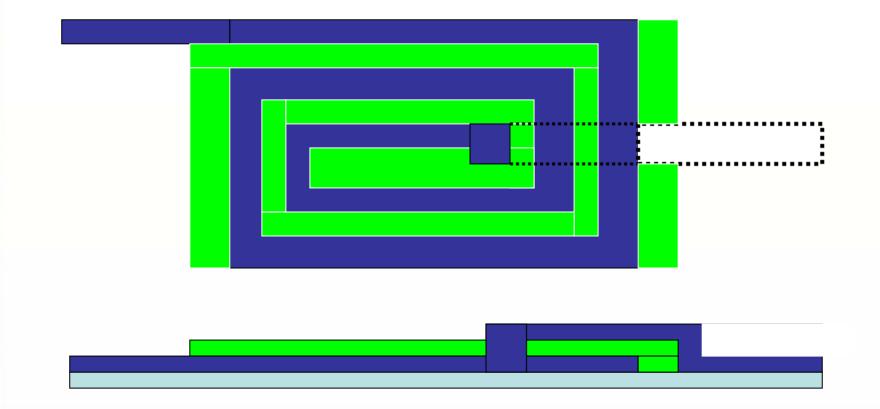

The second construction uses printed via holes on base substrate films. Multiple coils are formed with via hole connections to get larger inductances.

Figure 8 Construction of printed inductance with printed via hole

To build functional electronic circuits on a thin film the advanced screen-printing process has to be repeated multiple times up to ten. Exact dimensional control and alignment are required for both the equipment and conditioning.

### **Printable Electronics Materials**

Materials are key to high performances screen-printing. It is not only the conductive ink materials but also base films, resistant materials, dielectric materials and more. The best performance is provided by the appropriate combination of the materials. Multiple materials have been tried for each layer in this study as follow.

Base film: Polyimide, Polyethylene Naphthalate (PEN) Conductor ink: Silver paste (Several compositions) Resister ink: Silver paste, Carbon paste Insulation ink: Epoxy resin, Polyester resin Dielectric ink: Epoxy resin, Polyimide resin

A coating treatment is used to enhance the bond strength of the layers on the substrate or circuits prior to the screen-printing processes of the materials.

#### **Trials and results**

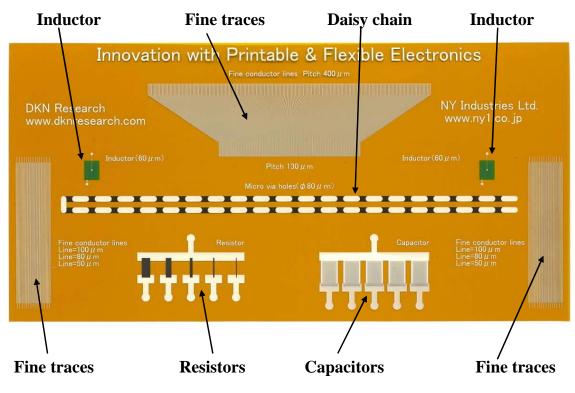

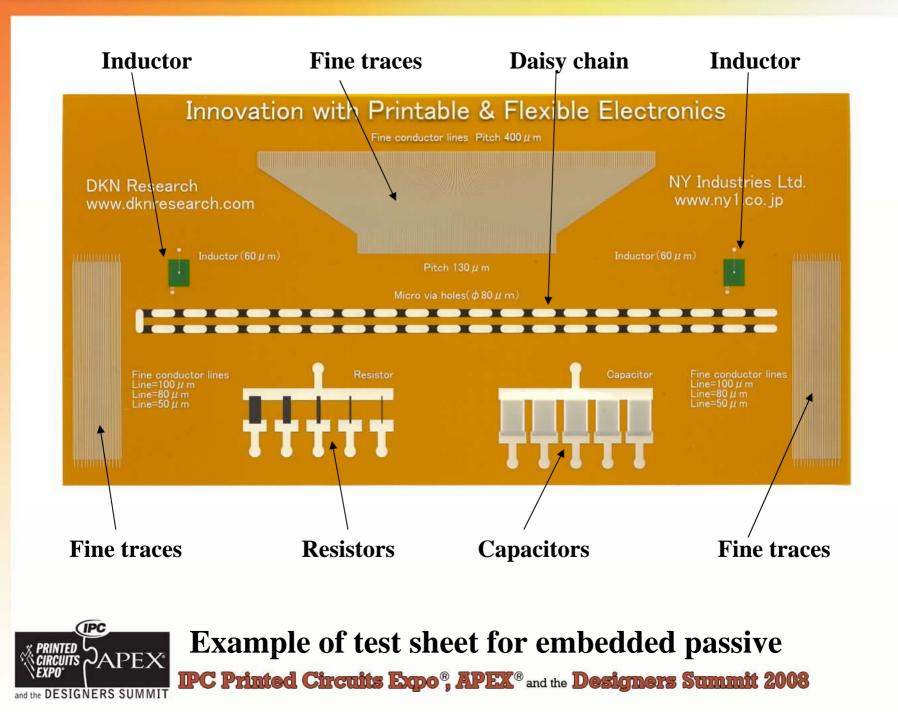

Several test patterns have been generated for the evaluation of the printable flexible electronics. Fig. 9 shows one of the test patterns for the embedded passives with multi-layer flexible circuits. It has multiple fine conductor layers with micro via holes and also has embedded resistors, capacitors and inductors.

Figure 9 Example of test sheet for embedded passive

Over ten screen-printing processes had to be conducted with accurate alignment to complete the whole electronic circuits on the thin film.

Many combinations of the materials for the test vehicles have been tried to achieve appropriate performance of the flexible electronic circuits. Heat resistant substrates such as polyimide film or PEN film are required as the base substrates to survive multiple high temperature processes.

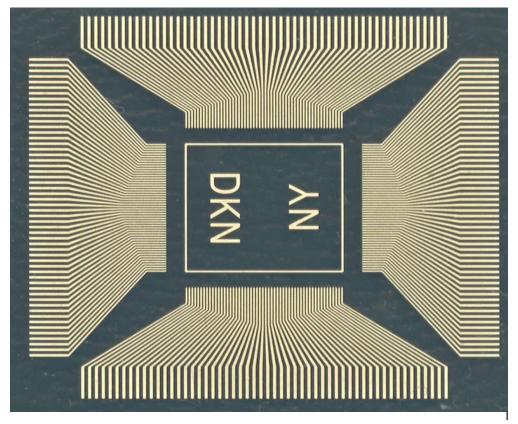

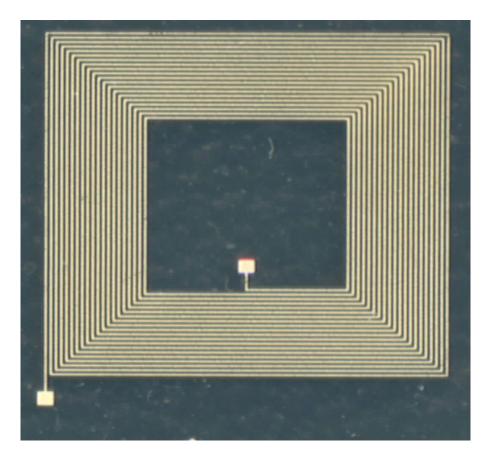

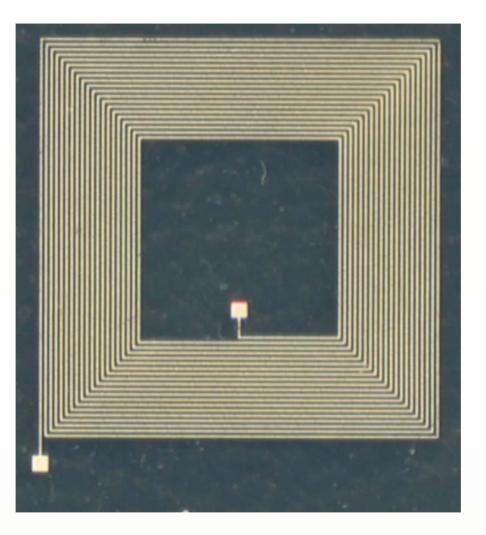

The optimized combinations of the materials and process conditions have yielded up to 60 micron pitch traces (30 micron line/spaces) on the thin substrates. Fig. 10 and Fig. 11 show examples of an IC substrate (150 micron pitch, 75 micron line/space) and a printed coil (100 micron pitch, 50 micron line/space) respectively.

Figure 10 Example of printed IC substrate (150 micron pitch)

Figure 11 Example of printed inductor (100 micron pitch)

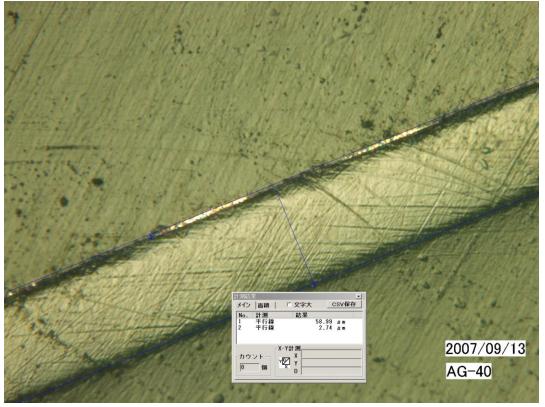

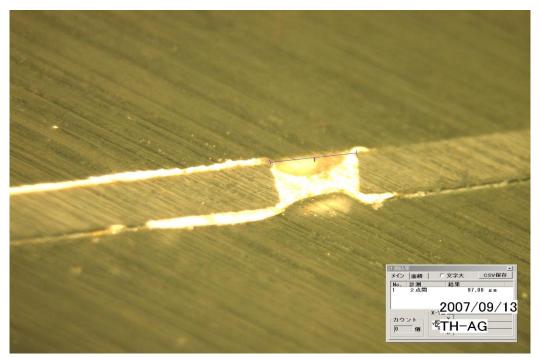

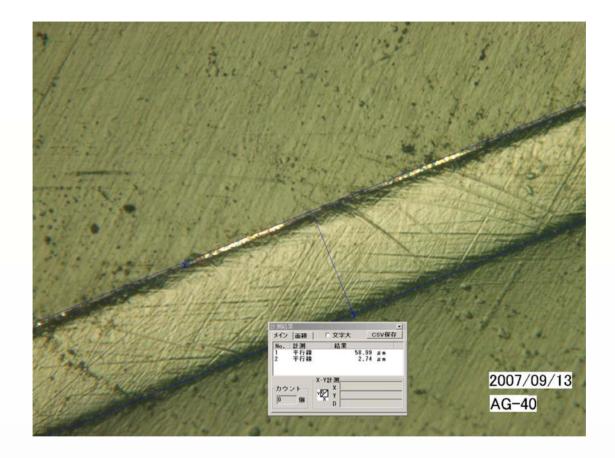

Fig. 12 shows a cross section photo of the fine traces with 80 micron pitch (40 micron line /space) built on a 50 micron thick polyimide film. The cross section photo indicates that the conductor thickness is smaller than 5 microns.

Figure 12 Cross-section of fine traces (80 micron pitch)

Fig. 13 shows a cross section photo of the micro via holes made for the double side circuits. 80 micron diameter holes have been made by micro punching process on a 50 micron thick polyimide film and filled with conductor paste by dual screen-printing process.

Figure 13 Cross-section of drilled micro via hole

The optimized combination between the hole shapes and conductor paste provide reliable via hole access by simple screenprinting process.

### **Electrical Performances**

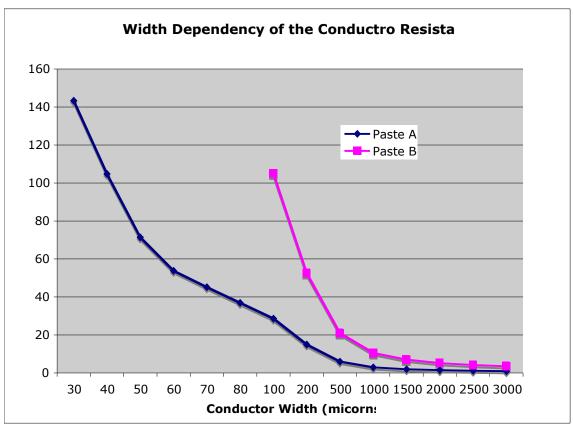

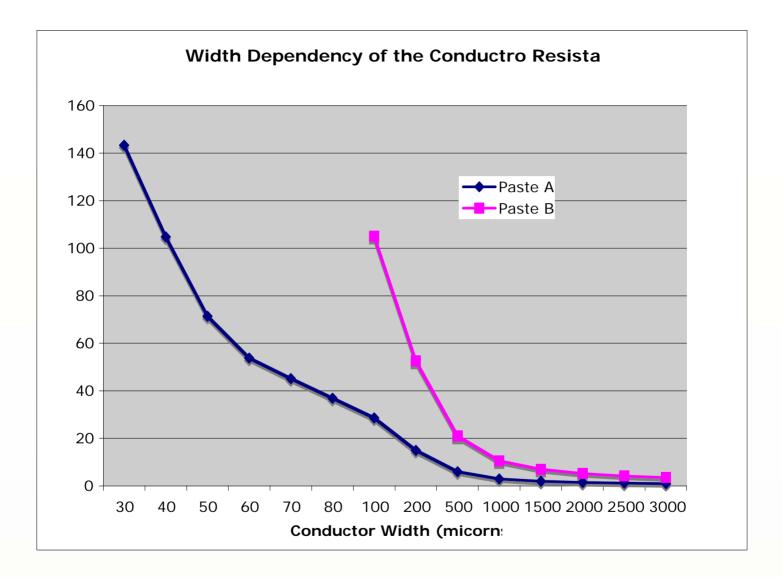

Many electrical properties have been measured for the test vehicles. Fig. 14, Fig. 15 and Fig. 16 show examples of the basic electrical properties.

Conductor resistances of the fine traces are shown in Fig. 14. Paste B in the graph represents the printed traces made by a standard screen-printing condition with conventional silver paste. Paste B cannot provide narrower lines than 100 microns. Paste A represents an optimized combination of the materials and substrates.

Figure 14 Conductor resistance of the fine traces

A silver paste with special binder materials was employed for the trials. Paste A with appropriate substrates and process conditions is capable to generate 30 micron line/space on the thin substrates. The curves are very close to hyperbolic lines calculated by the formula for the broad range of the line width down to 30 microns. The conductivity of the fine lines are very close to the theoretical limit of the conductivity of the paste.

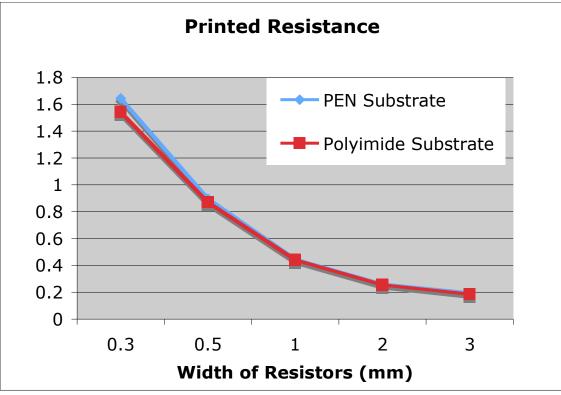

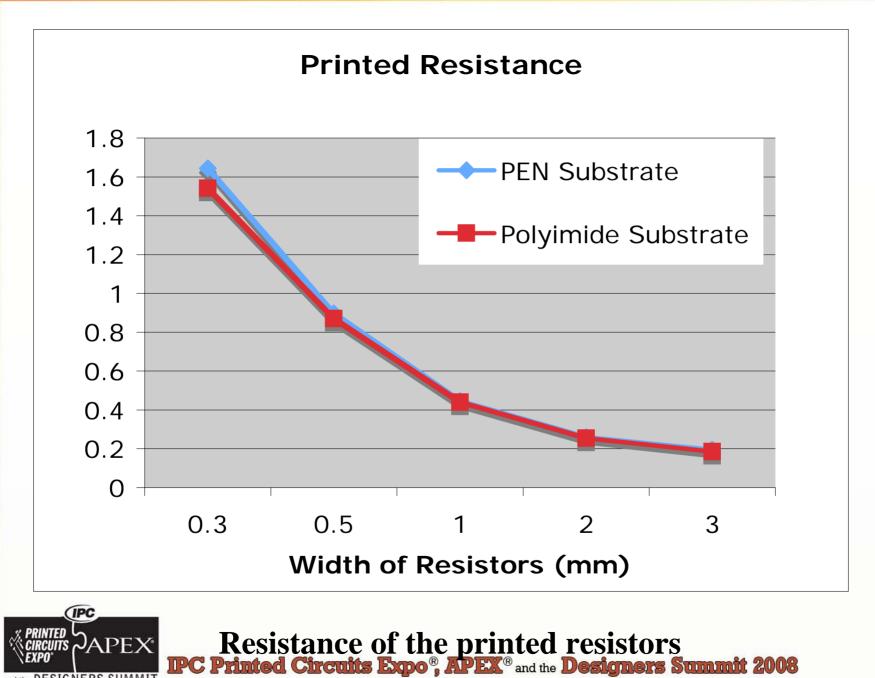

Fig. 15 indicates the resistance of the printed resistors on the film for the different widths with the same length and thickness. The lines in the graph draw good hyperbolic curves close to the theoretical values calculated by the formula. It indicates the advanced screen-printing process provide good accuracies of the printed resistors up to +/- 5% without supplemental trimming process.

Figure 15 Resistance of printed resistors

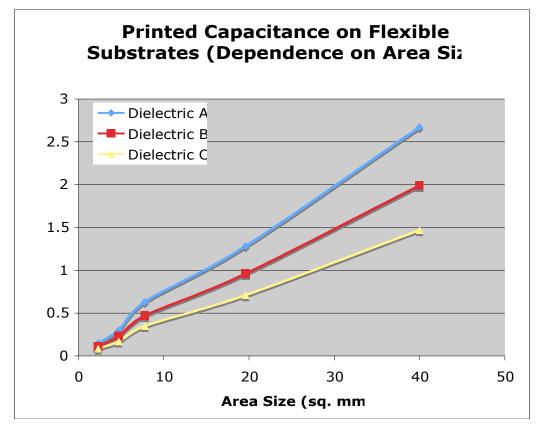

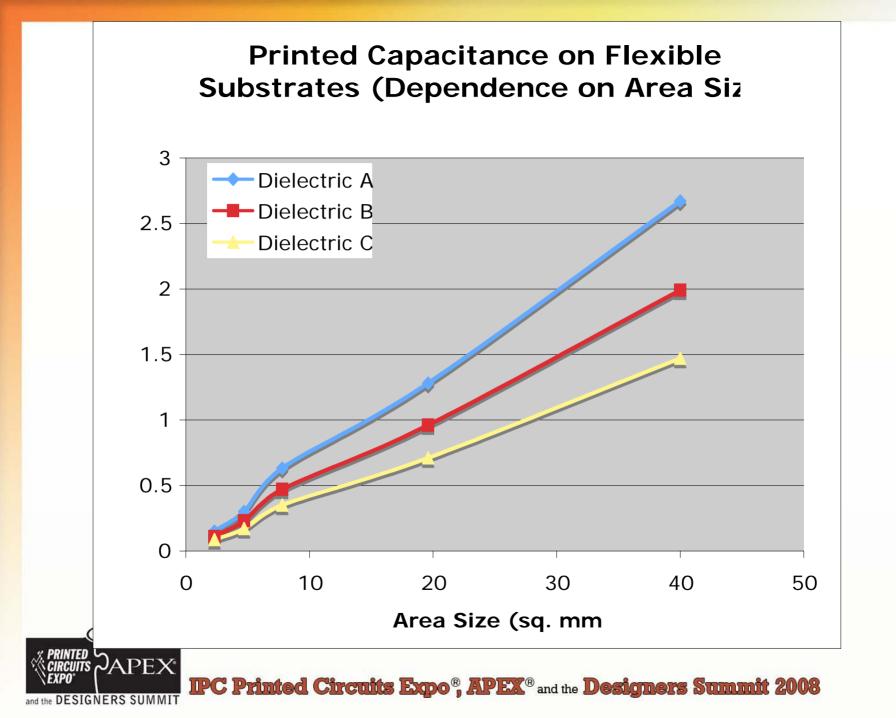

The electrical performances of the printed capacitors with high dielectric constant materials at a frequency of 1 kHz are shown in Fig. 16.

Figure 16 Capacitance of the printed capacitors (1 kHz)

The dependency on the area size of the printed capacitors with a high dielectric constant show high capacitance values with good linearity. It means that a 2 mm square printed capacitor can generate 200 Pico Farad capacitance at 1 kHz frequency on the flexible substrates.

### Conclusion

Screen-printing is not a new technology in the printed circuit industry. However, the combinations of the new paste materials and advanced screen-printing process have created further value of printable flexible electronics that cannot be made by the traditional photolithography process with copper foils. Further, more functionality of the circuits will be generated with new materials in the future.

The technical data evaluated in this study indicates that the advanced screen-printing processes are capable of generating high-density, multi-layer circuits on flexible substrates. They also indicate that it is possible to generate highly accurate embedded passive components in the flexible circuits.

More trials and data are to be completed and the results of producing complete printable flexible electronic systems will be reported in the near future.

### Reference

"Screen Printing for High-Density Flexible Electronics", Robert Turunen, Masafumi Nakayama and Dominique Numakura, Printed Circuit FAB, October, 2007

**Screen Printing Process for High Density Flexible Electronics Robert Turunen and Dominique** Numakura **DKN** Research, www.dknresearch.com Hisayuki Kawasaki and Masafumi Nakayama NY Industries, www.ny1.co.jp

## Overview

Advanced Screen-Printing Technology offers more functionality at a lower price than flexible circuits made by traditional subtractive processes. This innovative printing process produces not only conductors on substrates but also dielectrics, capacitances, resistors, coils, diodes, transistors and more. Multiple printing passes combined with appropriate via hole technologies are able to produce double and multi-layer circuits. Combining the printing process with the other technologies generates more value and complete systems.

# Background

- **Printed** Circuit Board (PCB)

- Early years

- Military Programs

- Reduced Size/Weight

- More Functionality

- Cost Insensitive

- High Reliability

- Process: Photolithography on Clad

# Background

- Commercialization

- Increased Functionality

- Reduced Enclosure Size

- Higher Density

- Cost-Cost-Cost

### **Traditional Photolithography Requires Numerous Steps**

### **Basic process of screen-printing**

Double side process with drilled via holes **PC Printed Circuits Expo<sup>®</sup>**, **APEX<sup>®</sup>** and the **Designers Summit 2008**

IPC

and the DESIGNERS SUMMIT

**APEX**

**Build-up process with printed via holes**

IPC

APEX

SIGNERS SUMMIT

## **Printable Flexible Electronics Advantages**

- Simple processing

- Reduced manufacturing cost

- Flexible

- Complete electronic systems on a flexible substrate

- No wet processing or wet waste

- Reduced environmental waste products

- Friendly to the environment

- Roll to Roll applicable

- Low cost for volume applications

## **Advanced Screen Printing Capabilities**

- 60 Micron Pitch

- 80 Micron Via

- Single, Double and Multi-layer (up to 6)

- RTR Compatible

- Passive Components Capable

- Insulation, Resistors, Inductors, Capacitors

- Reduced Manufacturing Cost

- Environmentally Friendly

**Construction of the printed resistor**

IPC

APEX

SIGNERS SUMMIT

IPC Printed Circuits Expo<sup>®</sup>, APEX<sup>®</sup> and the Designers Summit 2008

SIGNERS SUMMIT

# Construction of printed inductance with <u>printed via hole</u>

IPC

APEX

NERS SUMMIT

### Example of printed inductor (100 micron pitch) Printed Circuits Expor, APEX<sup>®</sup> and the Designers Summit 2008

Cross-section of fine traces (80 micron pitch)

Cross-section of drilled micro via hole (80 micron diameter)

IPC

and the DESIGNERS SUMMIT

### **Conductor resistance of the fine traces**

(IPC

and the DESIGNERS SUMMIT

APEX

SIGNERS SUMMIT

# **Application Opportunities**

- > RF modules

- Small antenna

- Functional sensors devices

- Flat panel displays

- Functional switch boards

- > Touch panel switches

- > Disposable devices

- > Flat panel light sources

- > Low cost cables

- > And more