#### The Study of High Density PCB Reliability

#### Huang Mingli, Zhang Shun, Ju Yuandao Huawei Technologies Co., Ltd. Shenzhen, China

#### Abstract

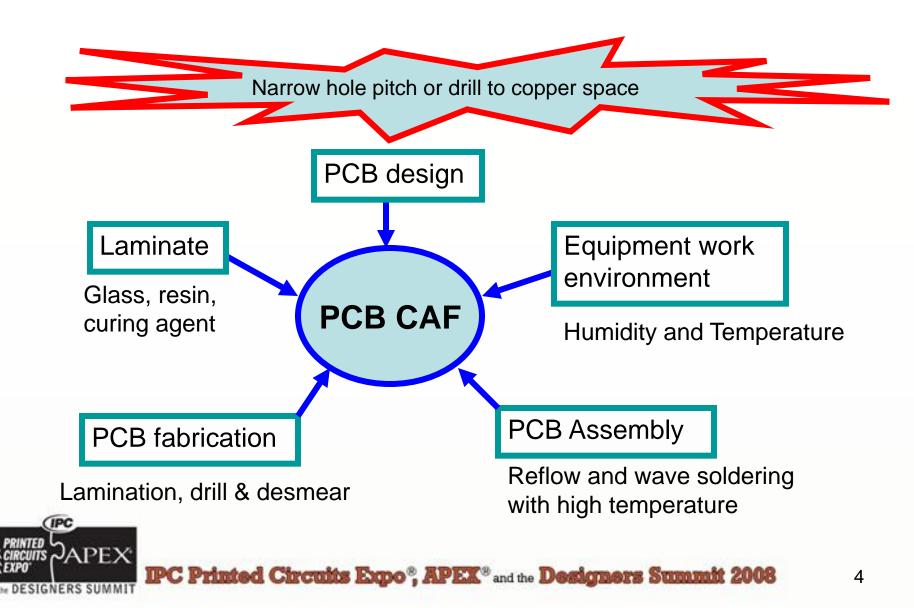

The increase in board routing density, decrease the hole-to-hole spacing and lower to 0.30mm. High aspect ration PTH reliability is not the major issue since the plating copper has at least 20% elongation, but conductive anodic filaments (CAF) and laminate crack are to be concerned since the lead-free assembly and the application of fine pitch components. The lead-free assembly will require higher peak reflow temperature of up to 250degree, and the high temperature will cause thermal damage to PCB, on the other hand, the fine pitch component will require very close hole-to-hole spacing and hole-to-trace spacing, these factors will cause PCB to be easy damaged by the mechanical and thermal stress. The article introduces how to evaluate and avoid these risks.

#### 1. Introduction

The close holes increase the CAF risk. The CAF formation is divided into two steps, and the first step is to form a path between two conductors, but the CAF path is difficult to detect for finished PCB by traditional methods such as cross section or X-ray. In PCB fabrication phase the major factor to form CAF path is inner oxide, lamination, drilling and desmear process, and the PCBA phase the major factor is thermal stress such as reflow and wave soldering and so on.

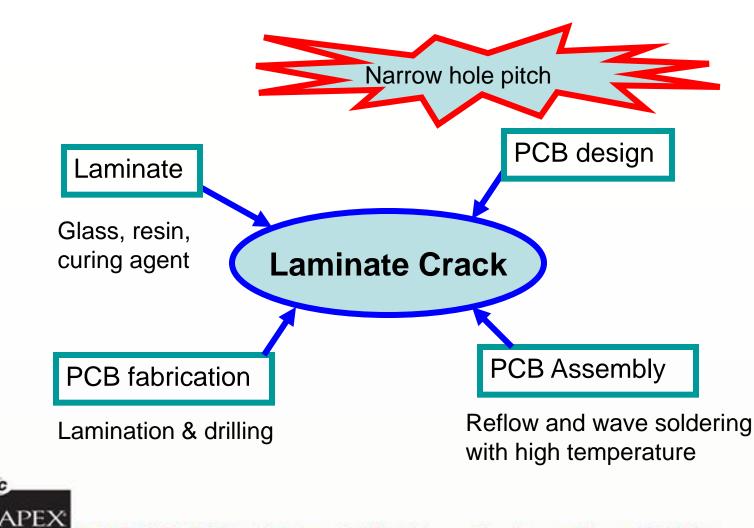

Laminate crack is another reliability issue for high density vias, which is found close thermal vias under BGA, thermal vias of 0.80mm pitch after thermal stress test. The study indicates that the laminate crack is affected by the laminate type, resin content and drill parameter.

#### 2. Inspecting CAF path by dye method

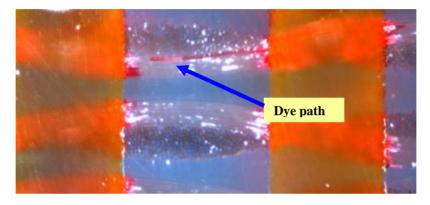

During PCB fabrication phase we detect mechanical and chemical damage after desmear process. If there is dye path in hole-to-hole, hole-to-copper or layer-to-layer, it will be easy to form CAF.

1) The effect of laminate type

Total 4 laminates below are selected for evaluation.

| Parameter         | Unit       | A-M-PN | B-H-DICY | C-H-DICY  | D-H-DICY |

|-------------------|------------|--------|----------|-----------|----------|

| Curing agent      | /          | PN     | DICY     | DICY      | DICY     |

| Filler            | /          | YES    | NO       | NO        | NO       |

| Glass Treatment   | /          | Yes    | No       | No        | No       |

| Water Absorption  | %(PCT/1Hr) | 0.29   | 0.2      | 0.19      | 0.15     |

| $CTE-Z(\alpha 1)$ | PPM/°C     | 48     | 55       | <60       | <60      |

| $CTE-Z(\alpha 2)$ | PPM/°C     | 260    | <300     | <300      | <300     |

| TG(DSC)           | °C         | 135    | 180      | 175       | 175      |

| TMA-T260          | Min        | >120   | 60       | >30(60)   | 38       |

| TD(TGA)           | °C         | 365    | 355      | >325(336) | 304      |

The test vehicle is 12 layers PCB with 3.0mm thickness, all vias use 0.30mm drill bit, two different via pitches are 0.60mm and 0.70mm, and the PCB fabrication is using normal parameters. After PCB desmear, vias are dyed, then cross section for inspection.

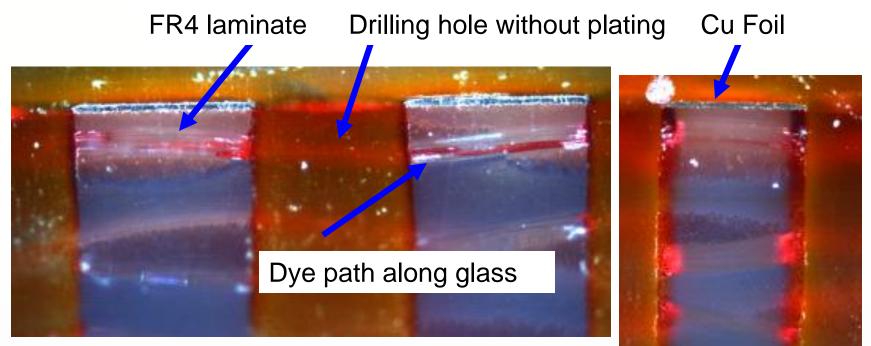

a) The glass adjacent to outer layer is easy to be damaged because of mechanical stress, which should be induced by drill bit and drill parameter mainly.

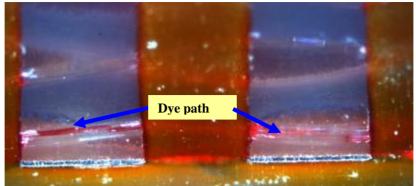

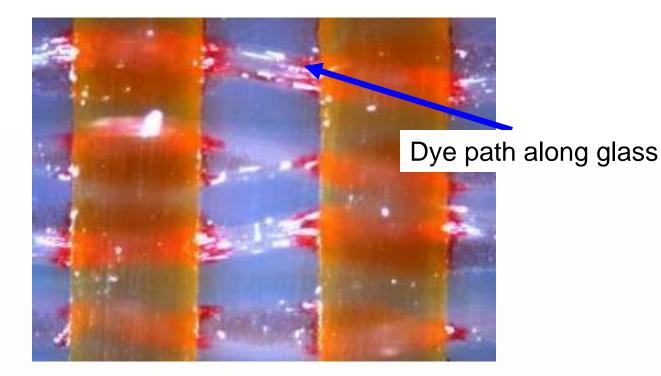

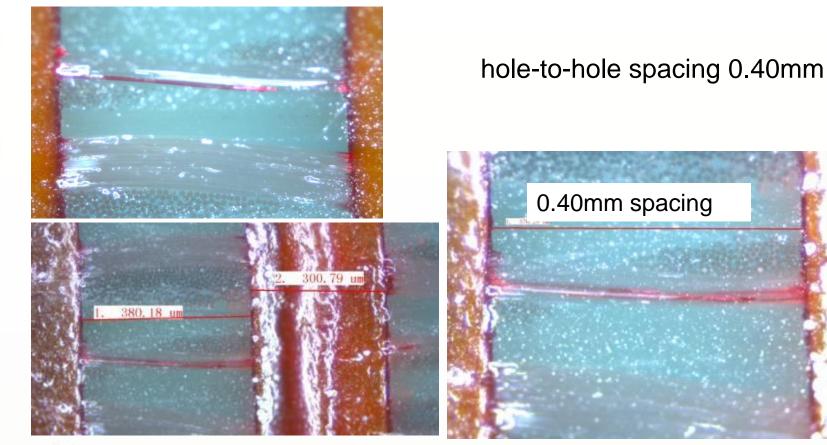

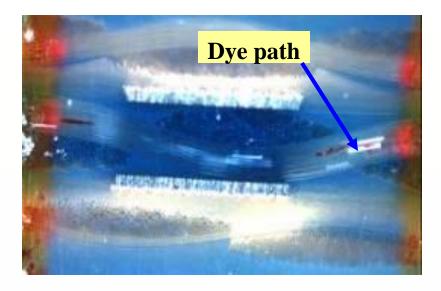

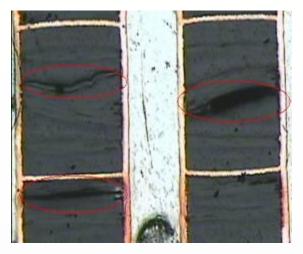

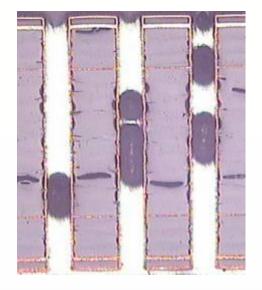

Figure 01 C-H-DICY dye path formation (0.30mm spacing)

Figure 02 C-H-DICY dye path formation (0.30mm spacing)

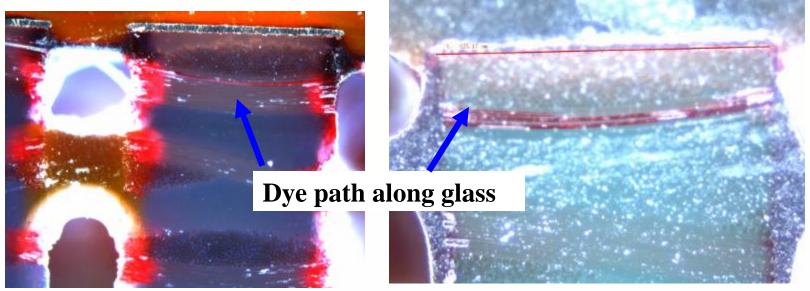

b) When the drill to drill spacing is 0.30mm, it's easy to form dye path along glass for DICY laminates, also 0.40mm drill to drill spacing has obvious dye path for some DICY laminates, but the PN laminate shows better bonding strength between resin and glass, and no dye path is detected.

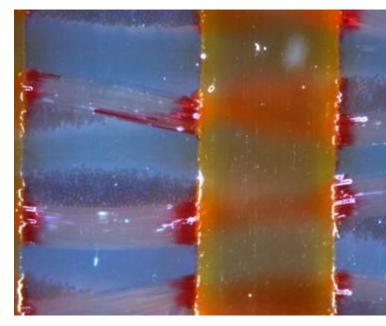

Figure 03 Hole-to-hole spacing 0.30mm (D-H-DICY)

Figure 04 Hole-to-hole spacing 0.30mm (B-H-DICY)

Figure 05 hole-to-hole spacing 0.30mm(C-H-DICY)

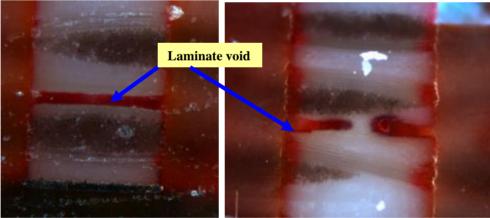

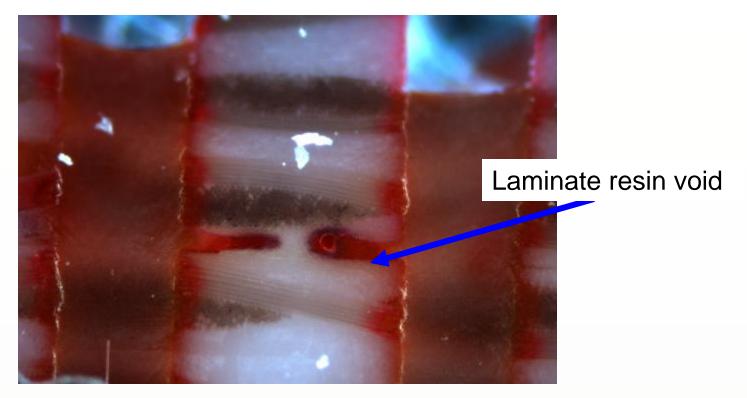

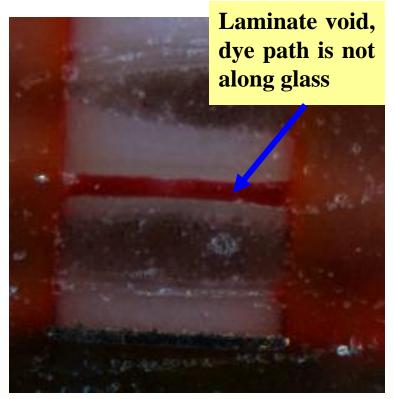

c) A-M-PN is PN curing agent laminate with filler and there are more laminate voids, so dye path is formed by the lamination voids, not along the glass.

Figure 06 A-M-PN dye path formation

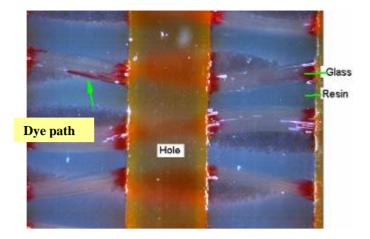

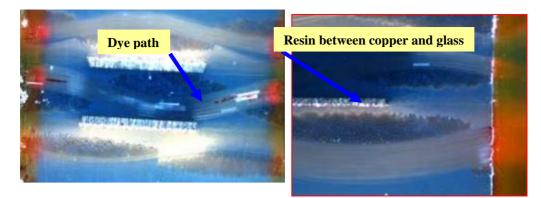

d) Fully dye path from hole to inner copper is not found, since there is no glass weave other than resin between glass and copper.

Figure 07 hole-to-copper damage

2) The effect of PCB fabrication parameter

Use DOE to test the effect of fabrication parameter as follows:

| Factor | Black Oxide     | Lamination  | Drill parameter  | Drill bit        | Desmear |

|--------|-----------------|-------------|------------------|------------------|---------|

| 1      | new rinse water | 190°C 60min | Normal Chip load | New drill bit    | 1 time  |

| 0      | old rinse water | 180°C 40min | Lower chip load  | Re-sharp 3 times | 2 times |

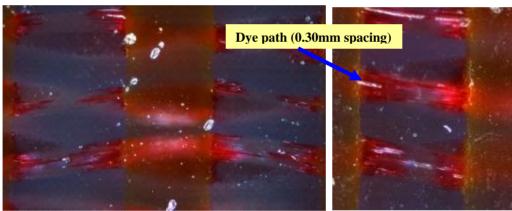

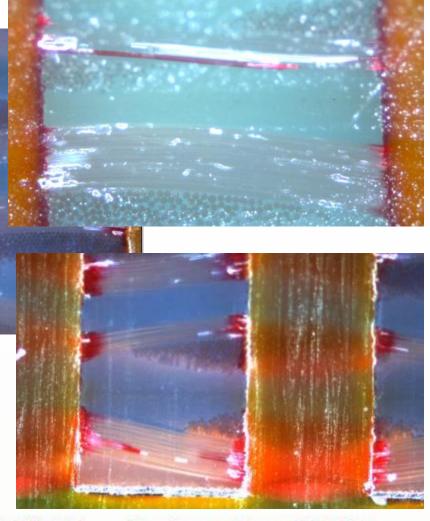

The re-sharp 3 times drill bit will cause long wicking, if hole-to-hole spacing is lower to 0.30mm, the wicking also can form a path of CAF. All test results prove that drill bit and drill parameter are major factors to form CAF.

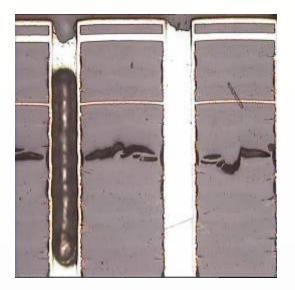

Figure 08 long wicking to form a dye path

#### 3. Verify the CAF failure by Insulation Resistance test

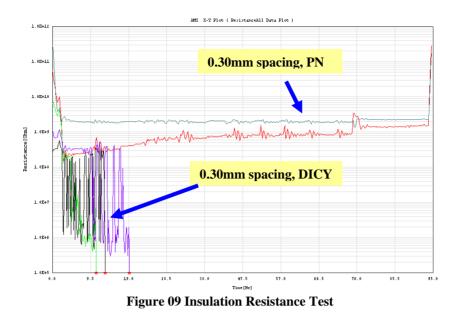

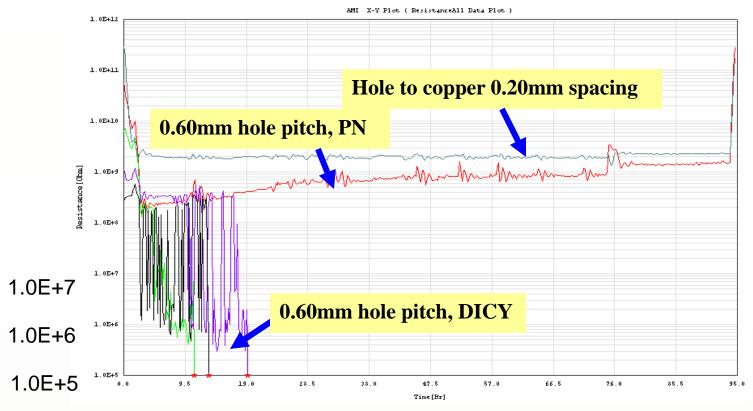

After 3 times lead-free reflow pretreatment, test vehicles are to keep in environment chamber of 85% RH and  $85^{\circ}$ C with both bias and test voltage 100V, and the insulation resistance is monitored online.

For most test vehicles with DICY laminates, the insulation resistance of 0.30mm drill-to-drill spacing drops below 10<sup>5</sup> ohms within 48hours, on some coupons of 0.40mm drill-to-drill spacing also can't pass the 240hours test, by contraries, the test vehicles with PN material show high insulation resistance within 240hours tests, also the hole to inner copper has high insulation resistance within 240hours.

#### 4. Laminate crack

Laminate crack has been the bottleneck of high density design. By means of experiment and fail cases analysis, it is found that laminate crack often occurred at the center of PCB and relies heavily on hole space, board thickness, laminate type(resin content, glass weave, Tg, Td, CTE, T288), pattern design, etc.

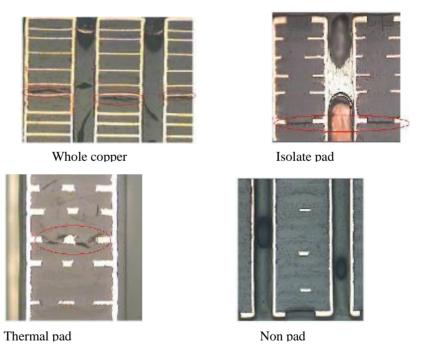

In addition, it also has relation to PCB fabrication. In general closer hole spacing and thicker board have higher risk of laminate crack or delamination between holes. The laminate crack possibility: whole copper > isolate pad > thermal pad > non pad. Besides, via plugging can block thermal transport and improve laminate crack.

Figure 10 Laminate crack degree for different pad design upon exposure to 288°C, 10s, 3 times

#### 6. Summary

With increase PCB density we should make more experiments on laminate selection and process optimization, in general low CTE-Z and high Td material has better performance.

If the drill-to-drill spacing is lower to 0.40mm, it is possible to avoid the CAF risk, but it is necessary to select proper laminates, and make some adjustment on PCB fabrication.

In general the PN curing agent FR4 shows better anti-CAF performance than DICY curing agent FR4, but should take care the lamination void issue, and PCB fabricator should adjust lamination parameter to meet the quality requirement.

Using dye method can inspect the laminate damage easily during PCB fabrication, we can define the CAF risk via dye path formation, and also dye method shows the wicking effect for improving the drill quality or making laminate selection.

Laminate crack is also related to the laminate, the laminate with good thermal resistance can reduce the laminate crack, besides it is necessary to reduce the thermal damage via design and via plugging.

#### THE STUDY OF HIGH DENSITY PCB RELIABILITY

Huang Mingli, Zhang Shun, Ju Yuandao Huawei Technologies Co., Ltd. Email: Huangml@huawei.com

C Printed Circuits Expo<sup>®</sup>, APEX<sup>®</sup> and the Designers Summit 2008

# Content

- The risk of High density PCB

- CAF Risk

- Laminate crack

- Summary

IPC Printed Circuits Expo<sup>®</sup>, APEX<sup>®</sup> and the Designers Summit 2008

### The risk of High density PCB

What should be taken care for high density PCB?

- 1) PTH reliability: High aspect ration PTH reliability is not the major issue since the plating copper has high elongation up to 30%.

- 2) Conductive anodic filaments (CAF) risk behaves as insulation resistance degrading between patterns inside PCBs, especially narrow hole-to-hole spacing is more susceptible to CAF, since narrow holes is easy damaged by the mechanical and thermal stress.

- 3) Laminate crack can be found after thermal tress, also it's susceptibility for narrow hole pitch, 0.80mm pitch BGA application should take care the laminate crack.

#### The risk of High density PCB

### The risk of High density

C Printed Circuits Expo<sup>®</sup>, APEX<sup>®</sup> and the Designers Summit 2008

IPC

# Content

- The risk of High density PCB

- CAF Risk

- Laminate crack

- Summary

IPC Printed Circuits Expo<sup>®</sup>, APEX<sup>®</sup> and the Designers Summit 2008

### **CAF** Risk

The CAF formation is divided into two steps:

- 1) The first step is to form a path between two conductors, it's separation of glass and epoxy.

- 2) The second step is electrochemical reaction.

In PCB fabrication phase the major factor to form CAF path is lamination, drilling and desmear process, and in PCBA phase the major factor is thermal stress such as reflow and wave soldering.

In general CAF is formed along fiber glass, but it is difficult to detect the separation of glass and resin in finished PCB by traditional methods such as cross section or X-ray, the article will introduce a dye method to inspect the CAF path.

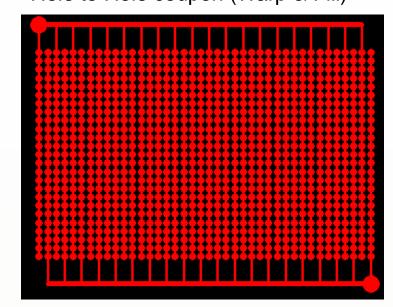

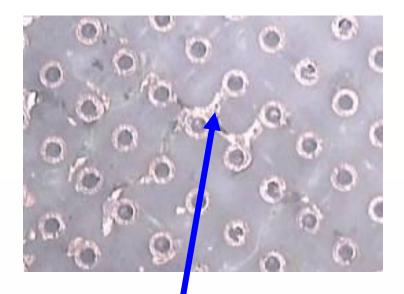

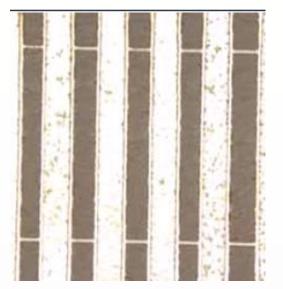

### CAF Risk-Test Vehicle

**CAF** Test Vehicle

PCB Layer Count: 12 layers Board Thickness: 3.0mm Drill bit: 0.30mm drill bit Hole pitch: 0.70mm, 0.60mm Drill to copper Clearance: 0.20mm, 0.25mm

Pattern design:

Drill to copper coupon

Hole to Hole coupon (Warp & Fill)

C Printed Circuits Expo<sup>®</sup>, APEX<sup>®</sup> and the Designers Summit 2008

### CAF Risk-Test Vehicle

#### Total 4 laminates below are selected for evaluation.

| Parameter             | Unit   | A-M-PN | B-H-DICY | C-H-DICY  | D-H-DICY |

|-----------------------|--------|--------|----------|-----------|----------|

| Curing agent          | /      | PN     | DICY     | DICY      | DICY     |

| Filler                | /      | YES    | NO       | NO        | NO       |

| Glass spray Treatment | /      | Yes    | No       | No        | No       |

| CTE-Z(a1)             | PPM/°C | 48     | 55       | <60       | <60      |

| CTE-Z(a2)             | PPM/°C | 260    | <300     | <300      | <300     |

| TG(DSC)               | °C     | 135    | 180      | 175       | 175      |

| TMA-T260              | Min    | >120   | 60       | >30(60)   | 38       |

| TD(TGA)               | °C     | 365    | 355      | >325(336) | 304      |

IPC Printed Circuits Expo<sup>®</sup>, APEX<sup>®</sup> and the Designers Summit 2008

How to dye the PCB?

Since lamination, drill and desmear are the major factors to form CAF in PCB fabrication. After PTH plating, the copper will surround the hole wall to prevent the dye solution soak, so PCB test coupon should be dyed after desmear process or make the holes as non-plated.

Must be vacuum with dye solution

C Printed Circuits Expo<sup>®</sup>, APEX<sup>®</sup> and the Designers Summit 200

Hole to Hole dye path

Dye path formation (0.30mm spacing, C-H-DICY)

PC Printed Circuits Expo<sup>®</sup>, APEX<sup>®</sup> and the Designers Summit 2008

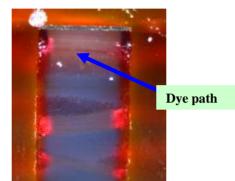

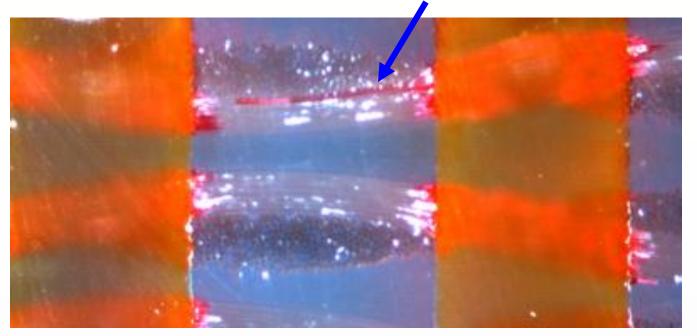

Hole to Hole dye path

#### 0.30mm spacing, C-H-DICY

#### 0.40mm spacing, D-H-DICY

The glass adjacent to outer layer is prone to form dye path, which should be induced by mechanical stress of drilling.

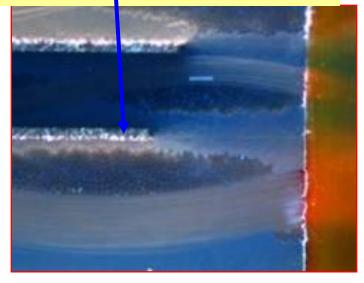

#### Hole to Hole dye path

#### Hole-to-hole spacing 0.30mm (B-H-DICY)

C Printed Circuits Eqpo<sup>®</sup>, APEX<sup>®</sup> and the Designers Summit 2008

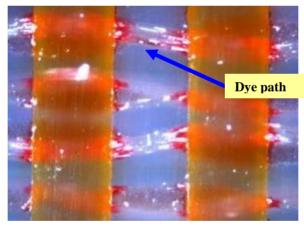

Hole to Hole dye path

Hole-to-hole spacing 0.30mm (C-H-DICY)

IPC Printed Circuits Expo<sup>®</sup>, APEX<sup>®</sup> and the Designers Summit 2008

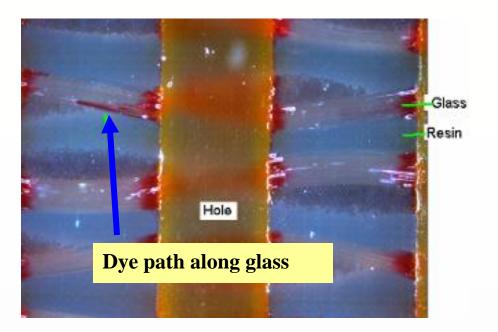

Hole to Hole dye path

Dye path along glass

hole-to-hole spacing 0.30mm(D-H-DICY)

C Printed Circuits Eqpo<sup>®</sup>, APEX<sup>®</sup> and the Designers Summit 2008

#### Hole to Hole dye path

#### hole-to-hole spacing 0.40mm

PC Printed Circuits Expo<sup>®</sup>, APEX<sup>®</sup> and the Designers Summit 2008

Hole to Hole dye path

PC Printed Circuits Expo<sup>®</sup>, APEX<sup>®</sup> and the Designers Summit 2008

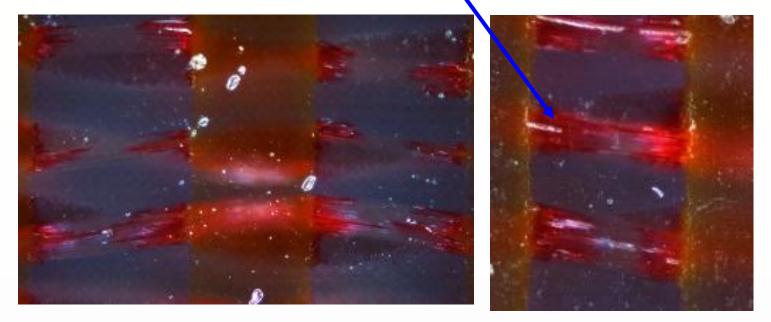

#### Hole to Hole dye path

hole-to-hole spacing 0.30mm(A-M-DICY)

C Printed Circuits Expo<sup>®</sup>, APEX<sup>®</sup> and the Designers Summit 2008

Hole to Hole dye path

Copper short were found between plated through holes for A-M-PN

The dye path formation is due to laminate void between holes.

Printed Circuits Eqpo<sup>®</sup>, APEX<sup>®</sup> and the Designers Summit 2008

Hole to hole dye path inspection result:

1) When the drill to drill spacing is down to 0.30mm, it's easy to form dye path along glass for DICY laminates, also 0.40mm drill to drill spacing has obvious dye path for some DICY laminates, but the PN laminate shows better bonding strength between resin and glass, and no dye path along glass is detected.

2) The PN curing agent laminate (A-M-PN) with filler has many laminate voids, the dye path is formed by the lamination voids, not along the glass.

#### Hole to copper dye path:

#### **Resin between copper and glass**

Inspection result: Fully dye path from hole to inner copper is not found.

C Printed Circuits Eqpo<sup>®</sup>, APEX<sup>®</sup> and the Designers Summit 2008

The effect of PCB fabrication parameter

Use DOE to test the effect of fabrication parameter as follows:

| Factor | Lamination  | Drill parameter  | Drill bit        | Desmear |

|--------|-------------|------------------|------------------|---------|

| 1      | 190°C 60min | Normal Chip load | New drill bit    | 1 time  |

| 0      | 180°C 40min | Lower chip load  | Re-sharp 3 times | 2 times |

The tested laminate is High Tg FR4 with DICY curing (C-H-DICY).

The effect of PCB fabrication parameter

Dye path (0.30mm spacing)

The re-sharp 3 times drill bit will cause long wicking, when hole-to-hole spacing is lower to 0.30mm, the long wicking can induce obvious CAF path.

C Printed Circuits Equo", APEX<sup>®</sup> and the Designers Summit 2008

Test Condition:

- 1) Precondition:

- a) Do conformal coating for test vehicles to avoid SIR failure

- b) Lead-free reflow 3 times

- 2) Environment chamber: 85% RH and 85°C

- 3) Test voltage: both bias and test voltage to be set as 100V

- 4) Insulation resistance monitor: online

- 5) Test time: 240hours at least

#### **Insulation Resistance Test**

Insulation Resistance: A-M-PB>B-H-DICY≈C-H-DICY ≈D-H-DICY

C Printed Circuits Expo<sup>®</sup>, APEX<sup>®</sup> and the Designers Summit 2008

Insulation Resistance Test Result:

For most test vehicles with DICY laminates, the insulation resistance of 0.30mm drill-to-drill spacing drops below 10^5 ohms within 48hours, on some coupons of 0.40mm drill-to-drill spacing also can't pass the 240hours test, by contraries, the test vehicles with PN material show high insulation resistance within 240hours tests, also the hole to inner copper keeps high insulation resistance within 240hours.

26

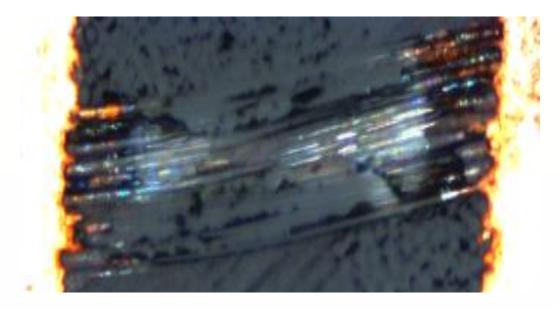

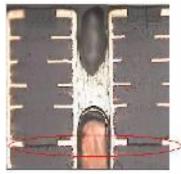

#### Failure analysis

**Dicy curing FR4**

From cross section, long wicking along glass had been found between holes with low insulation resistance.

# Content

- The risk of High density PCB

- CAF Risk

- Laminate crack

- Summary

IPC Printed Circuits Expo<sup>®</sup>, APEX<sup>®</sup> and the Designers Summit 2008

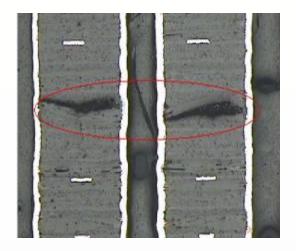

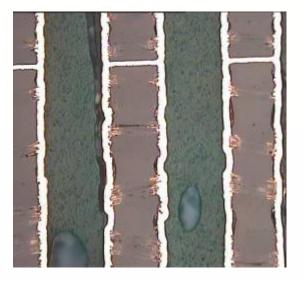

Laminate crack has been the bottleneck of high density design. By means of experiment and failure analysis, it is found that laminate crack often occurred between narrow holes.

C Printed Circuits Expo<sup>®</sup>, APEX<sup>®</sup> and the Designers Summit 2008

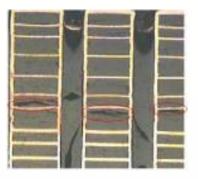

The PN High Tg FR4 with filler has better thermal resistance in thermal tress test.

PN High Tg FR4 A with filler (8mil hole spacing)

DICY High Tg FR4 B without filler (30mil hole spacing)

C Printed Circuits Expo<sup>®</sup>, APEX<sup>®</sup> and the Designers Summit 2008

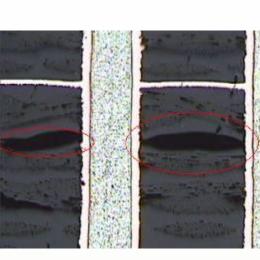

Via plugging is helpful to reduce the laminate crack.

8mil hole spacing with solder mask plugging

8mil hole spacing without solder mask plugging

PC Printed Circuits Expo<sup>®</sup>, APEX<sup>®</sup> and the Designers Summit 2008

The laminate crack possibility (different pad design):

whole copper > isolate pad ≈ thermal pad > non pad

Vias direct copper contact

Vias with thermal pads

#### Vias with isolated pads

#### Vias without pads

rcuits Expo<sup>®</sup>, APEX<sup>®</sup> and the Designers Summit 2008

IPC

Laminate crack summary:

1) In general closer hole spacing and thicker board have higher risk of laminate crack.

2) The PN FR4 with low CTE and high Td has better thermal resistance, and it can reduce laminate crack risk.

3) Via plugging can block thermal transport and reduce laminate crack risk.

4) The laminate crack is related the pattern design, the laminate crack possibility: whole copper > isolate pad  $\approx$  thermal pad > non pad.

# Content

- The risk of High density PCB

- CAF Risk

- Laminate crack

- Summary

IPC Printed Circuits Expo<sup>®</sup>, APEX<sup>®</sup> and the Designers Summit 2008

# Summary

- Using dye method can inspect the laminate damage easily during PCB fabrication, we can define the CAF risk via dye path formation, also dye method shows the wicking effect for improving the drill quality or making laminate selection.

- In general the PN curing agent FR4 shows better anti-CAF performance than DICY curing agent FR4, but may induce lamination void issue, and PCB fabricator should adjust lamination parameter to avoid lamination void.

- If the drill-to-drill spacing is lower to 0.40mm, it is possible to avoid the CAF risk, but it is also necessary to select proper laminates, and make some adjustment on PCB fabrication.

- When hole pitch is less than1.0mm, laminate selection is critical and via plugging is necessary to avoid CAF and laminate crack.

inted Circuits Expo<sup>®</sup>, APEX<sup>®</sup> and the Designers Summit 2008