#### A Case for Multiple Sheet Resistivities for Thin Film Embedded Resistor Packaging Applications

Rocky Hilburn, Craig Hasegawa and Jiangtao Wang Ph.D. Ticer Technologies 2555 W. Fairview St. Chandler, Arizona 85224

#### Abstract

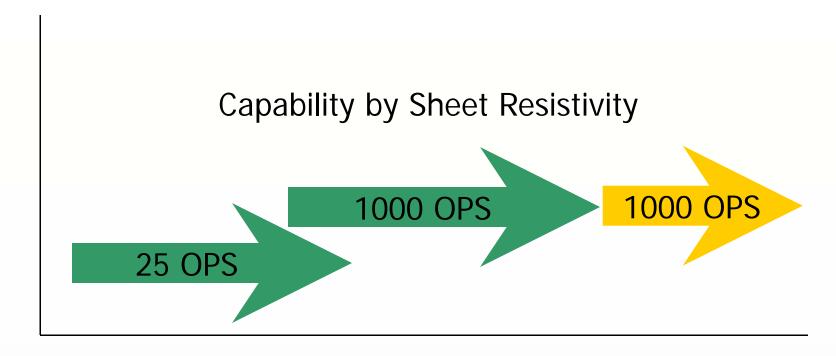

Designers of high performance electronics continue to have system requirements that necessitate the implementation of embedded resistors in microelectronic package and multilayer printed circuit applications. The reasons most commonly given for this shift in technology are performance enabling, reduction in form factor, and relief from routing complexity. The advantages realized with embedded resistors make a strong case for implementation in both new and legacy designs. Until recently, thin film resistors with a maximum sheet resistivity of 250 ohms/square were available. This constrained the practical limit of resistor values to about 10k ohms for small form factor packages and limited resistor footprint. The advent of a robust 1000 ohm/square thin film resistor has allowed designers to expand their range of resistors values that can easily be captured and still maintain a reasonable resistor form factor. Values to 100k ohms and greater are reachable, and when 1000 ohm/square and lower ohm/square materials are used together in multilayer packages, the resistor capture capability can reach into the 90+ percentage.

In this paper, an actual case, the use of multiple sheet resistivities and their practical use, will be discussed. Low ohm/square material, i.e. 10 or 25 OPS, used in combination with the 1000 OPS will be compared to a Bill of Materials with terminating and pull-up/down and the capture potential. The introduction of a 1000 ohm/square thin film embedded resistor material for this and other applications will also be covered.

#### Introduction

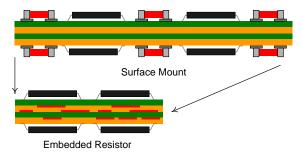

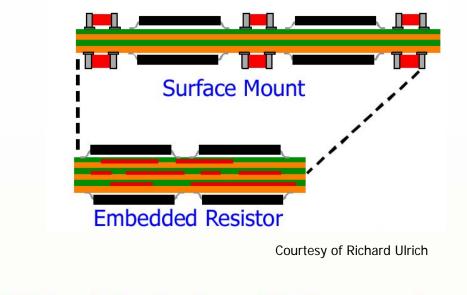

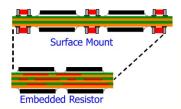

The need for increase functionality with smaller form factors in electronic devices continues to drive the development of electronic systems with passive components embedded in multilayer PCBs. Figure 1 shows the replacement of SMT components with embedded passives integrated into the printed circuit board.

To ensure high performance devices perform equal to or better than designs with SMT components the embedded resistors must achieve a specified value and a tolerance that enables the PCB design to meet electrical timing and circuit signal quality. Including embedded resistor in printed circuit designs allows the resistors to be placed more optimally in the circuit. The number of surface mounted resistors can be reduced, typically improving escape routing, and allows more outerlayer area to be used for active devices. This also frees top-side board area for adding functionality, optimizes the component placement and lowers overall system inductance. Embedded passives, in general, yield a more reliable printed circuit board by reducing the number of solder joints, reduce rework on the assembly, and lowers total system cost.

Figure 1: Reduced form factor with embedded resistor

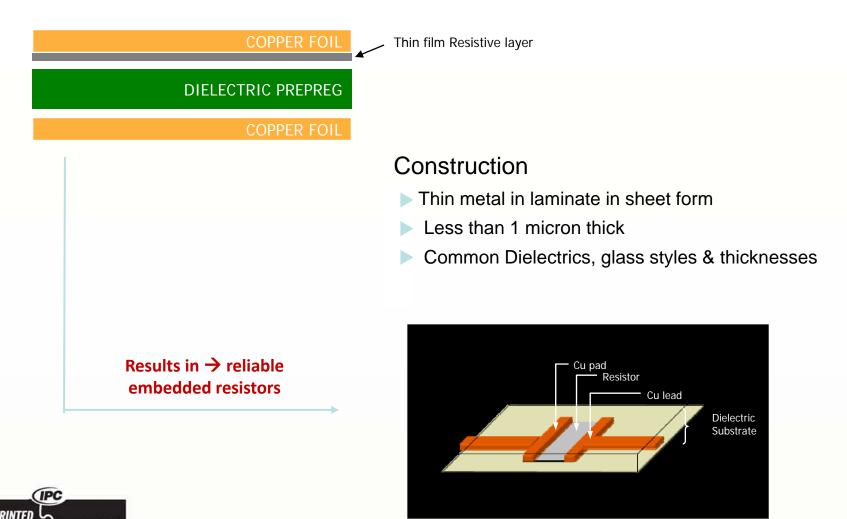

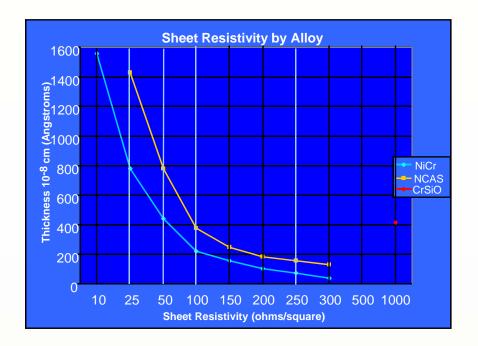

TCR® is an integrated thin film resistor foil for embedded resistor applications. It can consist of standard and low profile copper foil with a thin layer of resistive alloy (NiCr, NCAS or CrSiO) sputtered onto the matte side of the copper. When this material is patterned appropriately, the resistive layer serves as the embedded resistor element. Both NiCr and CrSiO alloys possess high electrical resistivity, low parasitics, high thermal stability, and low temperature coefficients of resistivity in the range of -20 to 300 ppm/C<sup>o</sup> [1].

The base copper foil is typically low profile and the surface topography is isotropic. A uniform resistive layer on low profile copper foil enhances not only the fabrication of resistors with tight tolerances but also has improved transmission loss properties when compared to standard electrodeposited copper foil [2].

Design and manufacturing of PCBs with embedded resistors, especially multiple sheet resistivities and multiple layers of buried resistors, can be challenging. These processes are further challenged by PCB technologies like HDI that typically go hand-in-hand with embedded passives. A critical analysis of the PCB Bill of Materials is fundamental to the determination of maximum resistor capture, optimization of embedded resistor utilization and implementation in the design. A good understanding of the finished assembly's electrical and mechanical requirements and available embedded passive materials is necessary for a successful implementation on new designs and legacy re-designs.

In this paper a case showing the methods and results of re-designing a legacy assembly is shown with actual goals and outcomes presented.

#### **Resistance Primer**

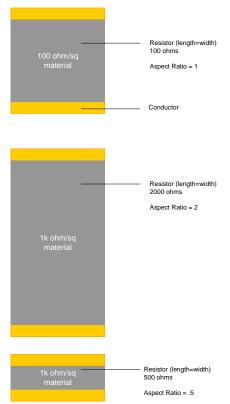

All resistor materials are provided with resistance values expressed in ohms per square. R = pL/A R is resistance in ohms, p is the resistivity of the material, L is the length and A is the cross sectional area (i.e., thickness times width). When thickness is held constant then R is the same for any square area, hence the expression ohms/square. Resistance then can be varied by varying the aspect ratio of the area (L/W), as illustrated in Figure 2 [3].

The ability to control the resistor value by adjusting the aspect ratio of the resistor element is integral in the analysis and design with multiple sheet resistivities. Resistor form factors can be optimized based on value, tolerance, routing limitations and physical area.

Figure 2: Sheet Resistance Relationships

#### **Technology Overview**

A low to medium volume legacy assembly was chosen for the redesign with embedded resistor and capacitive materials. The assembly was selected based on the primary goal to reduce the PCB area by a minimum of 20%. Assembly redesign was expected to be cost neutral and therefore the capture analysis was set to maximize the number of SMT resistors replaced.

The discussion in this paper is principally on the embedded resistor details of the analysis and design. The primary goals of the project were to produce a smaller form factor assembly and reduce weight. The smaller PCB size would allow better

panel utilization resulting in higher panel and part yield. Another design goal was to decrease the complexity of routing in the PCB.

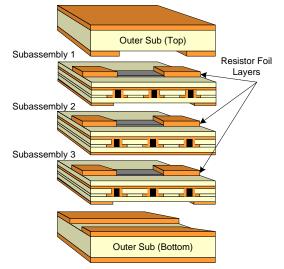

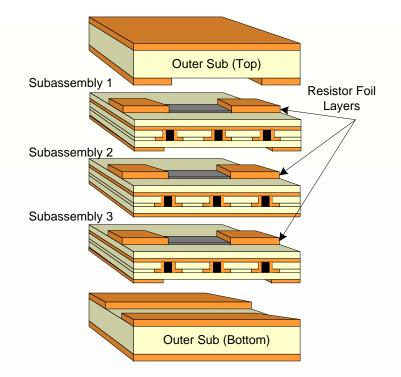

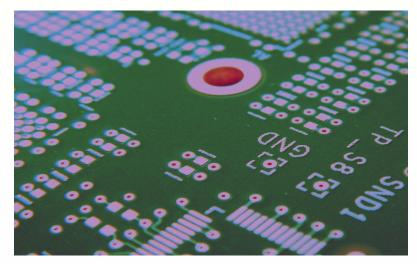

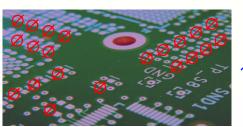

The PCB was a stacked microvia with 14+ layers and multiple subassemblies. The construction was high performance epoxy dielectrics with ½ ounce copper construction throughout the subassemblies and outers to meet the controlled impedance requirements. Lines and spaces minimums were 100 micron. Microvias from n-1 and n-2 resulted in the plating aspect ratio of the microvia greater than standard technology. Figure 3 shows an example of the PCB construction [4].

TCR® thin film resistor technology was chosen for the analysis, design and manufacturing of the PCB. The product line has a sheet resistivity range from 10 to 1000 ohms per square (OPS). The different alloys of NiCr and CrSiO, spanning two decades of resistivity, allowed the maximum resistor capture during the BOM analysis. Thin film resistor technology was chosen over other embedded resistor technologies like polymer thick film because of its post-assembly reliability, electrical performance, design flexibility and established printed circuit manufacturing knowledge.

Figure 3: Stack up of multilayer PCB with subassemblies and multiple embedded resistor layers

#### **Bill of Material Analysis**

The BOM for the PCB assembly was pulled out of the assembly design package. The resistors were segregated from the rest of the components and were placed in a separate database. The resistor value, tolerance, power, component ID, size, and placement coordinates were contained in the database to aid in the capture analysis. Resistor values ranged from 10 ohms to 1 MegOhm with resistor tolerance typically at +/-5%. Some resistors had 1% tolerance. These resistors were noted and evaluated by the electrical designers for their tolerance requirements.

The total number of resistors in the assembly was greater than 450. The resistor density was approximately 3 resistors per  $cm^2$ .

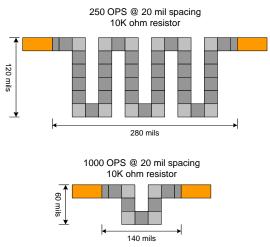

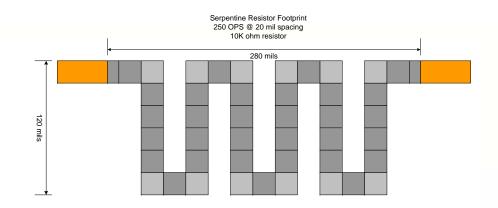

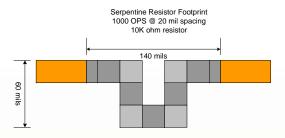

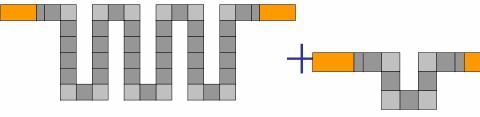

A resistor assessment calculator was used to evaluate the resistors values to select the capture candidates. The calculator uses algorithms based on resistor alloy and sheet resistivity to evaluate the resistor value, power requirements and tolerance. The calculator then provides a baseline for the resistor dimensions and footprint for the resistor based on the sheet resistivity. An example of the output from the resistor calculator is shown in Figure 4. The calculator also outputs the configuration of the resistor based on the recommended dimensions. The configurations output are partial square, bar and serpentine. The configuration and footprint of resistors can be optimized with the selection of the proper sheet resistivity for particular resistor values as shown in Figure 5. In the example a 10k ohm resistor is shown in two serpentine configurations based on 250 and 1000 OPS materials. The footprint of the resistor designed with 1000 OPS material is 75% smaller than the designed with 250 OPS material. This can be critical for higher resistor values with routing constraints.

| Step 1: Inputs        | Inputs         |                   |      |                       |                |  |  |  |

|-----------------------|----------------|-------------------|------|-----------------------|----------------|--|--|--|

|                       | Resi           | stor <sub>1</sub> |      | Resistor <sub>2</sub> |                |  |  |  |

| Resistor Value (Ohms) | 1              | 0                 | 1000 |                       |                |  |  |  |

| Power Dissipation     |                |                   | İ    |                       |                |  |  |  |

| (mWatts)              | 6              | 0                 |      | 60                    |                |  |  |  |

| Tolerance (%)         | 1              | .0                |      | 10                    |                |  |  |  |

| Step 2: Analysis      | Recor          | nmendeo           | 11   | Dimens                | ions           |  |  |  |

|                       | Resi           | stor <sub>1</sub> |      | Resistor <sub>2</sub> |                |  |  |  |

| Sheet Resistivity     | $W_1$          | L <sub>1</sub>    |      | W <sub>2</sub>        | L <sub>2</sub> |  |  |  |

| Ohms/Square (OPS)     | (m             | m)                |      | (т                    | m)             |  |  |  |

| 10                    | 0.5            | 0.5               |      | 0.3                   | 30.0           |  |  |  |

| 25                    | 0.9            | 0.3               |      | 0.3                   | 10.2           |  |  |  |

| 50                    | 1.5            | 0.3               |      | 0.3                   | 5.2            |  |  |  |

| 100                   | 2.7            | 0.3               |      | 0.3                   | 2.7            |  |  |  |

| 250                   | 6.5            | 0.3               | 1    | 0.3                   | 1.2            |  |  |  |

| 1000                  | 25.2           | 0.3               |      | 0.5                   | 0.5            |  |  |  |

|                       | Configuration  |                   |      |                       |                |  |  |  |

|                       | Resi           | stor <sub>1</sub> |      | Resistor <sub>2</sub> |                |  |  |  |

| 10                    | Squ            | lare              |      | Serpentine            |                |  |  |  |

| 25                    | Partial        | Square            |      | Serpentine            |                |  |  |  |

| 50                    |                | Square            |      | Bar                   |                |  |  |  |

| 100                   | Partial Square |                   |      | Bar                   |                |  |  |  |

| 250                   | Partial Square |                   |      | Bar                   |                |  |  |  |

| 1000                  | Partial        | Square            |      | Square                |                |  |  |  |

Figure 4: Resistor Calculator with Analysis

Figure 5: Footprint Comparison 10k ohm serpentine resistors

#### **Resistor Capture with Multiple Sheet Resistivities**

The resistor calculator provided a good analysis and established the need for multiple sheet resistivities in the design in order to maximize resistor capture and minimize resistor element footprints for higher value resistors. Determining the number of resistors by resistivity value groups confirmed the need and the drill-down showed the terminating and pull-up/down resistor sets of the BOM.

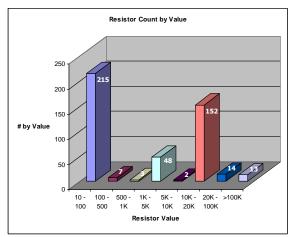

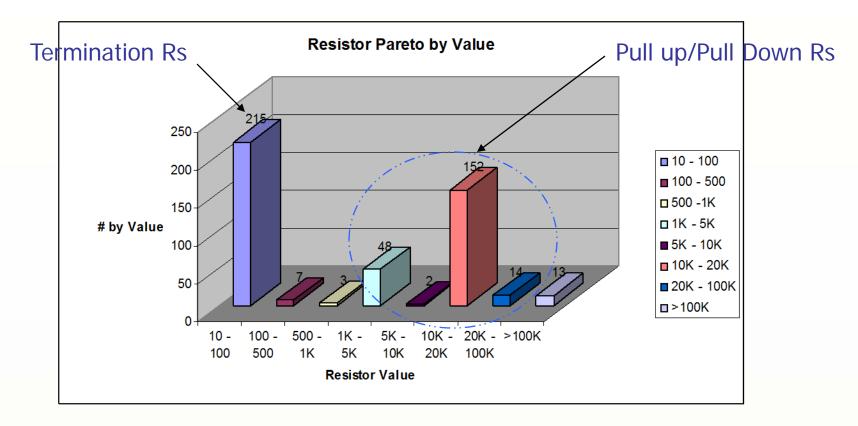

The resistor BOM contained mostly termination and pull-up/pull-down resistors. The termination resistors had values in the 10 to 100 ohm range and the pull-up/pull-down resistor values from 1k to 100k ohms. The capturing of the 1k to 100k ohm resistors was essential to maximizing the embedded count. The breakdown of the BOM by resistor values is shown is Figure 6.

With the results from the resistor calculator and the resistor value breakdown the next task was to determine optimum sheet resistivity pairings. Multiple scenarios using different pairings were compared based on capture percentage, optimum embedded resistor pattern size and finished tolerance. The following scenarios were evaluated:

- 10 and 250 OPS

- 10 and 1000 OPS

- 25 and 250 OPS

- 25 and 1000 OPS

The pairing of 25 and 1000 OPS materials was determined to be the best fit for the design parameters and manufacturing of the PCB. The use of these materials gave a resistor capture percentage of greater than 90% and providing a path to achieving the 20% PCB size reduction. In comparison, the 10 and 250 OPS pairing resulted in only a 56% SMT capture. This was greatly due to the 250 OPS material choice capturing resistor up to app. 7k ohms and still maintaining a reasonable resistor footprint.

Figure 6: BOM Resistor Count by Value

#### **Model Results**

Thin film embedded resistor materials were chosen to reduce or eliminate the constraints of standard surface mount components of the PCB assembly.

The PCB assembly was selected based on the need to reduce its form factor, weight and increase manufacturing and end product yields. The project was a re-design of a medium layer count, HDI PCB with multiple subassemblies. The PCB manufacturing was challenged with incorporating both embedded resistor and planar capacitor in the subassemblies, higher than standard technology HDI plating and process sequencing changes required by the embedded passives.

The recommendation of the optimal material sets required a detailed study of the assembly bill of materials and the resistor calculator tool. The resistor calculator gave the ability to visualize the recommended dimensions and configuration of the embedded resistor elements based on the resistor value, resistor tolerance, power requirements and sheet resistivity of the different materials. The resistor BOM analysis allowed identification of the resistor capture candidates and showed the need for multiple sheet resistivities in the PCB.

#### Conclusions

A case for implementing multiple thin film resistor sheet resistivities into a printed circuit re-design was presented. The thin film embedded resistor in the printed circuit is an excellent alternative to the SMT resistors for ease of assembly and it delivers advantages when the PCB form factor must be reduced. The availability and performance of a 1000 ohm per square thin film resistor material significantly enlarged the range of SMT capture.

This project's primary goal was PCB size reduction and was achieved by freeing additional top-side surface area. The smaller PCB form factor increased panel utilization by approximately 20%. High SMT component elimination was accomplished when it was determined 90% of the SMT resistors were good candidates for embedding when using 25 and 1000 OPS sheet resistivity layers. The reduction in PCB size and elimination of the SMT components reduced the assembly weight by the 20% of the original PCB weight. Additional decrease in assembly weight resulted from reduction in solder, component and plated vias. A weight increase due to the layers added in the PCB redesign is expected. The total weight change is expected to be lower in the final analysis. Last, the additional layers and circuit re-routing with small, integrated resistor elements reduced the complexity of the board.

#### **Future Work**

The project is currently in the assembly and testing phase thus the goals related to performance and reliability are yet to be determined. Once these phases are complete the information will be provided.

#### References

- 1. "TCR, TCR copper foil with integrated thin film resistor data sheet," Internet: http://www.ticertechnologies.com/tech\_lit.html.

- 2. G. Brist, S. Hall, S. Clouser, T. Liang, "Non-Classical Conductor Losses due to Copper Foil Roughness and Treatment", Electronic Circuits World Convention 10, Anaheim, February, 2005; S19-2.

- 3. R. Hilburn, J, Wang, D. Parson, S. Zhang, "Thin Film Embedded Resistor Processing in Sequential Lamination Printed Circuit Manufacturing", IPC Printed Circuits Expo, Los Angeles, CA, February, 2007.

- 4. R. Snogren, "Designing Embedded Resistors and Capacitors", IPC Printed Circuits Expo, Anaheim, CA, February, 2004.

#### A Case for Multiple Sheet Resistivities for Thin Film Embedded Resistor Packaging Applications

# Agenda

- Company Profile

- Business Case Introduction

- Project Requirements and Goals

- Embedded Resistor Calculator Example

- Bill of Material Analysis

- Project Findings & Lessons Learned

- Summary

## **Executive Summary**

- Re-designed and delivered legacy product incorporating TCR® thin film embedded resistor materials

- Used 25 and 1000 ohms/square (OPS) sheet resistivities to achieve 90% reduction in SMT resistors

- Achieved 20% PWB form factor reduction

- PWB in assembly fabrication

- Performance against legacy expected to show improvement while total system cost expected to be neutral or better

# **Company Information**

#### History of TCR and Ticer Technologies

- 1980's Gould Electronics researches ED resistor films

- 1997 Gould develops vacuum deposited thin film resistor

- 1999 Patents granted

- 6 patents

- 2001 Commercialization of TCR® thin film resistor

- 25, 50, 100 and 250 OPS thin film resistor foils

- 2002 Global market development

- 2006 Ticer Technologies spun off from Gould, exclusive license from Nippon Metals and Mining for N.A.

- 2007 Ticer introduces 1000 OPS material to market

### **Ticer Technologies**

Ticer Technologies 2555 West Fairview Street Chandler, Arizona USA

- New 8,700 sq. ft. manufacturing facility in Chandler, AZ.

- Manufacturing and Applications Laboratory on-site.

### **Business Case**

### Description

Take an existing *legacy* assembly and re-spin the PCB design to incorporate embedded resistors so overall form factor is reduced.

### Requirements

- PCB size reduction 20% minimum

- Total assembly cost neutral on first re-spin

- Additional layers could be added but kept to a minimum

- Thickness to remain the same

- Impedance adjustments minimal

- Maximize % of resistors captured

- 3 month project time for initial samples through contract manufacturing and ready for burn-in test

### Goals

- Smaller form factor

- Reduced weight

- Equal or better performance

- Equal or less complexity of routing of PCB

- Higher yields through assembly

- Higher panel yields through better utilization

- Higher part yield

# PCB Technology

- 14+ layer multilayer

- Multiple subassemblies

- Stacked microvia

- Higher than standard plating aspect ratio on microvias

- 4 mil tracks and gaps

- Impedance controlled

- High performance

dielectrics

- All ½ oz. copper construction

IPC

APEX

GNERS SUMMIT

### **Resistor Example**

### Laminate with TCR Details

IPC Printed Circuits Expo<sup>®</sup>, APEX<sup>®</sup> and the Designers Summit 2008

and the DESIGNERS SUMN

# TCR<sup>®</sup> Thin Film Resistor Technology

- Technology: Vacuum

Metallization onto copper foil

- Sheet resistivities 10, 25, 50, 100, 250, 1000 OPS

- Tolerance, Material: +/- 5%

- Copper Weights: <sup>1</sup>/<sub>2</sub> and 1 oz.

- Copper Grade: 3

### Bill of Material Analysis

### **Bill of Materials**

- BOM included mostly terminating and pull-up/pull-down resistors

- Total # resistors >450

- Resistor density: approximately 3 resistors/cm<sup>2</sup>

- Resistor values from 10 ohms to 1 MegOhm

- Resistor tolerances typically +/-5%

- Some critical resistors at 1%

#### BOM Review for Resistor Replacement

- BOM was evaluated for resistor embedding using Resistor Calculator

- Resistor Calculator provides baseline for resistor dimensions based on tolerance and power requirements

### **Resistor Calculator Example**

#### Ticer Resistive Foils TCR® Designer's Guide

Variables: Resistor Value, Power Dissipation, Tolerance, & Etch Tolerance Calculates: Baseline Resistor Width & Length

METRIC (microns)

#### A-Input Resistor Specifications (Table 1)

#### Step 1: For each resistor enter the resistor value (R) in ohms, its power dissipations (P) in mWatts, and the maximum allowable tolerance (9) in percentage (%). Note: Tolerances below 5% will output a value less than the TCR<sup>®</sup> material tolerance.

|                            | Table 1        |     |                |  |                |  |                |  |                |  |                |

|----------------------------|----------------|-----|----------------|--|----------------|--|----------------|--|----------------|--|----------------|

|                            | R <sub>1</sub> | n j | R <sub>2</sub> |  | R <sub>3</sub> |  | R <sub>4</sub> |  | R <sub>5</sub> |  | R <sub>6</sub> |

| Resistor Value (Ohms)      | 100            |     | 1000           |  | 10000          |  | 15000          |  | 67000          |  | 100000         |

| Power Dissipation (mWatts) | 60             | 1   | 60             |  | 60             |  | 60             |  | 60             |  | 60             |

| Tolerance (%)              | 10             | . ( | 10             |  | 10             |  | 15             |  | 15             |  | 20             |

#### B-Input Width and Length Etch Tolerances. Available from PWB Fabricator. (Table 2)

#### Step 2 Width and Length Etch Tolerances (E) based on PWB fabricator data is input. Note: Default value = 12.7 um for 1/2 oz. copper

| Table 2               |        |  |  |  |  |  |  |

|-----------------------|--------|--|--|--|--|--|--|

|                       | E (um) |  |  |  |  |  |  |

| Width Etch Tolerance  | 12.7   |  |  |  |  |  |  |

| Length Etch Tolerance | 12.7   |  |  |  |  |  |  |

#### C-Recoumended Length (L) and Width (W) of resistors by corresponding sheet resistivity (Table 3)

#### Step 3: Length and Width of the resistors are calculated for the different sheet resistivities. Review for acceptability for each sheet resistivity against design rules

|                   |      |      |            |     |         |    | Ta   | de 3  |            |      |       |            |      |        |            |             |        |

|-------------------|------|------|------------|-----|---------|----|------|-------|------------|------|-------|------------|------|--------|------------|-------------|--------|

| Sheet Resistivity | R    | 1    |            | 1   | R2 R3 R |    | R4   |       |            | R5   |       | R5         |      |        | 1          | R6          |        |

| Sheet Resistivity | W1   | L1   |            | W2  | L2      |    | W3   | L3    |            | W4   | L4    |            | W5   | L5     |            | W6          | L6     |

| Ohms/Square (OPS) | (U.  | m)   | -          | (u  | m)      |    | (um) |       |            | (um) |       |            | (um) |        | 4          | <i>(um)</i> |        |

| 25                | 311  | 1245 | t*         | 255 | 10210   | t* | 250  | 99857 | t*         | 126  | 75571 | t*         | 126  | 337116 | <i>t</i> * | 84          | 336508 |

| 50                | 374  | 747  | <i>t</i> * | 261 | 5229    | t* | 250  | 50053 | t*         | 126  | 37849 | t*         | 126  | 168621 | t*         | 84          | 168296 |

| 100               | 531  | 581  | p*         | 274 | 2739    | t* | 252  | 25151 | t*         | 127  | 18987 | t*         | 126  | 84373  | t*         | 84          | 84190  |

| 250               | 872  | 349  | <i>t</i> * | 311 | 1245    | t* | 255  | 10210 | t*         | 128  | 7670  | <i>t</i> * | 126  | 33825  | t*         | 84          | 33726  |

| 1000              | 2739 | 274  | <i>t</i> * | 498 | 498     | t* | 274  | 2739  | <i>t</i> * | 134  | 2012  | <i>t</i> * | 128  | 8551   | <i>t</i> * | 85          | 8495   |

\*L and W are constrained by power dissipation (P) or tolerance (d) requirements

#### **Resistor Calculator – Resistor** Footprints Recommended resistor configuration (Table 3)

Step 3: Resistor patterns are configured to optimize the footprint of the resistor based on sheet resistivity, resistor length and width

| Sheet Resistivity |                |                |

|-------------------|----------------|----------------|

| Ohms/Square (OPS) | R 1            | R 2            |

| 25                | Partial Square | Bar            |

| 50                | Partial Square | Partial Square |

| 100               | Partial Square | Partial Square |

| 250               | Partial Square | Partial Square |

| 1000              | Partial Square | Partial Square |

### **Resistor Pareto**

## Analysis of Resistor Pareto

- Multiple sheet resistivities required for maximizing resistor replacement

- Multiple scenarios would be suitable for covering resistance range

- 10 and 250 OPS

- 10 and 1000 OPS

- 25 and 250 OPS

- 25 and 1000 OPS

- 25 and 1000 OPS scenario selected for optimized resistor footprint and capture percentage

### Analysis of Resistor Pareto - 2

#### 10 100 300 500 10K 70k 1Megohm Resistor Value

### Project Findings & Lessons Learned

## PCB Re-Design

- Software capable of handling algorithms for resistor design

- Output of Gerber must be retain intelligence for outputting artwork and electrical test files

- Designers must understand embedded resistor capability and routing

**Courtesy of Mentor Graphics**

### **PCB** Fabrication

- Fabricator must be capable of all processes for the board build

- Embedded resistor not seen as the most difficult aspect of the build

### Summary

# Summary - 1

Smaller form factor of PCB would increase panels utilization by app. 20%

Size reduction could be accomplished by freeing additional surface area

Embedded resistor scenario of 25 and 1000 OPS captured app. 90% of SMT resistors

Implementation of embedded resistor could be cost neutral on initial design spin

## Summary - 2

- Assembly DPMO would drop due to elimination of 0201 SMT resistors

- Adherence to timeline Re-spin and PCB build finished behind schedule

- Performance differences TBD

- Reliability TBD

- Recommendation of handling PCBs with embedded resistor as ESD components to be implemented

- Better solutions available if this were a new design not a re-spin

### Acknowledgements

Ticer Technologies - Dr. Jiangtao Wang Ph.D. & Craig Hasegawa.

### **Contact Information**

Rocky Hilburn

Director, Technical Marketing Ticer Technologies 2555 W. Fairview St. Suite 101 Chandler, Arizona USA 85224 480.223.0892 (o) 480.205.1351 (m) 480.782.1720 (f) rhilburn@ticertechnologies.com