### The Universal PCB Design Grid System

### **Tom Hausherr, Valor Computerized Systems**

#### Abstract:

Mixing PCB Design Layout units will compromise perfection every time. PCB Design perfection starts with building CAD library parts and quickly moves to part placement, via fanout and trace routing challenges. Outputting data for machine production can be extremely complex or very simple based on the PCB Design Layout units that were used throughout the PCB design process. This paper reviews one of the single most important, but sometimes overlooked or taken for granted, aspects of the electronics industry – The PCB Design Grid System

#### Introduction:

From the 1960's through the 80's the primary PCB design grid system used Imperial units. All PCB design features and grid layouts were in 0.001" (1 mil) increments and everything was symmetrical and evenly balanced. Then in 1988 the world standards organizations banded together to agree that the metric unit system was superior for solving PCB design development. The first signs of this transition started appearing in the 1990's in component manufacturer's datasheets and the JEDEC component packaging dimensional datasheets, which were once entirely based on Imperial "inch" units, where slowly converted to metric units.

IPC, a world standards organization, proposed a base value of 0.05mm for the "PCB Design Grid System". And the process of getting all features in the PCB design back "On-Grid" was started. However, this was met by great resistance in the USA. Some American PCB designers, manufacturing companies, mechanical engineers and EE engineers are still fighting the transition process.

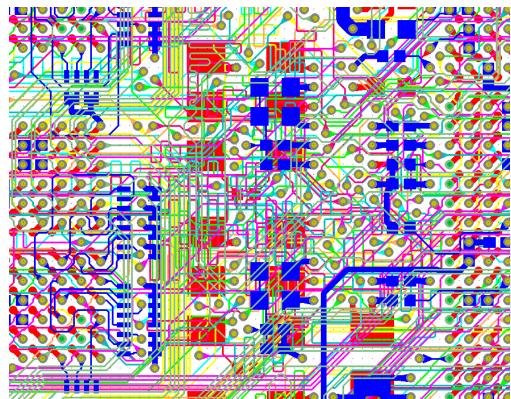

The transition from one unit system to another introduced chaos in the PCB design industry because PCB designers were forced into using two different unit systems during the transition period. The CAD vendor's way of coping with the transition was to introduce a "Gridless Shape Based" auto-routing feature that provided the PCB designer a solution for working with both metric and imperial unit pin pitched land patterns. New technical terms were introduced like "Off-Grid" or "Gridless" and "Shape Based" routing solutions. This concept was entirely based on the fact that PCB design rules are the primary factor and the PCB designer's objective goal was to adhere to the rules regardless of how irregular the land pattern features were. Some CAD library parts have an inch based pin pitch and some have a metric pin pitch. The PCB design grid system was chaotic and working in a gridless environment presented new challenges for PCB designers.

The main impact of the gridless system for PCB layout is the fact that trace routing computations is so granular that it consumes far more memory and CPU processing. The gridless system has tens of thousands of additional options to commutate and actually slows the auto-routing tools down. It also makes it extremely difficult to cleanly manually route traces in-between the center of two component leads or vias.

The "Universal PCB Design Grid System" impacts everything from CAD library creation, part placement, via fanout to trace routing while at the same time consuming far less computer memory and CPU processing. It also centers traces between pins and vias increasing manufacturing yields. It also improves the overall aesthetic look of the part placement and trace routing.

The ultimate goal for IPC Standards and designing a perfect PCB is to have all element feature sizes in the PCB design rounded off in 0.05 mm increments and snapped to a 0.05mm grid system. This paper will prove beyond any doubt that this is the ultimate solution. Note: 0.05mm = 0.0019685" or almost 2 mils

The following pages explain the criteria needed to follow "The Universal PCB Design Grid System" and to learn how advanced this system really is. But first, let's meet the key players whose goal is to standardize the electronics product development industry.

#### **Electronic Standard Organizations:**

Standard component package outlines come from industry standard organizations that specialize in component packaging data and standardization of documents and publications.

Standards organizations descriptions -

- JEDEC Joint Electron Device Engineering Council The semiconductor's engineering standardization body that represents all areas of the electronics industry, including discrete component and integrated circuit packaging standards.

- **EIA** Electronic Industries Alliance

A national trade organization that includes the full spectrum of U.S. manufacturers for tape and reel, tray and tube component, packaging standards. The EIA-481-D-2008 publication is the most recent.

- IEC International Electro technical Commission IEC is the leading global organization that prepares and publishes international standards for all electrical, electronic and related technologies as well as associated general disciplines such as terminology and symbols.

- **NIST** National Institute of Standards and Technology From atomic clocks to semiconductors, innumerable products and services rely in some way by NIST. NIST's mission is to develop and promote measurement, standards, and technology to enhance productivity, facilitate trade, and improve the quality of life.

- IPC Association Connecting Electronics Industries IPC is the only trade association that brings together all of the players in this industry: PCB designers, PCB manufacturers, PCB assembly companies, suppliers, and original equipment manufacturers.

- **ANSI** The American National Standards Institute ANSI's mission is to enhance both the global competitiveness of U.S. business and the U.S. quality of life by promoting and facilitating voluntary consensus standards and conformity assessment systems, and safeguarding their integrity.

- EIAJ Electronic Industries Association of Japan EIAJ's mission is to represent the domestic electronics industry in working on the challenges and issues it faces including programs planned and implemented with the cooperation of related organizations and associations worldwide.

- **NEMI** National Electronics Manufacturing Initiative NEMI is an industry-led consortium whose mission is to assure leadership of the global electronics manufacturing supply chain. With a membership that includes hundreds of electronic component manufacturers, suppliers, associations, government agencies and universities.

- JEITA Japan Electronics and Information Technology Industries Association

- JEITA is an industry organization in Japan with activities covering both the electronics and information technology (IT) fields. JEITA covers electronic components, radio and broadcasting equipment, computers, medical devices, measure and control systems and assemblies.

#### Land Pattern CAD Library Creation:

With guidance provided by these various standards organizations, PCB designers have built rules for creating consistent, quality land patterns in their CAD tools. In the ideal universal grid system, 0.05mm matches many elements. There are unique exceptions to these rules, but these are true most of the time.

Generic Sizes for all CAD Library Land Patterns for both SMT and PTH according to IPC -

- Outlines are in 0.05mm increments

- o Includes Silkscreen, Assembly and Placement Courtyard

- Pad Sizes are in 0.05mm increments

- Hole Sizes are in 0.05mm increments

- Polarity Markings are in 0.05mm increments

- Local Fiducials are in 0.05mm increments

- Reference Designator Height and Line Width are in 0.05mm increments

Ball Grid Array Standards for BGA Packages in the IPC-7351 standard -

- Ball and Land sizes are in 0.05mm increments (See Table 1)

- Pin pitches are on 0.05mm increments

- Package body outline dimensions are in 0.05mm increments

| Nominal Ball<br>Diameter | Reduction | Nominal Land<br>Diameter | Land Variation |  |

|--------------------------|-----------|--------------------------|----------------|--|

| 0.75                     | 25%       | 0.55                     | 0.60 - 0.50    |  |

| 0.60                     | 25%       | 0.45                     | 0.50 - 0.40    |  |

| 0.55                     | 25%       | 0.45                     | 0.50 - 0.40    |  |

| 0.50                     | 20%       | 0.40                     | 0.45 - 0.35    |  |

| 0.45                     | 20%       | 0.35                     | 0.40 - 0.30    |  |

| 0.40                     | 20%       | 0.30                     | 0.35 - 0.25    |  |

| 0.30                     | 20%       | 0.25                     | 0.25 - 0.20    |  |

| 0.25                     | 20%       | 0.20                     | 0.20 - 0.15    |  |

Table 1

Gull Wing Component Lead Standards for QFP, SOP and SOT Packages from JEDEC -

- Package body outline dimensions are in 0.05mm increments

- Package tolerances are in 0.05mm increments

- Terminal lead sizes are in 0.05mm increments

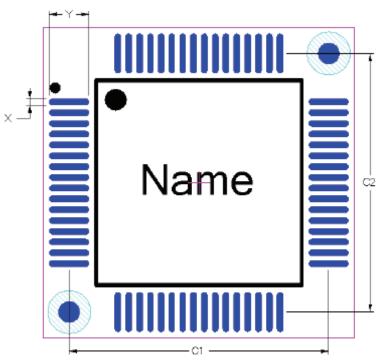

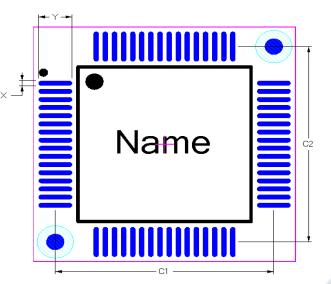

- Pin pitches, land size round-offs "X, Y" are on 0.05mm increments and land centers "C" are on 0.1mm increments. See Figure 1.

#### Figure 1

Chip Component Lead Standards for Resistor, Capacitor, Diode and Inductor Packages by EIA -

- Package body for outline length and width dimensions are in 0.05mm increments

- Terminal lead sizes are in 0.05mm increments

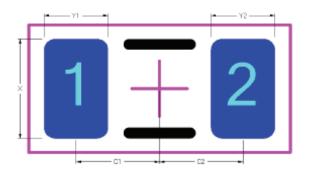

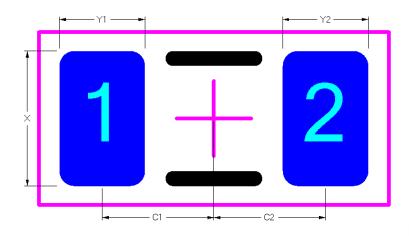

- Land size round-offs "X, Y" are on 0.05mm increments & land centers "C" are on 0.1mm increments

#### Figure 2

No-Lead Component Lead Standards for SON, QFN, DFN, SOTFL and SODFL by JEDEC -

- Pin pitches are on 0.05mm increments

- Package body outline dimensions are in 0.05mm increments (includes Height)

- Terminal lead sizes are in 0.05mm increments

- Package tolerances are in 0.05mm increments

The basic rule, in today's component package technology, is that most of the time component package dimensions and solder terminal leads are in 0.05mm increments. Of course the exceptions to this rule are all component packages that have been carried over from the 1980's time frame. In order for a complete transition to the metric system and full blown electronic product development automation is introduced, the Inch Based component packages would have to be eliminated.

#### Part Placement Grid System:

If you build your CAD library parts in millimeter units, the best placement grid rule is to use numbers that can be evenly divided into 1mm and are one place to the right of the decimal point. Optimized metric placement grids include: 1mm, 0.5mm, 0.2mm and 0.1mm. To achieve the best results, no other part placement grids should be used unless absolutely necessary like for a fixed connector or switch on the PCB edge.

#### Via Size and Fanout Grid System:

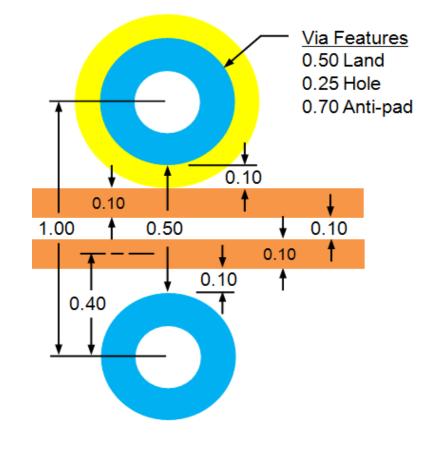

Via padstack sizes are in increments of 0.05mm. This includes all via-hole sizes.

The best via padstack for overall trace routing is – 0.5mm pad, 0.25mm hole, 0.7mm plane anti-pad

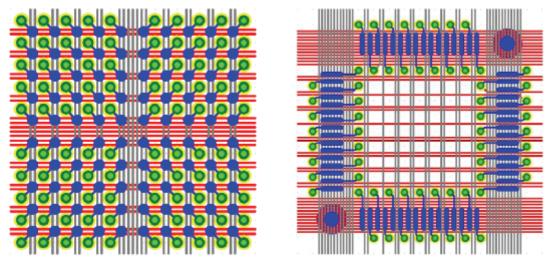

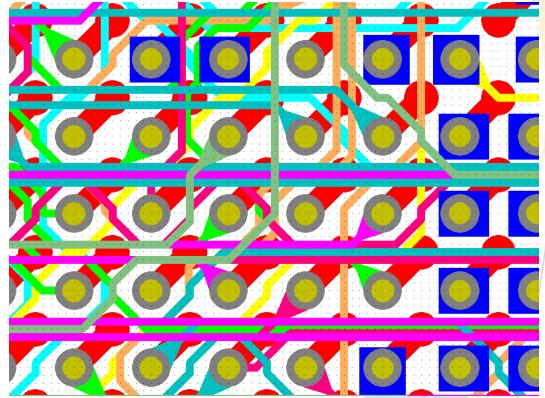

If every via in the PCB design was placed on a 1mm grid system, the traces can be routed across the design layout without unnecessary bends.

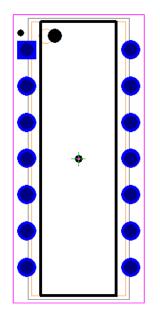

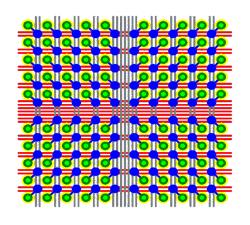

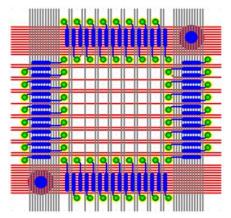

The best via fanout grid is 1mm. This allows for two 0.1mm traces to be routed in-between vias. See Figures 3, 4 and 5 below.

Figure 3

Figure 4

Figure 5 clearly illustrates 2 vias snapped on a 1mm grid with two 0.1mm traces perfectly centered between them. You can also route one 0.1mm trace between the vias perfectly centered. The plane anti-pad does not encroach under the traces and

provides a clean return path on the reference plane. This is a superior routing solution for high speed technology while providing a simplified working environment.

#### Trace / Space Size Grid System:

Metric trace width rules are in increments of 0.05mm with one exception 0.125mm (5 mils).

0.25mm = 10 mils

0.20mm = 8 mils 0.15mm = 6 mils

0.125mm = 5 mils

0.120 mm = 4 mils

0.075mm = 3 mils

0.05mm = 2 mils

#### **Trace Routing Grid System:**

The ultimate metric routing grid is 0.05mm.

#### **Reference Designators and Text Grid System:**

0.1mm is the common grid for placing Reference Designators and Text, but 0.05mm is used for tight spaces

#### **Copper Pour and Plane Fill Grid System:**

0.1mm is the common grid for Copper Pour outlines and snap grid, but 0.05mm can be used for high density part placement and trace routing

#### Mounting Hole Size and Placement Grid System:

All mounting-hole padstacks are in increments of 0.05mm and the placement grid is in 0.05mm increments.

#### **Conclusion:**

The Universal PCB Design Grid System is based on the 0.05mm unit. All shapes and sizes for every aspect of the PCB layout should be in increments of 0.05mm. Transitioning to the metric system for PCB layout is necessary to achieve electronic product development automation.

The United States is now the only industrialized country in the world that does not use the metric system as its predominant system of measurement. However, PCB design worldwide has been driven historically by the component manufacturers and CAD vendors to use the Imperial measurement system.

Clearly, U.S. companies that do not produce products or services to metric specifications will risk being increasingly noncompetitive in world markets. Japan has identified the U.S. lack of metric usage as a strategic impediment to access of U.S. products to the Japanese home market. In addition, consolidation of the European market product standards will make sales of non-metric products increasingly difficult and uncertain. Most U.S. companies understand that using metric units is essential to future economic success. Their hesitation may be due to uncertainty as to when and how to convert.

Through their actions, U.S. federal agencies are demonstrating an increasing determination to use the metric system of units in business-related activities. Example: Most component manufacturers have converted their component dimensional datasheets to millimeter units. Many of the results are not yet very visible to the public, which is not a direct target of current federal transition activities. Most veterinary and medical institutions have completed the transition to metric units however, industry is the main target, and is becoming increasingly aware of and generally welcomes the government's progress.

Industry acceptance of the wisdom of proceeding with the metric transition is due partly to the realization that producing to metric specifications and surviving in tomorrow's economic environment are synonymous. Most companies today export their products to a global market where metric based products are expected.

Additional documents to reference:

- "Metric Via Fanout" <u>http://www.pcbmatrix.com/Downloads/GeneralDocuments.asp</u>

- "Metric Pitch BGA and Micro BGA Routing Solutions Paper" <u>http://www.pcbmatrix.com/Downloads/GeneralDocuments.asp</u>

- "The CAD Library of the Future" http://www.pcbmatrix.com/Downloads/LPSoftware.asp

- "IPC Padstack Charts" <u>http://www.pcbmatrix.com/Downloads/LPSoftware.asp</u>

A comment from NIST - http://ts.nist.gov/WeightsAndMeasures/Metric/lc1136a.cfm#history

The current effort toward national metrication is based on the conclusion that industrial and commercial productivity, mathematics and science education, and the competitiveness of American products and services in world markets, will be enhanced by completing the change to the metric system of units. Failure to complete the change will increasingly handicap the Nation's industry and economy.

It's interesting to note that component manufacturers, world standards organizations, assembly shops and many PCB designers have already transitioned to the metric unit system. When the PCB "fabrication material" companies transition to the metric unit system, then the global electronics industry will complete the full transition to a standard grid system. Micron units are definitely the future. I believe that "10 microns" is better to express than "0.01 millimeters". Today, 80% of PCB designers can get away with using a 0.05mm grid system. Due to upcoming microminiaturization of component package technology, in 2012 it will be common place for PCB designers to produce metric based CAD library parts and PCB design layouts that will be in 10 micron (0.01mm) units.

This White Paper was written by: Tom Hausherr EDA Library Product Manager Valor Computerized Systems <u>Tom.Hausherr@Valor.com</u> <u>www.PCBMatrix.com</u>

# The Universal PCB Design Grid System

### By Tom Hausherr PCB Matrix, a Valor Company

# Mixing PCB Design Units

- Building CAD libraries in Metric and importing them into Imperial unit databases compromises perfection in part placement, via fanout and trace routing.

- Avoid designing your PCB Layout in Metric and have all of the mechanical constraints in Imperial units.

- Outputting Gerber data or X,Y coordinates for assembly machine production can be either complex in structure or simplified throughout the entire electronic product development process.

- This presentation reviews one of the single most important but often overlooked aspects in EDA.

# History

- From the 1960's through the 80's the primary PCB design grid system used Imperial units.

- Physical design units were in tenth Inch, but every PCB layout used 0.001" as the base unit of measure and everything was rounded in 1 mil increments.

- In the 1990's the world standards organizations banded together to agree that the metric unit system was superior for solving PCB design development.

- IPC started to publish all literature in metric units and by 2001, JEDEC and most component suppliers complied with the new world standard measurements

# Standards Organizations

- JEDEC Component Packages

- EIA Component Packaging (Tape & Reel)

- IPC Land Patterns (CAD Libraries)

- IEC European Electronic Standards

- NIST Naming Conventions

- JISSO Component Package Miniaturization

- JEITA Component Packages in Asia

- EIAJ Component Packages in Asia

- NEMI Component Manufacturer's

### **Gridless Shape Based**

- Due to the mixing of Inch & Metric PCB design units, PCB real-estate was not optimized when working with a snap grid for routing traces.

- CAD vendor's invented Shape Based routing technology to optimize trace routing.

- Due to the number of grid cells that need to be calculated, going off-grid or "gridless" uses an enormous amount of computer CPU and memory resources. The auto-router has hundreds of thousands of additional grid options for computation.

- A Gridless working environment in the majority of CAD tools is difficult to manually edit traces.

# PCB Grid System Impact

- Snapping objects to a course grid uses less CPU processing and computer memory

- Centers traces between objects

- Provides better aesthetic looking results

- Increases PCB layout productivity and quality

- Affects all aspects of PCB design layout

- CAD Libraries

- Part Placement

- Via Fanout

- Trace Routing

# Grid Unit Increments

- 0.05 mm is the base unit of measure that everything in a PCB design layout should be rounded to and this includes:

- CAD Libraries

- Part Placement

- Via Sizes

- Mounting Holes

- Board Outline

- Via Fanout

- Trace Widths

- Routing Grid

- Test Points

- BGA standard features are in 0.05 mm increments

- Here are the typical BGA ball sizes in 0.05 mm increments –

| Nominal Ball<br>Diameter | Reduction | Diameter | Land Variation |

|--------------------------|-----------|----------|----------------|

| 0.75                     | 25%       | 0.55     | 0.60 - 0.50    |

| 0.60                     | 25%       | 0.45     | 0.50 - 0.40    |

| 0.55                     | 25%       | 0.45     | 0.50 - 0.40    |

| 0.50                     | 20%       | 0.40     | 0.45 - 0.35    |

| 0.45                     | 20%       | 0.35     | 0.40 - 0.30    |

| 0.40                     | 20%       | 0.30     | 0.35 - 0.25    |

| 0.30                     | 20%       | 0.25     | 0.25 - 0.20    |

| 0.25                     | 20%       | 0.20     | 0.20 - 0.15    |

- BGA pin pitches are in 0.05 mm increments

- BGA package dimensions are in 0.05 mm increments

- Gull Wing lead package dimensions for SOP, QFP, SOD & SOT are in 0.05 mm increments

- Pin pitches are in 0.05 mm increments

- All Land Pattern data is in 0.05 mm increments

- Land Length and Width

- Land Snap Grid

- All 2D Line Widths

- Polarity Markings

- 2D Line Snap Grid

- Ref Des Height & Width

- Local Fiducials

- Chip component packages are in 0.05mm increments

- All Land Pattern data is in 0.05 mm increments

- Land Length and Width

- Land Snap Grid

- All 2D Line Widths

- Polarity Markings

- 2D Line Snap Grid

- Ref Des Height & Width

- Local Fiducials

- Rounded Rectangle Radius

- Chip component packages are in 0.05mm increments

- If pin pitch is Imperial units, so are the pad centers

- Most Land Pattern data is in 0.05 mm increments

- Pad Sizes

- Hole Sizes

- Plane Anti-pad

- Thermal Relief

- 2D Line Widths

- 2D Line Snap Grid

- Ref Des Height & Width

- Polarity Markers

- In every CAD library part there are four different 2D lines that need to be defined and they all perform a different purpose. Here are the default line width sizes for the IPC-7x51 standard library outlines

- Silkscreen Outline, 0.2 mm

- Silkscreen Polarity Marker, 1.2 mm

- Silkscreen Post Assembly Inspection Dot, 0.5 mm

- Assembly Outline, 0.1 mm

- Assembly Polarity Marker, 1.2 mm

- Placement Courtyard, 0.05 mm

- 3D Model Outline, 0.001 mm

### Part Placement

- Part placement courtyards are in 0.05mm increments

- Common part placement and PCB feature snap grids to insure that every pad center is on a 0.05 mm grid

- 1 mm for Large Parts

- 0.5 mm for Medium Parts

- 0.1 mm for Miniature Parts

- Silkscreen Text Height and Width

- Silkscreen 2D Line Snap Grid

- Ref Des Height & Width

- Global Fiducials

- Board Outlines

- Tooling holes

### Via Sizes & Fanout

- Via features are in 0.05 mm increments

- Pad Size

- Hole Size

- Plane Anti-Pad

- Thermal Relief

- Via Snap Grids

- 1 mm

- 0.5 mm

- 0.1 mm

- 0.05 mm

1 mm pitch BGA with 0.1 mm Trace

0.5 mm pitch QFP with 0.1 mm Trace

### Via Sizes & Fanout

• Via & Trace/Space features and routing grids are in 0.05 mm increments. Here are two vias on 1 mm grid.

# Trace / Space Sizes

Metric trace width rules are in increments of 0.05mm with two exceptions 0.075mm (3 mil) & 0.125mm (5 mil)

**Basic Rounded Equivalents**

- 0.30 mm = 12 mils

- 0.25 mm = 10 mils

- 0.20 mm = 8 mils

- 0.15 mm = 6 mils

- 0.125 mm = 5 mils

- 0.10 mm = 4 mils

- 0.075 mm = 3 mils

- 0.05 mm = 2 mils

### **PCB** Feature Sizes

- Reference Designator Height and Width Sizes are in 0.05 mm increments

- Copper Pour Outlines are in 0.05 mm increments

- Mounting Hole Sizes are in 0.05 mm increments

- Board Outline Dimensions are in 0.05 mm increments

- Board Cutouts are in 0.05 mm increments

- Board Keep-outs are in 0.05 mm increments

- Test Point Locations are in 0.05 mm increments

- Ref Des Snap Grids are in 0.05 mm increments

- Free Text Snap Grids are in 0.05 mm increments

### Conclusion

- IPC: The Universal PCB Design Grid System is based on the 0.05mm unit. All shapes and sizes for every aspect of the PCB layout should be in increments of 0.05mm. Transitioning to the metric system for PCB layout is necessary to achieve global electronic product development automation.

- NIST: The current effort toward national metrication is based on the conclusion that industrial and commercial productivity, mathematics and science education, and the competitiveness of American products and services in world markets, will be enhanced by completing the change to the metric system of units. Failure to complete the change will increasingly handicap the nation's industry and economy.

# The Universal PCB Design Grid System

### By Tom Hausherr PCB Matrix, a Valor Company