#### Minimizing Voiding In QFN Packages Using Solder Preforms

Seth J. Homer shomer@indium.com Ronald C. Lasky, PhD, PE rlasky@indium.com Indium Corporation Clinton, NY 13323 USA

#### ABSTRACT

According to Prismark Partners, the use of QFNs is growing faster than any package type except for flip-chip CSPs. Prismark projects that by 2013, 32.6 billion QFNs will be assembled worldwide, which represents 15% of all IC packages.

However, QFNs can be a challenge to assemble, especially when it comes to voiding. In most QFN assembly processes, solder paste is used as a means of attachment. This approach can be problematic, as excessive voiding often occurs due to the lack of standoff on the component and the high flux content of the paste. The addition of a solder preform can reduce such voiding by increasing the solder volume of the joint without adding flux volume.

Adding preforms to an assembly process is very easy. Preforms are packaged in tape & reel for easy placement by standard pick and place machines, right next to your components. The focus of this paper will quantify the preform requirements and process adjustments needed to use preforms in a standard SMT process. In addition, experimental data showing void reduction using preforms will also be presented.

Keywords: QFN, solder preforms, QFN packages, flux,

#### INTRODUCTION

Advances in flux formulations and particle size distribution have led to increased capabilities for solder paste; however, there are some challenges that still exist, especially as related to specific components. One component in particular is QFNs (quad flat pack no leads).

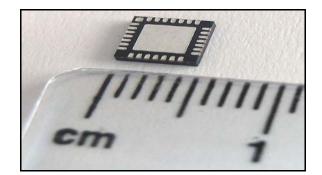

QFNs are close to the size of a chip-scale package. In addition to having no leads, QFNs have a thermal pad to conduct heat out of the integrated circuit (IC) in the QFN into the printed wire board (PWB). Figure 1 shows a QFN with its leads and thermal pad.

Figure 1. A QFN showing its leads and thermal pad

QFN packages are slated to have one of the highest growth rates in the next few years, predicted to be over 15% per year by Prismark Partners. This growth is understandable as QFNs are desirable for assembling miniaturized personal electronic devices such as mobile phones. With something like 3 billion worldwide mobile phone subscriptions, a number approaching one half of the world's population, mobile phones are rapidly becoming the defining electronic device of this era. So, miniaturized packages such as QFNs will continue to be in demand for the foreseeable future.

Unfortunately, when assembling QFNs, voids can form in the reflowed solder paste under the thermal pad. This paper will review steps to minimize this type of void formation by using solder preforms.

#### HOW VOIDS FORM IN QFNS

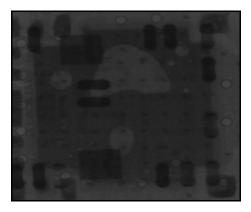

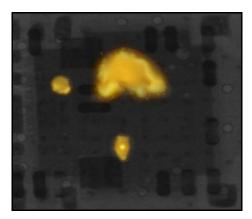

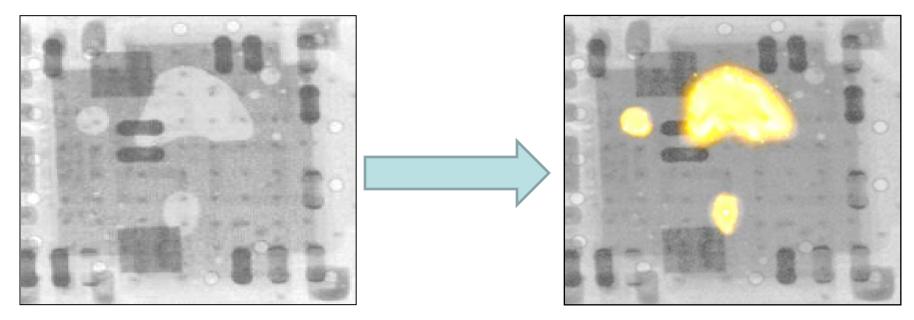

In the typical QFN assembly process, solder paste is printed on the PWB lead pads, as well as the PWB pad for the QFN thermal pad. Then the QFN component is deposited. The QFN design leaves little vertical space between the QFN thermal pad and the PWB pad. Therefore, during the reflow process, it is difficult for all of the flux volatiles to escape from the area of the QFN thermal pad. This phenomenon is acerbated by the fact that solder paste is approximately 50% flux by volume. As a result of these trapped volatiles, voiding is common. See Figure 2. In addition to this concern, some QFN designs are too large and demand more solder than printed paste can deliver to the solder joint. In these cases, the lack of solder is responsible for the voiding, which can result in poor thermal conductivity between the QFN pad and the PWB. This poor thermal conductivity can lead to the IC overheating and can then cause near term IC failures, in addition to long term IC reliability risk. Figure 3 shows a thermal image of such an overheating IC.

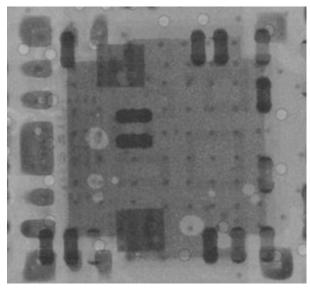

Figure 2. An X-Ray image of the voiding between the QFN thermal pad and the PWB

Figure 3. Illustration of the result of thermal path obstruction and localized heating

Acceptable voiding level criteria vary depending on the component and the application, but the most common QFN concern is with the largest void created on the thermal pad. A solder preform, in conjunction with the paste deposit, will assist in reducing the size of these large voids, as well as reducing overall quantity of voids.

First, however, it would make sense to determine if process changes alone can result in acceptable levels of voiding. Herron etal <sup>i</sup> performed extensive analyses in this regard. Their work showed a number of trends:

- 1. "Window paning" the solder deposit to create vents for the flux volatiles to escape will result in smaller voids, a desirable result.

- 2. However, the vent channels result in additional "open" areas that reduces solder joint continuity just as a void does.

- 3. Venting with window panes reduces the size of the voids, but typically does not reduce the total voiding area. Since hot spots are caused by large voids, the smaller voids that result from venting are still desirable.

- 4. Better voiding results are achieved if the pad is solder mask defined.

- 5. If the pad area has thermal vias, voiding will be minimized if the vias are plated with a solderable material, such as copper.

6. Even with venting and an optimum process, it is difficult to reduce voiding below 30% and, in some cases, 40%. So in cases where voiding must be below 20%, solder preforms will likely be required.

#### A QFN VOIDING SOLUTION USING SOLDER PREFORMS

Approaching a solution using a solder preform requires attention to the following areas:

- Stencil Design

- Preform Geometry

- Placement Parameters

- Preform Flux Coating

- Reflow Profile

#### STENCIL DESIGN

Stencil design parameters when using a solder preform vary, but results indicate that stencil designs that maximize the solder paste under the component result in less voiding, indicating that a maximum amount of solder is required under the QFN. Following the QFN manufacturer's design recommendations are a good starting point.

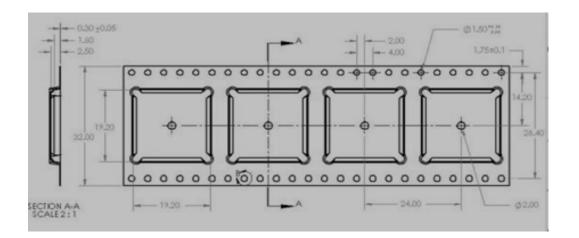

#### PREFORM GEOMETRY

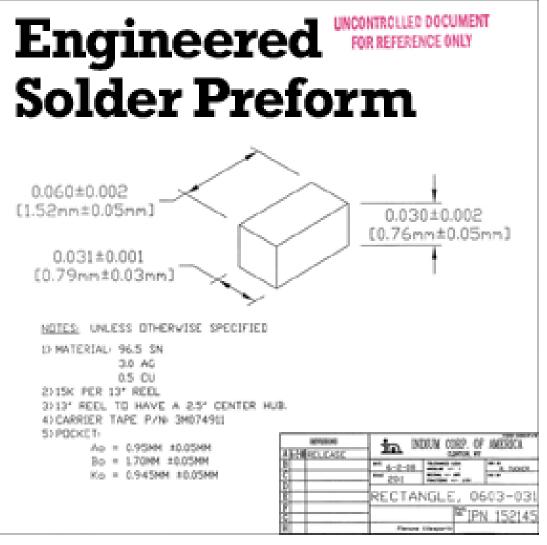

Experimentation has shown that the best results are achieved when the solder preform occupies approximately 80 to 85% of the area of the PWB pad, and is approximately 50% of the printed paste thickness. However, a minimum preform thickness of .0015" is required to prevent preform bending.

Table 1 Is an example of stencil calculation based on the Freescale QFN Application Note AN1902

| OFN                     |      | PCB Land Pattern |      |      |      | Stencil Aperture |          |       |  |

|-------------------------|------|------------------|------|------|------|------------------|----------|-------|--|

| QEN                     | 4    | x 4              | 9)   | x 9  |      | 4)               | <b>4</b> | 9 x 9 |  |

| Version                 | E    | s                | E    | s    | E    | s                | E        | s     |  |

| Lead pad width (mm)     | 0.37 | 0.37             | 0.28 | 0.28 | 0.32 | 0.32             | 0.28     | 0.28  |  |

| Lead pad length (mm)    | 0.92 | 0.92             | 0.69 | 0.69 | 0.75 | 0.75             | 0.69     | 0.69  |  |

| Pitch (mm)              | 0.65 | 0.65             | 0.50 | 0.50 | 0.65 | 0.65             | 0.50     | 0.50  |  |

| Thermal pad width (mm)  | 2.15 | 2.15             | 7.25 | 7.25 | 2.15 | 2.15             | 7.25     | 7.25  |  |

| Thermal pad length (mm) | 2.15 | 2.15             | 7.25 | 7.25 | 2.15 | 2.15             | 7.25     | 7.25  |  |

| Aspect ratio            | -    | _                | _    | _    | 2.52 | 2.52             | 2.20     | 2.20  |  |

| Area ratio              | _    | _                | _    | _    | 0.88 | 0.88             | 0.78     | 0.78  |  |

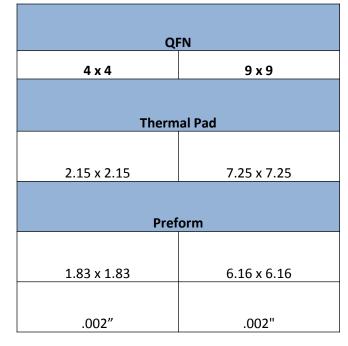

**Table 2** Represents the calculation for a suggested solder perform dimension

| Treform Design.  |             |  |  |  |

|------------------|-------------|--|--|--|

| QFN              |             |  |  |  |

| 4 x 4            | 9 x 9       |  |  |  |

| Thermal Pad      |             |  |  |  |

| 2.15 x 2.15      | 7.25 x 7.25 |  |  |  |

| Preform Geometry |             |  |  |  |

| 1.83 x 1.83      | 7.25 x 7.25 |  |  |  |

| .002"            | .002"       |  |  |  |

Preform Design

The ratios in table 2 are not fixed, merely a starting point. For instance, a larger pad area might require a solder perform closer to 80% of the pad area. However, the solder paste must provide tack for the preform and the QFN. Therefore, allowing for paste around the perimeter enables the solder paste on the edge of the preform to provide good tack to the QFN. This will help prevent skewing during reflow.

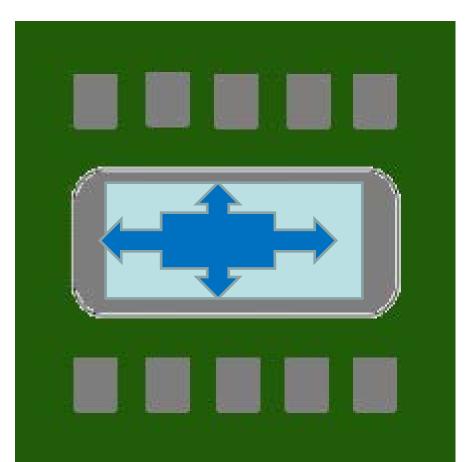

#### PLACEMENT RECOMMENDATIONS

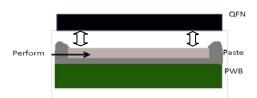

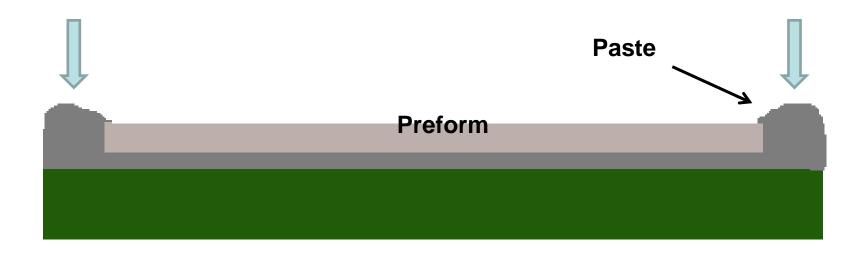

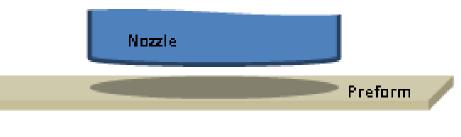

Figure 4. Illustration of a rectangular solder preform placed on the solder paste

Since the solder preform is packaged in tape & reel, its placement can be manipulated easily to achieve the desired result. In order to ensure there will be sufficient tack to hold the QFN component, the preform must be pushed into the paste far enough to allow for the solder paste contact to the QFN. (See Fig. 4) If this result isn't achieved, component floating will occur. In addition, it must be assured that the QFN leads make good contact to the solder deposit on the lead pads. The solder preform placement force is critical, as the preform still needs to be as flat as possible after it is placed into the paste. In addition, component placement pressure should be increased to ensure that the component seats well in the paste along the perimeter of the preform.

| Table 5. Theement pressure in Newton's |                    |             |  |  |

|----------------------------------------|--------------------|-------------|--|--|

| Placement Pressure                     | Placement Pressure | Placement   |  |  |

| Preform                                | Component          | Performance |  |  |

| 2n                                     | 2n                 | Poor        |  |  |

| 5n                                     | 3n                 | Fair        |  |  |

| 4n                                     | 3n                 | Good        |  |  |

| <b>Table 3.</b> Placement pro | essure in Newton's |

|-------------------------------|--------------------|

|-------------------------------|--------------------|

Increased placement pressure on the solder preform can result in its bending. The pick & place nozzle should occupy the most surface area possible on the preform. See Figure 5. The best nozzle will support the preform to preserve flatness. Bending can result in skewing of the QFN at reflow.

Figure 5. Illustrates the desired relationship between the nozzle and the solder preform

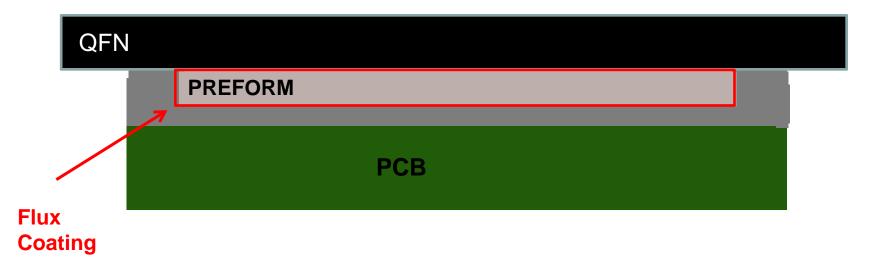

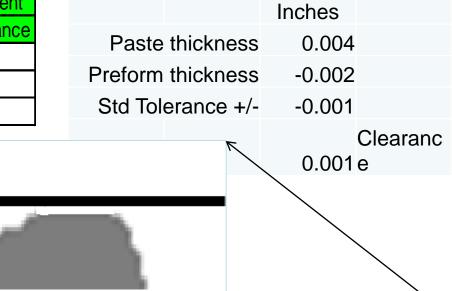

#### FLUX COATING

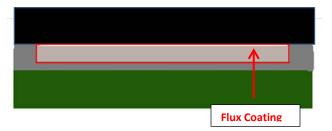

The interface between the top of the solder preform and the thermal pad on the QFN does not contain paste; therefore there is no flux to prepare the surface for solder wetting. This shortcoming can also cause excessive voiding. The solution is a flux-coated solder preform. See Figure 6. A solder preform coated with NC-9 flux at 1 to 1.5% by weight, will be sufficient to ensure good wetting without incurring voiding.

The flux coating must be deemed compatible with the paste used.

Figure 6. To minimize voiding the solder preform must be flux-coated as shown

#### **REFLOW PROFILE**

When adding a solder preform to the process, reflow profile adjustments are not specified or required. In cases of low thermal mass, a more linear profile is acceptable, but in cases of high thermal mass, a soak profile is required. The addition of a solder preform has actually been shown to reduce variability from one board to the next and is tolerant of reflow profile adjustments.

#### COLLABORATIVE TESTING OVERVIEW:

In order to evaluate the effectiveness of solder preforms in minimizing voiding in QFNs, a collaborative investigation was performed. The critical parameters in this study are listed below:

QFN thermal pad dimensions (dims): 2mm x 2mm Paste: No-clean solder paste with 89% SAC387, Type 3 PWB pad dims: 2mm x 2mm Stencil dims: 2mm x 2mm x .004" thick Preform dims: 1.7mm x 1.7mm x .002" thick Flux coating: NC-9 @ 1.0% by weight Profile: Soak

The resulting voiding average was less than 10%, and improvement from the initial voiding average can be as much as 50% or more of the solder joint.

#### In Conclusion:

As stated, voiding under QFNs is attributed to flux entrapment and/or lack of solder in the joint. The addition of a solder preform dramatically increases the solder content without excessive flux. The additional solder density residing in the center of the pad also inhibits the development of a large void.

To minimize voiding design considerations should include: **Stencil Design:** manufacturer recommended **Solder Preform Geometry:** approx. 85% thermal pad dimensions and 50% paste thickness **Placement Parameters:** increase placement pressure, muzzle selection **Flux Coating:** required for solder preform/QFN interface **Reflow Profile:** dependent/flexible

#### Acknowledgment:

Portions of this paper were presented at SMTAI 2011, Fort Worth TX.

<sup>i</sup> Herron, D, Liu, Y, and Lee, N.C., Voiding Control At QFN Assembly, SMTAI, Forth Worth, TX, 2011.

### Minimizing Voiding in QFN Packages Using Solder Preforms

#### <u>Results achieved:</u>

#### **Over 50% reduction in voiding**

Seth J. Homer shomer@indium.com

Ronald C. Lasky, PhD, PE <u>rlasky@indium.com</u>

Indium Corporation Clinton, NY 13323 USA

© INDIUM CORPORATION

### **QFNs are in Demand**

Prismark projects that by 2013, 32.6 billion QFNs will be assembled .

- Smaller form factors

- Increased demand on performance

### "The Challenge"

- Paste is approx. 50% flux by volume

- Low stand-off leaves no exit for excess volatiles

- Large voiding causes near term failure or long-term reliability risk

### **Solder Preform Defined**

TPS

Same metallic properties as solder pastes

APEX EXPO" 2012 CAN

- Specified geometry

- Offers predictable volume.

#### Parameters to be Discussed

- Stencil/pad design

- Preform geometry

- Placement parameters

- Preform flux coating

- Reflow profile

©INDIUM CORPORATION

### **Printed Paste on the Board**

#### **Voiding Control for QFN Assembly**

Authored by: Derrick Herron, Dr. Yan Liu, and Dr. Ning-Cheng Lee

TPS

PO" 2012 CAN

| Parameter      | Sub parameter        | Layers            |

|----------------|----------------------|-------------------|

|                | Microvia number      | 0, 16, 32, 36     |

|                | Peripheral venting   | With and          |

|                | for full thermal pad | without           |

| Thermal Pad    | Dividing method      | Solder mask,      |

| on PCB         |                      | venting channel   |

| OILLCD         | Thermal subpad       | Square, triangle  |

|                | shape                |                   |

|                | Thermal subpad       | 1, 4, 8, 9        |

|                | number               |                   |

| Stencil        | Aperture             | 85%, 100%         |

|                | Reflow profile       | Short, long cool, |

| Heat History   |                      | long, long hot    |

| ficat filstory | Other heat treatment | Prebake, 1        |

|                |                      | reflow, 2 reflow  |

Table 1. Parameters used in voiding study.

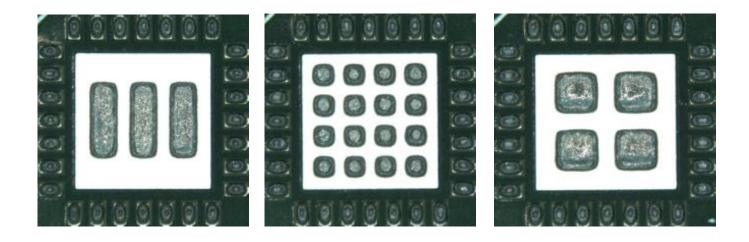

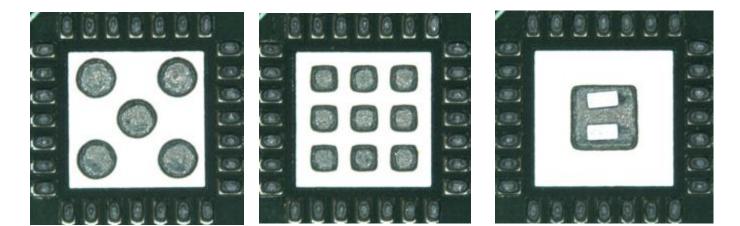

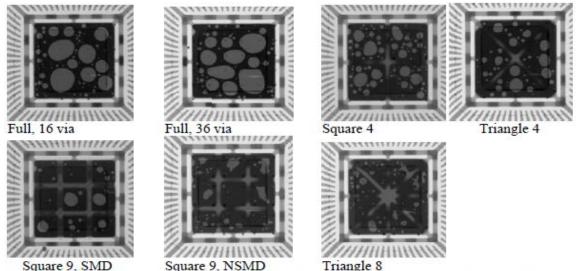

### **Thermal Pad Design**

| Full, no vent, 36 via     | Full, vented, 36 via  | Full, no vent, 16 via |

|---------------------------|-----------------------|-----------------------|

| Full, vented, 16 via      | Square 4, 16 via      | Triangle 4, 16 via    |

|                           |                       |                       |

| Square 9, 36 via,<br>NSMD | Square 9, 36 via, SMD | Triangle 8, 32 via    |

|                           |                       |                       |

Table 2. Design of thermal pads on test board.

#### **Printed Paste on the Board**

## **Can Process Changes Work?**

Herron etal<sup>1</sup> showed a number of trends:

PO" 2012

"Window paning" creates vents that results in smaller voids

TPS

Vent channels resulted in additional "open" areas that reduced solder joint continuity

| Table 2. Design           | Table 2. Design of thermal pads on test board. |                       |  |  |  |  |

|---------------------------|------------------------------------------------|-----------------------|--|--|--|--|

| Full, no vent,            | Full, vented, 36                               | Full, no vent,        |  |  |  |  |

| 36 via                    | via                                            | 16 via                |  |  |  |  |

|                           |                                                |                       |  |  |  |  |

| Full, vented,             | Square 4, 16 via                               | Triangle 4, 16        |  |  |  |  |

| 16 via                    |                                                | via                   |  |  |  |  |

|                           |                                                |                       |  |  |  |  |

|                           |                                                |                       |  |  |  |  |

| Square 9, 36              | Square 9, 36                                   | Triangle 8, 32        |  |  |  |  |

| Square 9, 36<br>via, NSMD | Square 9, 36<br>via, SMD                       | Triangle 8, 32<br>via |  |  |  |  |

1. Herron, D, Liu, Y, and Lee, N.C., Voiding Control At QFN Assembly, SMTAI, Forth Worth, TX, 2011

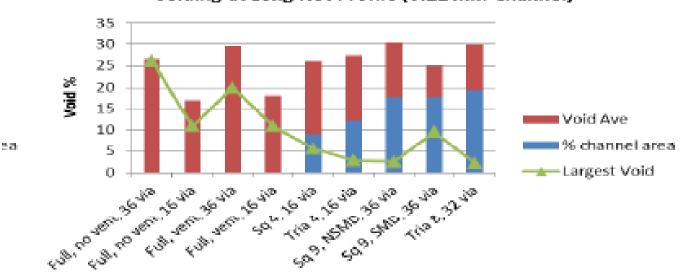

## **Can Process Changes Work?**

Plating thermal vias with solderable material minimizes voiding

(C)

TPS

CAN

2012

- Even with venting and an optimum process, it is difficult to reduce voiding below 30% and, in some cases, 40%.

- In cases where voiding must be below 20%, solder preforms will likely be required.

Voiding at Long Hot Profile (0.22 mm Channel)

### **Can Process Changes Work?**

- Venting reduces the size of the voids, but typically does not reduce the total voiding area.

- Hot spots are caused by large voids => the smaller voids are better.

- Solder mask defined is better.

Figure 5. X-ray images of QFN solder joints for designs with a 0.33mm wide channel reflowed with a long cool profile.

## **Preform dimensions**

TPS

CAN

#### \*80% of the QFN ground pad area is a good place to start.

#### Freescale Semiconductor

PO" 2012

Application Note

| QFN                     | PCB Land Pattern |      |      |      | Stencil Aperture |      |      |       |

|-------------------------|------------------|------|------|------|------------------|------|------|-------|

| QFN                     | 4:               | x 4  | 9)   | (9   |                  | 4)   | ( 4  | 9 x 9 |

| Version                 | E                | S    | E    | S    | E                | S    | E    | S     |

| Lead pad width (mm)     | 0.37             | 0.37 | 0.28 | 0.28 | 0.32             | 0.32 | 0.28 | 0.28  |

| Lead pad length (mm)    | 0.92             | 0.92 | 0.69 | 0.69 | 0.75             | 0.75 | 0.69 | 0.69  |

| Pitch (mm)              | 0.65             | 0.65 | 0.50 | 0.50 | 0.65             | 0.65 | 0.50 | 0.50  |

| Thermal pad width (mm)  | 2.15             | 2.15 | 7.25 | 7.25 | 2.15             | 2.15 | 7.25 | 7.25  |

| Thermal pad length (mm) | 2.15             | 2.15 | 7.25 | 7.25 | 2.15             | 2.15 | 7.25 | 7.25  |

| Aspect ratio            | _                | _    | _    | _    | 2.52             | 2.52 | 2.20 | 2.20  |

| Area ratio              | _                | _    | _    | _    | 0.88             | 0.88 | 0.78 | 0.78  |

AN1902 Rev. 4.0, 9/2008

#### Preform design:

| QFN                     |             |  |  |  |

|-------------------------|-------------|--|--|--|

| 4 x 4                   | 9 x 9       |  |  |  |

| Thermal Pad             |             |  |  |  |

| 2.15 x 2.15 7.25 x 7.25 |             |  |  |  |

| Preform                 |             |  |  |  |

| 1.83 x 1.83             | 6.16 x 6.16 |  |  |  |

| .002"                   | .002"       |  |  |  |

## Preform vs. Printed Paste Thickness

The preform thickness should be approximately 50-70% of the printed paste thickness

#### Why Flux Coated?

- Flux coating provides flux at the interface with the pad on the QFN

- Will not contribute to voiding

- Promotes wetting, discouraging void propagation

## Why Flux Coated?

TPS

#### QFN

IPC

APEX EXPO" 2012 CAN

#### Alloy: SAC305 with 1.5% by weight flux coating

1.83mm x 1.83mm x .05mm Preform wgt: .0012gms Flux wgt: .000018gms

6.16mm x 6.16mm x .05mm Preform wgt: .0141gms Flux wgt: .0002gms

## **Some Considerations**

Tps

0" 2012 CAN

- Experimentation was done using a no-clean paste in conjunction with a no-clean flux-coated preform.

- A preform without flux coating in conjunction with the no-clean paste did show better results but not as repeatable.

- If a water-wash paste is used, a preform without flux can still be placed but results are not know at this time.

# APEX 2012 CANT TO CIS CONT CIS

### **Pick and Place Parameters**

**Tape selection:** pocket dimensions must be adjusted to minimize travel in the pocket while in transport and on the line. This will minimize mis-picks.

- Pitch

- Depth of pocket

- Cover tape

### **Pick and Place Parameters**

TPS

#### **Placement Force is Crucial**

**PO" 2012**

- The preform placement force is critical, the preform needs to be as flat as possible after it is placed into the paste.

- Component placement pressure should be increased more than normal to ensure that the component seats well in the paste along the perimeter of the preform.

- Nozzle design is important, it should occupy as much of the preform surface as possible

| Placement Pressure | Placement Pressure | Placement   |

|--------------------|--------------------|-------------|

| Preform            | Component          | Performance |

| 2n                 | 2n                 | Poor        |

| 5n                 | 3n                 | Fair        |

| 4n                 | 3n                 | Good        |

### **Preform Flatness**

| Placement Pressure | Placement Pressure | Placement   |

|--------------------|--------------------|-------------|

| Preform            | Component          | Performance |

| 2n                 | 2n                 | Poor        |

| 5n                 | 3n                 | Fair        |

| 4n                 | 3n                 | Good        |

## **Reflow Profile Adjustments**

TPS

Ver 2015 0

- When a preform is used, the reflow profile should reflect a ramp to peak.

- This is not always possible as thermal mass of the assembly might require a soak.

- When introducing the preform, start with your existing reflow profile and adjust as needed.

## **Breaking Up the "Large" Void**

- Molten solder density is 2x the paste

- Wetting force gives direction to the volatiles

- Promotes out-gassing

#### Overview

- Printed paste should occupy the entire ground pad on full pad design

- 80% of the QFN ground pad area is a good place to start

- The perimeter of the preform will be paste, providing tack for the QFN

- Preform thickness 50%-70% of the printed paste thickness

- No-clean flux @ 1.5% by wt.

- No-clean flux compatibility is a requirement

- Placement parameters for high volume production

- Adjust reflow profile as necessary.

## **Collaborative Testing**

TPS

- QFN thermal pad dimensions (dims): 2mm x 2mm

- Paste: No-clean solder paste with 89% SAC305, Type 3

- PWB pad dims: 2mm x 2mm

- Stencil dims: 2mm x 2mm x .004" thick

- Preform alloy: SAC305

NAS 2105 0

- **Preform dims:** 1.7mm x 1.7mm x .002" thick

- Flux coating: No-clean flux @ 1.5% by weight

- **Profile:** Adjusted soak

The resulting void average was reduced by over 50%.

### Conclusions

The addition of flux-coated preforms to your process:

- Reduces overall voiding

- Prevents creation of a large void

- Can be used in high volume processes via tape & reel

- Can be customized for process variability

### **Questions?**

### **Thank You!**

Seth J. Homer Product Specialist Indium Corporation Office: 315-853-4900 Mobile: 315-351-6660 shomer@indium.com Ronald C. Lasky, Ph.D., PE Instructional Professor, Thayer School of Engineering, Dartmouth College Senior Technologist, Indium Corporation Mobile: 508 930 2242