#### From leaded to Leadless SMD (DFN) packages. Enabling Automatic Optical Inspection (AOI) for Leadless (DFN) Packages via Side Wettable Flanks

#### Hans-Juergen Funke

Nexperia Germany GmbH Hamburg, Germany Hans-Juergen.Funke@Nexperia.com

This paper and Presentation "From leaded to Leadless SMD (DFN) packages. Enabling Automatic Optical Inspection (AOI) for Leadless (DFN) Packages via Side Wettable Flanks" was first presented at the 2018 IPC Apex Expo Technical Conference and published in the 2018 Technical Conference Proceedings.

#### Abstract

Leadless semiconductor plastic packages (QFN) is a growing package category in terms of market share and diversity. This is also valid for low pin count semiconductors (e.g.: transistors and diodes). Several semiconductor companies offer a wide variety of leadless packages for such products. For small, low pin count products, these leadless packages are known as DFN (Discrete Flat No leads)packages. The diversity of DFN packages is still growing. There are several advantages of DFN packages compared to conventional leaded (SO) packages. A disadvantage is that the quality of the AOI inspection of the solder joint on the PCB is limited because the device terminals are only at the bottom of the products. The best way to inspect the soldering quality on PCB is x-ray inspection. However, especially automotive customers have requested suppliers to find a reliable alternative solution. In response to the requests to enable AOI (Automatic Optical Inspection) capability for leadless packages, side wettable flanks for DFN packages have been invented. With the help of side wettable flanks, a satisfactorywetting with solder during reflow soldering process at SMT can be guaranteed. The resulting solder fillet can be reliably inspected with AOI systems. An additional benefit is that the mechanical robustness on PCB could be improved (e.g.: higher device shear force). This paper describes the evolution from leaded to leadless semiconductor (DFN) low pin count packages. It will include survey of standard semiconductor low pin count leaded and DFN packages. The realization and boundaries of side wettable flanks will be discussed. Focus is on side wettable flanks for 3 to 6 I/Os DFN packages. Alternatives for >6 I/Os packages are considered: e.g.: "dimple", saw plate saw and immersion Sn plating. Verification of AOI capability as done together with a leading AOI system supplier complete this paper.

#### Introduction

Even thoughintegration is continuously increasing there is and will be a growing demand for discrete semiconductors. Discrete semiconductors are defined as a single device, for example a transistor or a diode, in a package. However double transistors anddiodes, arrays of devices or a combination of single function chips (e.g. combining transistors, diodes and/or passive devices) arealso considered as discrete semiconductors.

Besides being used for debugging of failures in IC design the main driving factor for discrete semiconductors include:

- Driving high currents

- Dealing with high voltage

- Easier power dissipation

- IC protection against ESD pulses and surge currents

- Flexibility of designing electronic circuits

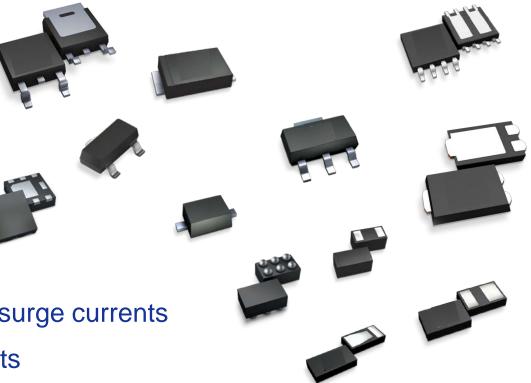

There is a broad variety of discrete semiconductor packages on the market, including packages with through hole leads. This paper concentrates on SMDpackages. The first SMDpackage which was developed around 1968 was the SOT23 (see figure 1).

#### Figure 1: SOT23 leaded SMD gullwing package

Over timevarious discrete semiconductor SMD packages with gullwing leads like SOT23 or flat leads like SOD323F (see figure 2) have been introduced. It is expected that the variety of such packages will continue to increase, be it at a slower rate in the future and mainly for medium power applications. However, they are still used in high and growing volume.

#### Figure 2: SOD323F leaded SMD flat lead package

The application area of leaded packages is for electronic devices which are not typically limited in terms of space e.g. consumer electronics like TV sets, monitors, radios, chargers and so on. Also in automotive applications, the leaded SMD packages are still commonly used because of its proven ease of use and board level reliability. One of their ease of use aspects is the AOI capability after soldering onto a PC board.

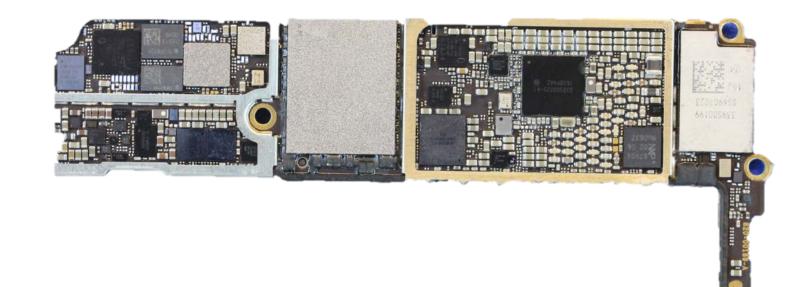

Other application fields require a high density of electronic components on PCBs because of space limitation. A good example of this are mobile devices like smart phones. Due to this fact, QFN (Quad Flat No lead) packages with connection pads only on the bottom have been established to reduce the required PCB area by eliminating the leads. These kinds of packages are also used in high volume for discrete semiconductors. The variety (e.g. because of miniaturization) as well as the volume are growing rapidly. Because of their small size and low number of I/Os for discrete semiconductors these packages are named DFN which stands for Discrete (or Dual) Flat No leads. An example of a DFN package is the DFN2020-6 as shown in figure 3. An explanation of the nomenclature of DFN package on the example DFN2020-6 is as follows: "2020" is the nominal x and y dimension, in this case 2.0 mm x 2.0 mm, the "6" means 6 I/Os.Because of its compact design DFN packages incorporate more advanced SMT technology compared to leaded packages. This technology is already widely established in the industry. A disadvantage in respect to ease of use of QFN/DFN packages is that the solder connection quality can only be fully inspected by x-ray, because the solder connection is only underneath the plastic body of the package.

#### Figure 3:DFN2020-6 as example for DFN packages

At this point it should be mentioned that because of space limitations, other packaging technologies have also been invented. For example, CSPs (Chip Scale Packages) which have either solder balls (also known as flip chip or WLCSP=Wafer Level

Chip Scale Package) or flat contacts (DSN packages =Discrete SiliconNo leads). These kinds of package usually come without a plastic body. The trend for this package category is that they will get a plastic protection at the side walls for some advanced applications. Beside the examples in figure 4 & 5 and some further remarks they are not in the scope of this paper.

#### Figure 4: Example of a WLCSP with solder balls

#### Figure 5:Example of a DSN diode package with flat contact pads

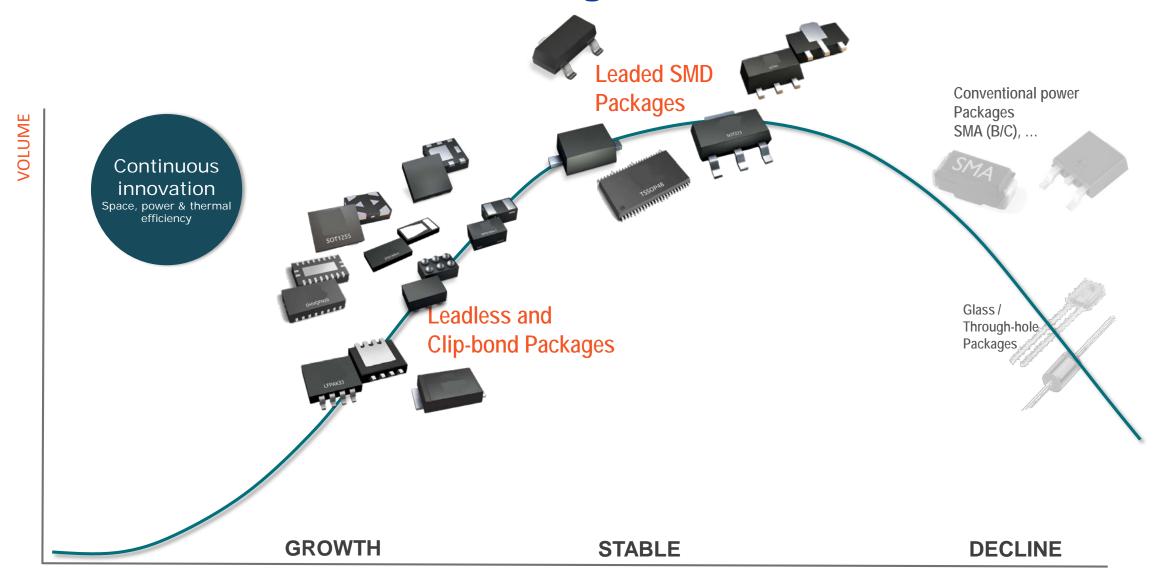

To complete the introduction of the DFN package and the variety of packages available, a package portfolio offered by a semiconductor standard product manufacturer is included in figure 6.

|           | Minia                         | turization                         |                               |                                |                           |                                       |                              |                                   |                          |                        |                              |                           |                                                                                             |                              | Medium p                                       | ower                                       |

|-----------|-------------------------------|------------------------------------|-------------------------------|--------------------------------|---------------------------|---------------------------------------|------------------------------|-----------------------------------|--------------------------|------------------------|------------------------------|---------------------------|---------------------------------------------------------------------------------------------|------------------------------|------------------------------------------------|--------------------------------------------|

| 2 Pins    | DSN0402-2<br>0.4 x 0.2 x 0.12 | <b>DSN0603-2</b><br>0.6. x03 x0.3  | DSN1006-2<br>1.0x06x0.3       | DSN1006U-2<br>1.0x0.6x0.3      | DFN1006D-2<br>1.0x04x0.37 | DFN1006-2<br>1.0x0.6x0.48             | 50D523<br>12x08x0.6          | DSN1608-2<br>16×08×0.25/0.2*      | DFN1608D-2<br>1.6x08x037 | 50D323<br>1/7x125x0.95 | SOD323F<br>1.7 x 1.25 x 0.95 | 500123F<br>26x1.7x1.0     | (SOD123W)<br>2.6 x 1.7 x 1.1                                                                | SOD123<br>2.68x1.6x1.15      | (SOD128)<br>3.8 x 2.6 x 1.0                    | (SOT1289)<br>5.8 x 4.3 x 0.78              |

| 3-4 Pins  | WLCSP4*<br>0.8 × 0.8 × 0.35   | DFN10068-3<br>1.0×0.6×0.37         | X5ON8                         | DFN1010D-3<br>1.1 x 1.0 x 0.37 | DT663<br>5×12×055 20×     | 1.25 x 0.95                           |                              | 2020D-3<br>20x062 50T23<br>2,9x13 | x1.0 SOT1438             | 8<br>50789<br>45x25x   | LEPAKS6<br>5.0x6.0x12        | SOT223<br>65×35×16        | 5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5<br>5 | рурак<br>11.0 x 10.0 x 4.3   | рак<br>11.0×10.0×4.3                           | 50T78<br>15.6x 10.0x4.4                    |

| 5-6 Pins  | X250N5<br>0.8x0.8x0.35        | <b>X250N6</b><br>1.0×0.8×0.35      | DFN1010-6<br>1.0 x 1.0 x 0.48 | DFN1010B-6<br>1.1 x 1.0 x 0.37 | DFN1412-6<br>1.4x12x0.47  | DFN1410-6/<br>X50N6<br>145×1.0×0.48   | WLCSP6<br>1.48 x 0.78 x 0.35 | WLCSP5*<br>1.51x1.14x0.65         | SOT665<br>1.6x1.2x0.55   | 507666<br>14x1.2x0.55  | 50T353<br>20x1.25x0.95       | SOT363<br>20x125x095      | DFN2020-6<br>2.0 x 2.0 x 0.62                                                               | DFN2020D-6<br>2.0x 2.0x 0.62 | DFN2020MD-6<br>2.0x2.0x0.62                    | 507457<br>29x1.5x1.0                       |

| 7-14 Pins | 5014<br>1.35×1.0×0.5          | <b>X250N8</b><br>1.35 × 0.8 × 0.35 | WLCSP10<br>1.57 x 1.17 x 0.57 | DFN2110-9<br>2.1 x 1.0 x 0.48  | DFN2111-7<br>2.1x1.1x05   | V550P8<br>2.0x23x0.85                 | DFN2510A-10<br>2.5x1.0x0.48  | DFN2520-9<br>2.5 x 20 x 0.48      | DFN2521-12<br>25x21x05   | DOFN14<br>30×2.5×0.85  | LFPAK33<br>33×33×085         | DFN4020-14<br>40×2.0×0.48 | DFNS6AD<br>5.0x6.0x0.9                                                                      | LFPAK56D<br>5.0x6.0x1.0      | инини<br>нинин<br>т <u>торрна</u><br>64×50×1.1 | ричи<br>ричи<br>рирак-7<br>11.0x 10.0x 4.3 |

| 216 Pins  | DQFN16                        | DOFN20<br>45x25x                   |                               | DQFN24                         | TSSOP16<br>64x5.0x1.1     | 1000000<br>100000<br>55000<br>64 x 65 |                              | TSSOP24<br>7.8×64×1.1             | 125×61×1.0               | TV50                   |                              | 5016<br>9/9×3.9×0.85      | 5020<br>15.3 x 7.5 x 2                                                                      | 111 mt<br>5024<br>45 i28     | 1/5×2.45                                       | DFN5050-32                                 |

Figure 6: Extract of discrete semiconductor package variety

#### From leaded to Leadless SMD (DFN) plastic packages

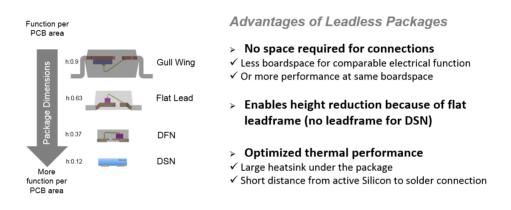

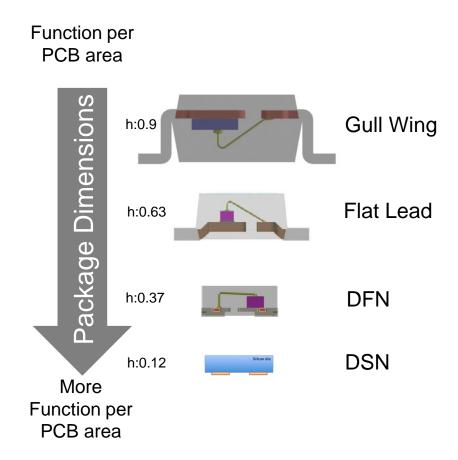

As already mentioned in the introduction, leadless DFN packages are becoming ever more important to realize growing electronic functionality in compact devices. This section will focus on the driving factors for evolution of packages from leaded SMD to leadless DFN packages and on the advantages of DFN packages. The overall driving factor is space limitation. The primary driver is area but height can also be on major concern. As a first step, height reduction was the motivation to go from gullwing SMD packages to flat lead SMD packages. Due to the shorter distance from chip to PCB solder point, the package's thermal resistance could also be somewhat reduced with this package design. The next step in height reduction was made by implementing DFN packages. In addition, DFN packages also have the advantage of further reducing the distance from chip, which is the source of power dissipation/heat, to the solder connection, because the chip is directly positioned above the solder pad. Only the leadframe and die attach layer are between the PCB solder connection and the chip. With that the thermal path is reduced to a minimum. In addition, it is possible to maximize the size of the heatsink (solderable metal area) under the package. Figure 7 illustrates the evolution from a leaded gullwing package to a leadless DFN packages. In this context, it should be noted that theintroduction of CSP (DSN) packages has been the nextstep in the evolution. Besides the obvious advantages of DFN packages there is one drawback which is that the AOI inspection of solder connection is limited because the solder pads are only at the bottom of the package.

Figure 7 : From leaded to leadless packages

#### **Construction and Manufacturing of Discrete Semiconductor Plastic Packages**

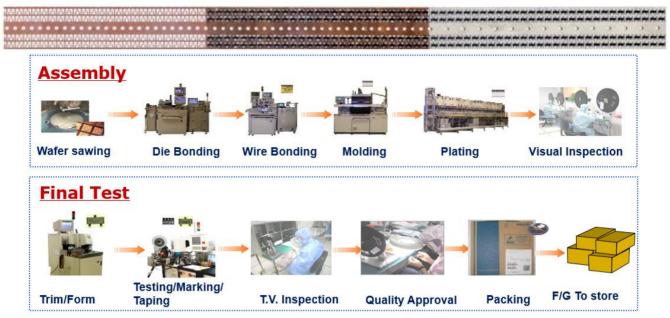

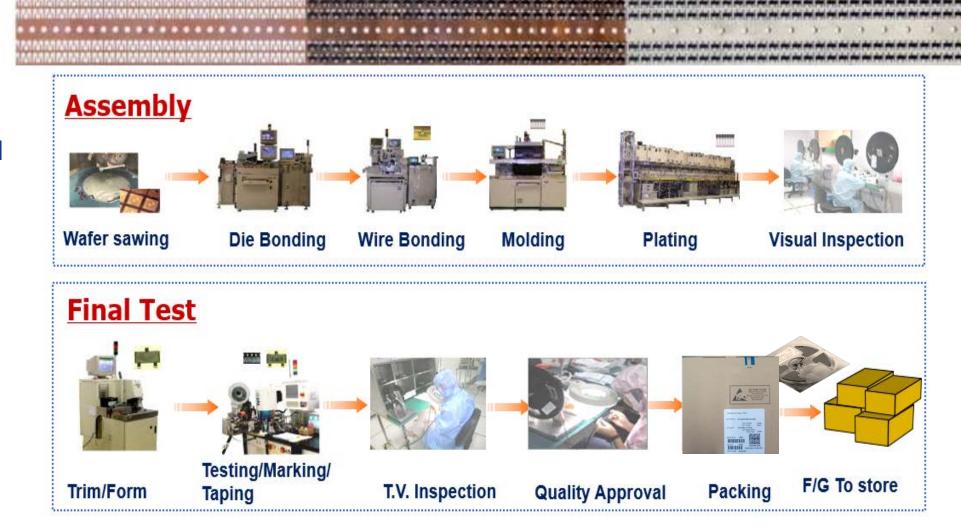

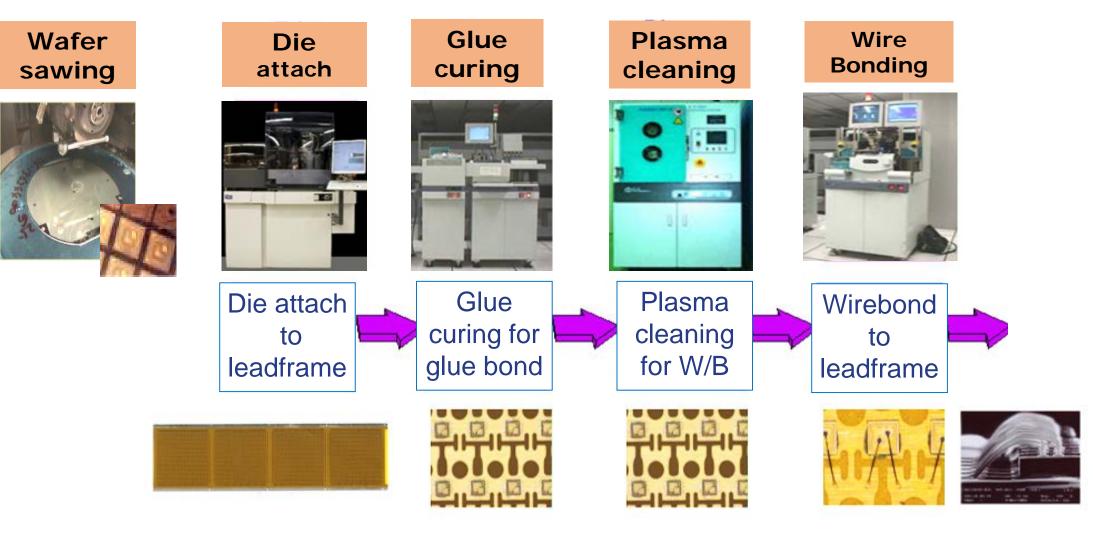

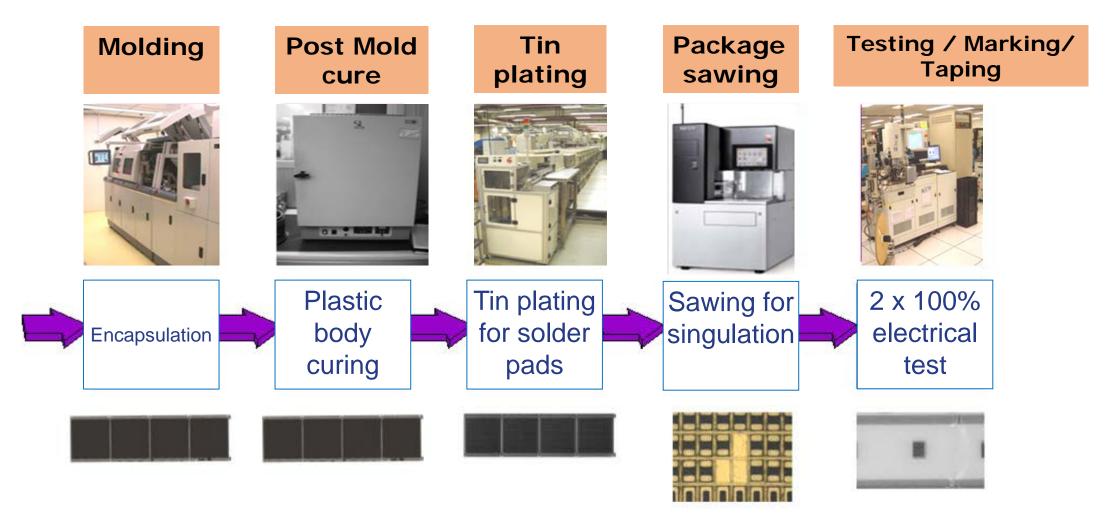

In this section a description of themanufacturing process and an explanation will be given as to why the lead tips of leaded SMD packages and the side flanks of DFN packages are usually not plated with a metal layer which ensures solder wetting. The production flow of leaded semiconductor packages is based on a leadframe. The leadframe is made froma Cu alloy or NiFe material with Cu plating. It has several functions: It acts as a carrier for transport in production, as connection for chips and wire, and a part of it builds the leads of the final package. After the chip attach and wire bond the body of the package is created by epoxy plastic encapsulation of the chip and leadframe part which is inside the package. That means every package is formed by an individual cavity in the mold tool. The next production step for the package is to have the leadframe electro galvanic plated with tin (Sn). This tin layer prevents the underlying metal, e.g. Cu, from oxidation and so guarantees a surface which is wettable by solder pasteduring the soldering process. Finally, the single packages will be separated by punching (trim) the leads out of the leadframe. Since the leadframe tin plating is done before singulation of the packages, the lead tips are not covered with Sn. Figure 8 illustrates the production process flow by example of reel to reel package assembly.

Figure 8:Discrete semiconductor assembly flow, example reel to reel production

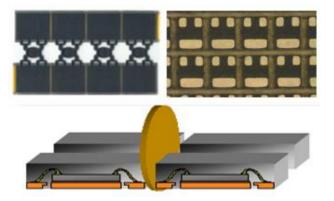

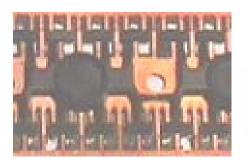

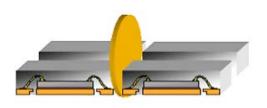

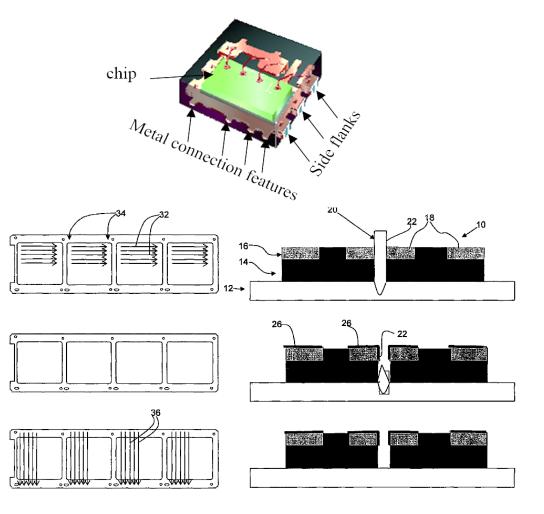

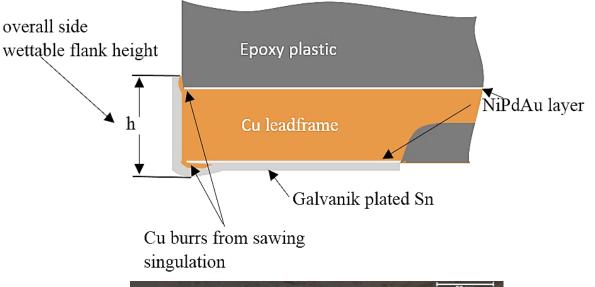

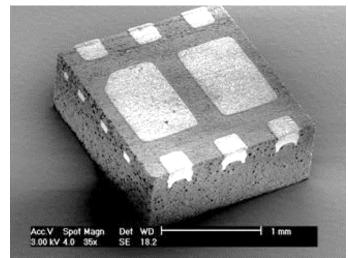

DFN packages are assembled in a similar manner as leaded packages. However, a map (or group) of several products are molded with epoxy plastic in one shot. All QFN / DFN package leadframes consist of Cu alloy base material. A lot of them are plated with a NiPdAu layer stack which is already applied by the leadframe supplier and which guarantees an oxide free surface for chip attach, wire bonding and, on the connection pads, for wetting with solder. Optionally, the NiPdAu layer may be left as is or plated in addition with tin. Singulation into individual packages is done by blade sawing. In case tin is applied the singulation is done after electro galvanic tin plating.As a remark, the same diamond coated sawing blade used for wafer dicing are used for package singulation.Figure 9 shows two leadframe strips with four maps each which are molded in one shot and the principle of sawing singulation into individual packages. Of course, in this case Sn plating of the side flanks of the DFN package pads is Cu alloy (leadframe base material) which may oxidize and so a wetting with solder in the reflow soldering process depends on storage condition and duration of the products and cannot be guaranteed.

Figure 9: Mold maps and singulation of DFN packages

#### Side Wettable flanks to provide guaranteed solder wetting of side pads for low I/O DFN packages

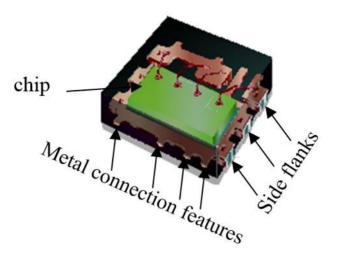

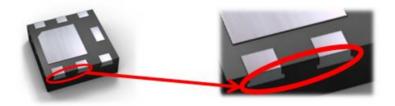

To overcome the disadvantage that solder wetting of the side flanks of DFN packages is not guaranteed, a solution has been developed to also cover the side flanks with plated tin in the same electro galvanic plating step as used for the bottom pads [1]. This technique is only applicable for DFN packages with up to four pads (can be more if multiple pads are fused to each other) and the pads need to be on two parallel opposite sides of the package. A plating of the pad's side flanks on all four sides of a DFN package is not possible with this method. The method relies on the fact that the solder pads of the

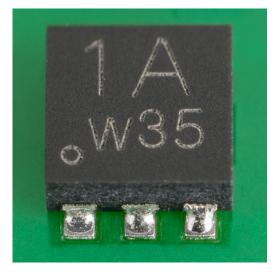

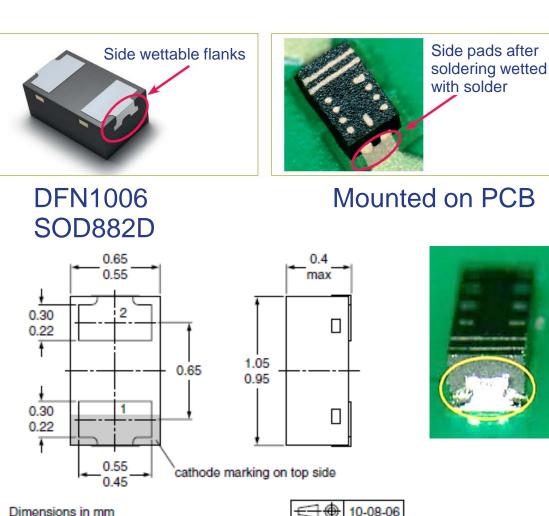

individual packages are connected by metal features, which are perpendicular to the I/O pad flanks, to the leadframe. These metal features will be separated at final singulation step. As example of a DFN package with wettable flanks refer to figure 3 and for detail view see figure 10 and figure 11.

Figure 10: Transparent view of DFN2020-6 package

Figure 11: Detail view on side wettable flank feature of DFN2020-6 package

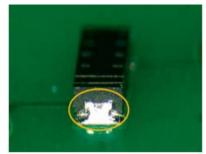

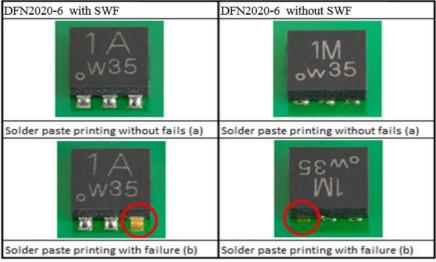

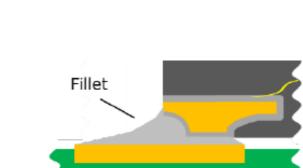

With the full tin-plated side wettable flanks it is guaranteed that the complete side pad surface will be wetted with solder during the reflow soldering process. An important advantage is that the plating layer on the side flank is as thick as on the bottom pads, which is around  $10\mu m$ . With that a wettable surface can be guaranteedeven after long periods of storage. Two examples of optical appearance of side flanks after soldering are shown in figure 12 for a DFN2020-6 package with and without side wettable flanks and in figure13 for the two-pad DFN1608-2 package.

Figure 12: Example DFN2020-6 comparison of SWF versus bare Cu side flanks after soldering

Figure 13: Example DFN1608 appearance of side wettable flanks after soldering

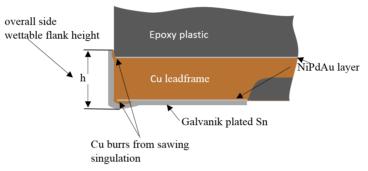

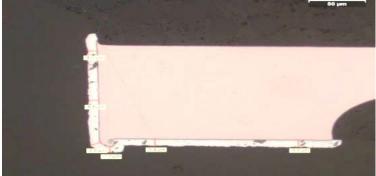

The height of the side wettable flanks of a DFN package which are plated with this method depends on the leadframe thickness. Usual leadframe thickness for DFN packages with a package height of  $h \ge 0.5$ mm up to 0.65 mm is 127µm (=5 mil) and for packages with package height h< 0.5mm it is 100µm (4 mil). The height of the side wettable flanks is higher than the leadframe thickness because some Cu burr will occur at sawing and this burr and the Sn plating thickness of the bottom pads will add to the height. Refer to the cross-section figure 14 for details.

Figure 14: Height of side wettable flanks

Based on the explanation above the wettable flanks meets the requirement of a minimum height of 100µm as raised by some automotive customers [2].

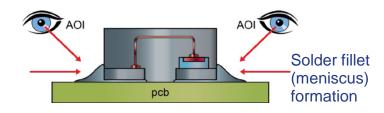

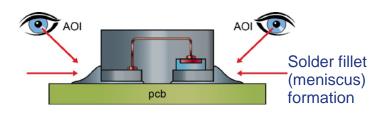

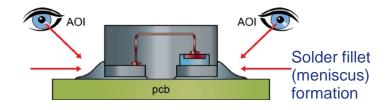

#### AOI capability of low pin count DFN packages with side wettable flanks

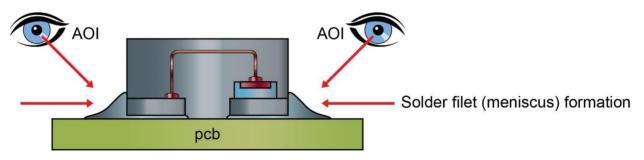

The main purpose of the side wettable flanks is to enable a reliable AOI capability for DFN packages. Thus, the costly x-ray inspection process can be skipped.

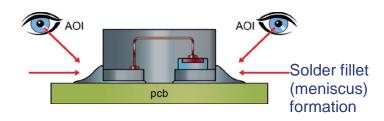

Figure 15 : AOI enabled DFN package with Side Wettable Flanks (SWF)

A boundary which needs to be considered is that the PCB solder pad size must be extended to be larger than the package dimension to give some space for the solder to build a meniscus or filet. The solder footprint recommendations of suppliers which offer packages with side wettable flanks include this extra space.

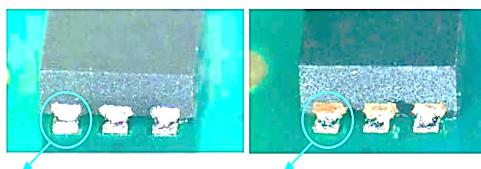

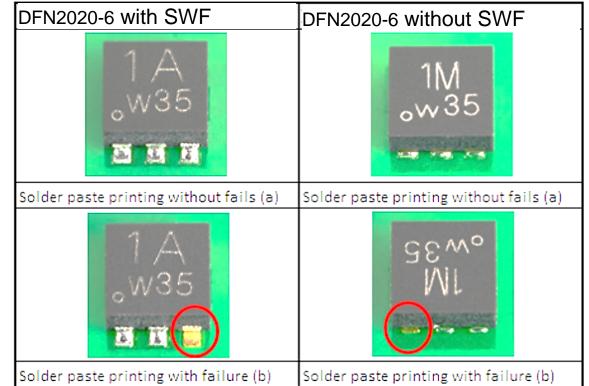

The effectiveness of the side wettable flanks for AOI inspection has been proven together with a leading AOI equipment supplier by evaluation of soldered DFN device equipped with SWF in comparison to corresponding DFN packages without

SWF. Multiple test boards were built on which the footprints were modified to accommodate the SWF package. The printed solder paste volume has been modified on purpose. E.g. on some PCB solder pads no solder was printed (see example figure 16). It could be confirmed that the DFN packages with SWF are suitable to reliably identify soldering failures with AOI on PCB after reflow soldering [4].

Figure 16: Example of solder failures on test board

#### Additional benefits of low pin count DFN packages with side wettable flanks

An additional benefit of side wettable flanks is that the mechanical robustness of the PCB bond is improved compared to DFN packages without SWF. For a survey of advantages refer to figure 17.

#### Improved mechanical robustness

#### Maximum shear force

Optimized for high shear forces for robust soldering

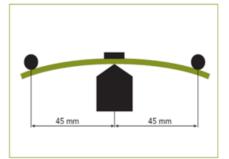

#### Maximum board bending

Very high board bending capability for designs with flexible PCBs

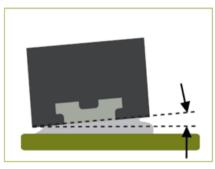

#### Minimum tilting angle

Reduced tilting angle for ultra flat PCB designs

Figure 17: Board level robustness improvements of DFN with SWF

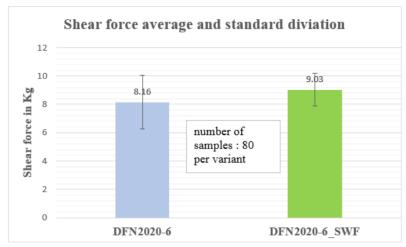

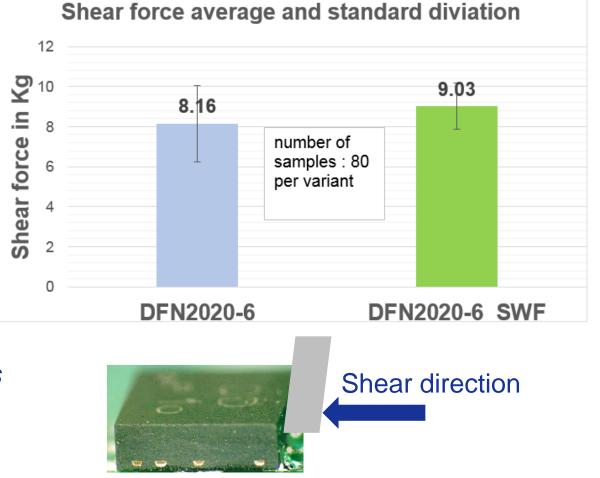

The shear force required to dislocate the package off the PCB is increased due to the meniscus that is formed after soldering. Shear force data for a DFN2020-6 package with and without side wettable flanks have been collected. Overall 80 samples each had been sheared on the PCB after soldering. The result is that shear force could be improved by about 10% with side wettable flanks as well as a reduction of the standard deviation of the shear values was observed. Refer to figure 18 for details. Important for a solid comparison is that the footprint, stencil apertures and solder paste type for both package variants are the same. The shear direction and height of the shear bit needs to be kept the same for all tests as well.

Figure 18: Shear Test on PCB for a DFN2020-6 package with and without Side Wettable Flanks (SWF)

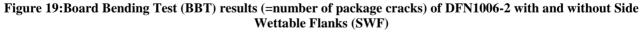

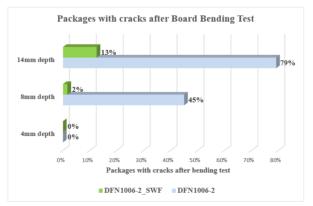

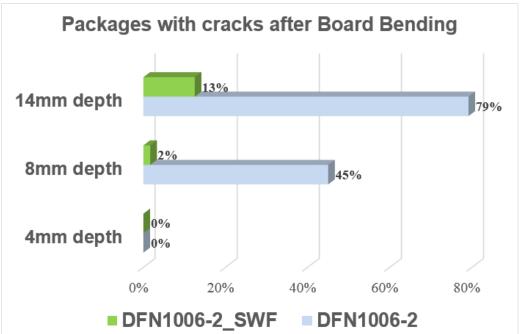

The board bending test robustness could be optimized as well, which is given by additional features at the package solder pads to achieve a better anchoring to the plastic body. For verification board bending tests were performed for DFN1006-2 packages with and without side wettable flanks. Over time 120 board bend test results per package variant following IEC60068-2-21 have been gathered. Because tests were done at different times the impact of process and material variations are eliminated. Summarizing all the data it could be proven that board bending depth for the DFN1006-2 package with SWF is up to 14 mm. For the data as displayed in Figures 19 and 20 the number of package cracks after board bending have been counted. Electrical testing of all samples are still pass even though the packages show cracks. Already tiny cracks as shown in figure 21 are counted. The bending robustness of both DFN1006-2 package variants is > 4mm and with that the package robustness is better than for passive chip components of same size for which the bending depth is often specified with 1mm.

| Row Labels             | Sum of Qty | BBT 4mm | BBT 8mm | BBT 14mm |

|------------------------|------------|---------|---------|----------|

| B DFN1006-2            |            |         |         |          |

| 2016Q1                 | 20         | 0       | 4       | 18       |

| 2016Q2                 | 20         | 0       | 20      | 20       |

| 2016Q3                 | 20         | 0       | 10      | 20       |

| 2016Q4                 | 20         | 0       | 9       | 17       |

| 2017Q1                 | 20         | 0       | 0       | 0        |

| 2017Q2                 | 20         | 0       | 11      | 20       |

| DFN1006-2 Total        | 120        | 0       | 54      | 95       |

| <b>■ DFN1006-2_SWF</b> |            |         |         |          |

| 2016Q1                 | 20         | 0       | 0       | 1        |

| 2016Q2                 | 20         | 0       | 1       | 8        |

| 2016Q3                 | 20         | 0       | 0       | 0        |

| 2016Q4                 | 20         | 0       | 0       | 0        |

| 2017Q1                 | 20         | 0       | 1       | 6        |

| 2017Q2                 | 20         | 0       | 0       | 0        |

| DFN1006-2_SWF To       | tal 120    | 0       | 2       | 15       |

Figure 20:Board BendingTest result DFN1006-2 with and without Side Wettable Flanks (SWF)

Figure 21: Example of plastic body crack after board bending

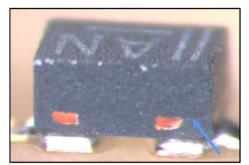

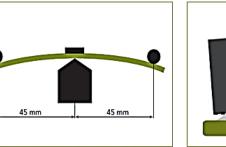

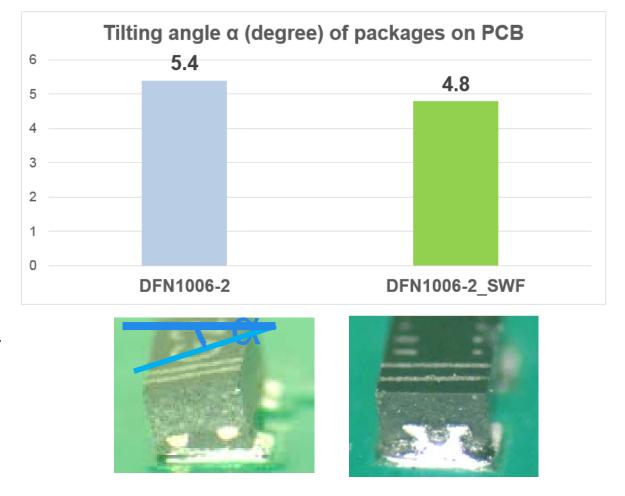

An advantage mainly relevant for 2 I/O DFN packages with side wettable flanks is that the tilting after soldering is reduced. In figure 22 is an example of package tilting angle of DFN1006-2 packages with and without side wettable flanks. It should be mentioned at this point that for a proper comparison the solder volume needs to be controlled carefully to be the same for both package variants. Otherwise this will be easily the dominating factor for tilting.

Figure 22: Tilting angle on PCB of DFN1006-2 packages without and with Side Wettable Flanks

#### Alternative Side Wettable Flank solutions for DFN packages with more than 6 I/Os

One alternative is to use dimples on side pads for DFN/QFN with multiple I/Os and leadframe thickness of  $\geq 200\mu$ m. Dimples are already etched and NiPdAu plated together with the bottom pads at the leadframe supplier. Sawing singulation is done between two adjacent packages in the middle of the etched dimples. The wettable feature size formed by the dimples is smaller than for the galvanic tin plating solution described previously. Usually packages with SWF made in this way will be delivered with NiPdAu pad plating, that means without additional tin plating on the pads. Figure 23 gives an example of such a package without, on the left, and with the dimple feature, on the right picture.

Figure 23: Example of multi I/O DFN/QFN package with dimples to achieve wettable flanks

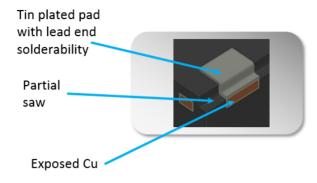

Another alternative is partial sawing of the DFN packages prior to tin plating, also known as the "saw plate saw" method. After map molding, sawing is done, but not completely, just to a depth to expose the side flank partially. The clue is that the pads are still connected by the remaining metal part of the pad flanks which are not separated. By this method, the continuity

of the leadframe is maintained for the galvanized plating process. Full singulation, with a thinner sawing blade than used for partial cut, is done after Sn plating. Due to the involved sawing tolerances, this method is the same as the dimples alternative, only suitable for  $\geq 200\mu$ m thick leadframes and as shown in figure 24 not the complete height of the side flank is covered with tin.

Figure 24: SWF realization by saw plate saw process

#### Outlook: E-less Sn plating as universal alternative for multi I/O package

An upcoming option is to apply e-less (immersion) tin plating to realize side wettable flanks as for the galvanic plating solution for low I/O count DFN packages, the e-less tin plating covers the side flanks in complete height ( $\geq$  leadframe thickness, refer to figure 14). It allows plating of multiple pads which can be arranged on all four sides of the DFN/QFN packages. The individual DFN/QFN package can be fully separated prior to e-less immersion tin plating. Unlike barrel plating, a good layer thickness conformity can be achieved by fixation of the packages in the immersion Sn plating process on a carrier (e.g. dicing foil). A disadvantage of immersion tin plating is that the growth rate of the tin is slow and getting slower with increasing Sn thickness. The achievable Sn layer thickness is less than  $3\mu$ m. However, plating chemistry suppliers offer new immersion Sn plating systems including surface treatments to provide as good wetting as plated and after storage.

#### Summary/Conclusion

The described galvanic tin plating method of side wettable flanks ensures solder wetting of the side flanks after storage. With current leadframe height a side wettable flank height of minimum 100 $\mu$ m can be achieved. DFN packages with side wettable flanks combine advantages of packages with and without leads in respect to AOI capability and board level robustness. The AOI capability on PCB is proven by a leading AOI system supplier. To realize side wettable flanks for multi pad packages ( $\geq 6$  I/Os) e-less tin plating of side flanks will be evaluated.

#### **General References**

[1] Martin Ka Shing Li, Max Leung, Pompeo Umali, "Singulation of IC packages, plating contact pads of the leadframe, and including contact pad edge regions formed by the first series of cuts", US Patent 13/876,819, 19 August 2014

[2] Udo Welzel, Marco Braun, Stefan Scheller, Sven Issing, Harald Feufel, "Wettable-flanks: Enabler for the use of bottomtermination components in mass production of high-reliability electronic control units", IPC, February 2017

[3] NXP / Nexperia "Application Note AN10365 "Surface mount reflow soldering" Rev 6.0, "2012

[4] Detlef Beer, Hans-Juergen Funke, Application Report, AOI Inspection of DFN Devices, 23 October 2013

#### APEX EXPO 2018 SUCCED AT THE OF TECHNOLOGY

## From leaded to Leadless SMD (DFN) Packages. Enabling Automatic Optical Inspection (AOI) for Leadless (DFN) Packages via Side Wettable Flanks

Hans-Juergen Funke Nexperia Germany GmbH Hamburg, Germany Hans-Juergen.Funke@Nexperia.com

### Content

SUCCEED

- Introduction, Why Discrete Semiconductors

- Discrete Semiconductors Packages, Portfolio Example

- Discrete Semiconductors Package Platforms

- Discrete Semiconductors Package Trends

- Driving factors for Leadless Packages

- Leaded SMD Packages, Characteristics and Assembly

- Leadless Packages (DFN/QFN), Characteristics and Assembly

- Side Wettable Flanks for low I/O DFN Packages

- Additional Benefits of Side Wettable Flanks

- Side Wettable Flanks for QFN and DFN Packages Examples of alternative SWF Solutions

- Summary and Conclusions

### Introduction, Why Discrete Semiconductors

Debugging failures in IC design

I ACITY

- Driving high currents

- Dealing with high voltage

- Easier power dissipation

- IC protection against ESD pulses and surge currents

- Flexibility of designing electronic circuits

### Worldwide Production Volume of Discrete Semiconductors > 400 billion pieces / year

SUCCEED

### **Discrete Semiconductors Packages, Portfolio Example**

DSN1608-2

DFN1608D-2

SOT143B

2.9 x 1.3 x 1.0

1.6 x 0.8 x 0.25/0.29 1.6 x 0.8 x 0.37

SOT23

2.9 x 1.3 x 1.0

SOD323

1.7 x 1.25 x 0.95

**SOT89**

4.5 x 2.5 x 1.5

SOD523

1.2 x 0.8 x 0.6

#### Miniaturization

X2SON5

5014

DQFN16

3.5 x 2.5 x 0.85

1.35 x 1.0 x 0.5

08×08×035

X250N6

X250N8

1.35 x 0.8 x 0.35

DQFN20

4.5 x 2.5 x 0.85

1.0 x 0.8 x 0.35

SUCCEED VELOCITY AT THE

DFN1010-6

$10 \times 10 \times 0.48$

WLCSP10

1.57 x 1.17 x 0.57

DFN1010B-6 1.1 x 1.0 x 0.37

TECHNOLOGY

DFN1410-6/ DFN1412-6 XSON6 1.4 x 1.2 x 0.47

DFN2111-7

2.1 x 1.1 x 0.5

1.45 x 1.0 x 0.48

6.4 x 6.5 x 1.1

DFN2020-3

2.0 x 2.0 x 0.62

DFN1006-2

1.0 x 0.6 x 0.48

WI CSP6

WLCSP5\* 1.48 x 0.98 x 0.35 1.51 x 1.14 x 0.65

DFN2020D-3

2.0 x 2.0 x 0.62

SOT665 1.6 x 1.2 x 0.55

SOT666 SOT353 1.6 x 1.2 x 0.55

2.0 x 1.25 x 0.95

LFPAK56

5.0 x 6.0 x 1.0

SOD323F

1.7 x 1.25 x 0.95

SOT363

2.0 x 1.25 x 0.95 2.0 x 2.0 x 0.62

DFN2020-6 DFN2020D-6 2.0 x 2.0 x 0.62

2.0 x 2.0 x 0.62

DFN2020MD-6

D<sup>2</sup>PAK-7

TSSOP14 6.4 x 5.0 x 1.1

LFPAK56D 5.0 x 6.0 x 1.0

DFN5050-32 5.0 x 5.0 x 0.85

DQFN24 TSSOP16 5.5 x 3.5 x 0.85 6.4 x 5.0 x 1.1

DFN2110-9

2.1 x 1.0 x 0.48

VSSOP8

2.0 x 2.3 x 0.85

DFN2510A-10

2.5 x 1.0 x 0.48

7.8 x 6.4 x 1.1

DFN2520-9

2.5 x 2.0 x 0.48

12.5 x 6.1 x 1.05

DFN2521-12

2.5 x 2.1 x 0.5

DOFN14

3.0 x 2.5 x 0.85

LFPAK33

3.3 x 3.3 x 0.85

DFN4020-14

4.0 x 2.0 x 0.48

5020

15.3 x 7.5 x 2.45

DFN56AD

5.0 x 6.0 x 0.9

5024

12.8 x 7.5 x 2.45

3.8 x 2.6 x 1.0 5.8 x 4.3 x 0.78

(SOD128)

D<sup>2</sup>PAK

SOD123

2.68 x 1.6 x 1.15

(SOD123W)

2.6 x 1.7 x 1.1

SOT223

SOD123F

2.6 x 1.7 x 1.0

DPAK 6.5 x 3.5 x 1.65

6.6 x 6.1 x 2.3

SOT78

(SOT1289)

### **Discrete Semiconductors Packages, Portfolio Example**

#### Miniaturization

SUCCEED VELOCITY AT THE

| 2 Pins    | D5N0402-2<br>0.4 x 0.2 x 0.12 | DSN0603-2<br>0.6. x 0.3 x 0.3   | DSN1006-2<br>1.0 x 0.6 x 0.3  | DSN1006U-2<br>1.0x0.6x0.3 | DFN1006D-2<br>1.0 x 0.6 x 0.37 | DFN1006-2<br>1.0 x 0.6 x 0.48                             | SOD523<br>12 x 0.8 x 0.6         DSN1608<br>1.6 x 0.8 x 0 | -                     | SOD323                     | SOD323F<br>1.7 x 1.25 x 0.95 | SOD123F<br>2.6x1.7x1.0 |                         | <b>SOD123</b><br>268 x 1.6 x 1.15     | (SOD128)<br>3.8 x 2.6 x 1.0                | (SOT1289)<br>5.8 x 4.3 x 0.78  |

|-----------|-------------------------------|---------------------------------|-------------------------------|---------------------------|--------------------------------|-----------------------------------------------------------|-----------------------------------------------------------|-----------------------|----------------------------|------------------------------|------------------------|-------------------------|---------------------------------------|--------------------------------------------|--------------------------------|

| 3-4 Pins  | WLCSP4*<br>0.8×0.8×0.35       | 1.0 x 0.6 x 0.37                | XSON8                         |                           |                                | T323         DFN24           x1.25 x 0.95         2.0 x 2 |                                                           | 50T23<br>29x1.3x10    | s sots9<br>1.0 4.5x2.5x1.5 | LFPAK56<br>5.0x6.0x1.0       | 50T223<br>65x35x1.65   | DPAK<br>6.6 x 6.1 x 2.3 | D <sup>2</sup> PAK<br>11.0x 10.0x 4.3 | FPAK<br>11.0x10.0x4.3                      | SOTT8<br>15.6 x 10.0 x 4.4     |

| 5-6 Pins  | <b>X250N5</b><br>0.8×0.8×0.35 | <b>X250N6</b><br>1.0x 0.8x 0.35 | DFN1010-6<br>1.0 x 1.0 x 0.48 | DEN<br>1.1 x              | ckage Ca                       | ategory<br>Leaded                                         |                                                           | Conventi              | Explan<br>onal pla         |                              | kage                   | Count<br>38             | FN2020D-6<br>0x20x0.62                | DFN2020MD-6<br>2.0x2.0x0.62                | 507457<br>29x15x1.0            |

| 7-14 Pins | 5014<br>1.35 x 1.0 x 0.5      | x250N8                          | WLCSP10<br>1.57 x 1.17 x 0.57 | DFN2                      | stic                           | DFN<br>QFN                                                |                                                           | Discrete<br>Quad Flat |                            |                              |                        | 25<br>5                 | FPAK56D<br>0 x 6.0 x 1.0              | инини<br>нити<br>TSSOP14<br>64 x 5.0 x 1.1 | рак-7<br>11.0x 10.0x 4.3       |

| ž         | Finan                         | Elu                             |                               | in chi                    |                                | DSN                                                       |                                                           | Discrete<br>with flat |                            |                              |                        | 5                       |                                       | 6                                          |                                |

| 216 Pi    | DQFN16<br>3.5 x 2.5 x 0.85    | DOFN20<br>4.5 x 2.5 x           |                               | QFN24<br>5x3.5x0          | p Scale                        | WLCSP                                                     |                                                           | Wafer Le<br>with Sold |                            | Scale I                      | Package                | 4                       | 12.8 ×                                | 4<br>4<br>67.5 x 2.45                      | DFN5050-32<br>5.0 x 5.0 x 0.85 |

### **Discrete Semiconductors Package Platforms**

SUCCEED VELOCITY AT THE

### **Discrete Semiconductors Package Trends**

SUCCEED VELOCITY AT THE

### **Driving factors for Leadless Packages**

Advantages of Leadless Packages

No space for leads needed

SUCCEED

- less PCB space for same electrical function

- or more performance on same PCB area

- Enables height reduction due to flat leadframes

- Optimized thermal performance

- large heatsink under plastic body possible

- short distance from active silicon to PCB solder pad

### **Driving factors for Leadless Packages**

----

### Leaded SMD Packages - Package Characteristics / Build up

VELOCITY

SUCCEED

- Leadframe based plastic packages

- Reel-to-reel or strip leadframe

- Die attach: eutectic (mainly) and epoxy glue

- Ball / wedge wire bonding (Cu or Au wires)

- Single cavity transfer molding

- Lead finish: Electro-galvanic Sn plating

### **Leaded SMD Packages** - Assembly Flow, Example Reel to Reel

SUCCEED VELOCITY AT THE

TECHNOLOGY

Example :

Reel to reel SOT23 production

### **Leaded SMD Packages** - Assembly Line, Example Reel to Reel

**Die-& Wire Bond**

SUCCEED VELOCITY AT THE

TECHNOLOGY

Molding

**Sn** Plating

### Leadless Packages (DFN/QFN) - Package Characteristics / Build-up

VELOCITY

Strip leadframe

SUCCEED

AT THE

- Die attach: epoxy glue

- Chip front contacts: Cu or Au wires

- Map molding (transfer molding)

- Lead finish: Electro-galvanic Sn or NiPdAu plating

- Package singulation: sawing

ball wedge

**Reverse wire loop** for thin packages

### Leadless Packages (DFN/QFN) - Assembly Line Set-up

TECHNOLOGY

SUCCEED VELDEITY

### Leadless Packages (DFN/QFN) - Assembly Line Set-up

TECHNOLOGY

SUCCEED VELDEITY

### **Side Wettable Flanks for low I/O DFN Packages**

VELOCITY

TECHNOLOGY

### Example 1 : DFN2020-6 (SOT1220)

SUCCEED

AT THE

- Exposed side pads are Sn plated =SWF (Side Wettable Flanks)

- Results in easily wetting with solder

- Enables visual inspection of solder connection on PCB by AOI

- Combines advantages of packages with and without leads

**100% solder wetting solution** with new 2 x 2 mm leadless package

Optimal visual solder inspection

High-quality solder connections

No complete wetting on side pad

- Quality of solder connection difficult to determine

- Very limited options for optical solder inspection

DFN2020-6 comparison of SWF versus bare Cu side flanks after soldering

### Side Wettable Flanks for low I/O DFN Packages

VELOCITY

TECHNOLOGY

### Example 2 : DFN1006 (SOD882D)

SUCCEED

AT THE

- Exposed side pads are Sn plated =SWF (Side Wettable Flanks)

- Results in easily wetting with solder

- Enables visual inspection of solder connection on PCB by AOI

- Combines advantages of packages with and without leads

Dimensions in mm

### Side Wettable Flanks for low I/O DFN Packages Realization

Electro-galvanic tin plating of bottom and side pads:

Exposure of side flanks by sawing

SUCCEED

- Bottom pads and side flanks plated in same process

- Final package singulation after plating

## Side Wettable Flanks for Iow I/O DFN Packages Requirement for ≥ 100µm SWF height

Usual leadframes thickness:

SUCCEED

AT THE

- for packages with  $h \ge 0.5mm$  : 127 $\mu m$

- for packages with h < 0.5mm : 100μm</p>

- Sawing burr and Sn plating thickness guarantees ≥ 100 µm SWF height also for packages < 0.5mm height</p>

VELOCITY

## Side Wettable Flanks for low I/O DFN Packages Verification of Effectiveness

AOI capability has been verified in cooperation with a leading AOI equipment supplier

SUCCEED

AT THE

Test board with footprints of various DFN packages has been realized

VELOCITY

- Solder paste volume has been varied by purpose:

E.g.: ± 50% more or less solder volume

- No solder paste printed at some pads

|           |                   |                 | ages           |                 |            | Corresponding Packages       |                   |                 |                |                 |           |  |  |

|-----------|-------------------|-----------------|----------------|-----------------|------------|------------------------------|-------------------|-----------------|----------------|-----------------|-----------|--|--|

| with      | solderal          | ole (S          | n plat         | ed) sid         | le pads    | without solderable side pads |                   |                 |                |                 |           |  |  |

| Package   | SOD/SOT<br>number | length<br>in mm | width<br>in mm | height<br>in mm | picture    | Package                      | SOD/SOT<br>number | length<br>in mm | width<br>in mm | height<br>in mm | picture   |  |  |

| DFN1006-2 | SOD882            | 1.0             | 0.6            | 0.37            |            | DFN1006-2                    | SOD882            | 1.0             | 0.6            | 0.5             |           |  |  |

| DFN1608-2 | SOD1608           | 1.6             | 0.8            | 0.37            |            |                              |                   |                 |                |                 |           |  |  |

| DFN1010-3 | SOT1215           | 1.1             | 1.0            | 0.37            | DINTOTO -3 | DFN1010-6                    | SOT1216           | 1.1             | 1.0            | 0.37            | onun 4    |  |  |

| DFN2020-6 | SOT1220           | 2.0             | 2.0            | 0.65            |            | DFN2020-6                    | SOT1118           | 2.0             | 2.0            | 0.65            | DFN2020-6 |  |  |

### Side Wettable Flanks for low I/O DFN Packages Verification of Effectiveness

AOI capability has been verified in cooperation with a leading AOI equipment supplier

SUCCEED

AT THE

Test board with footprints of various DFN packages has been realized

VELOCITY

- Solder paste volume has been varied by purpose:

- E.g.: ± 50% more or less solder volume No solder paste printed at some pads

- It could be confirmed that DFN packages with SWF enable reliable AOI of solder connection quality

## Side Wettable Flanks for low I/O DFN Packages Additional Benefits compared to DFN w/o SWF

- Maximized shear force of packages on PCB

- Maximized board bending robustness Together with smart leadframe design: up to 14 mm bending depth according to IEC60068-2-21

VELOCITY

TECHNOLOGY

SUCCEED

AT THE

Minimized tilting of packages after soldering Particularly for 2 I/O packages

#### Improved mechanical robustness

Shear bit

Maximum shear force Optimized for high shear forces for robust soldering Maximum board bending Very high board bending capability for designs with flexible PCBs

### Side Wettable Flanks for low I/O DFN Packages

### Maximized shear force of packages on PCB

Shear test according to IEC 62137-1-2

VELOCITY

SUCCEED

- Important to be controlled for comparison:

- PCB pad layout, stencil dimensions and solder paste type

- Shear direction and shear bit height

- Example for DFN2020-6 package:

- Shear test on PCB with 80 samples each with and without SWF

- SWF result in 10% higher shear forces

- SWF reduces the variation of shear forces

## Side Wettable Flanks for low I/O DFN Packages

### **Maximized board bending robustness**

Board bending test according to IEC60068-2-21

VELOCITY

- Bend test performance improved by inner package design, e.g. Leadframe anchoring features

- Example for DFN1006-2 package:

SUCCEED

- Bending test on PCB with 120 samples each with and without SWF

- All tested samples passed electrical insitu test

- SWF samples passed up to 14mm bending without any visual defect

- As reference: Chip capacitors in same size often specified with 1mm bending depth

## Side Wettable Flanks for low I/O DFN Packages Reduced tilting after soldering on PCB

Tilting of Packages after soldering

SUCCEED

AT THE

Important to control for comparison:

VELOGITY

- PCB pad layout, stencil dimensions and solder paste type

- Reflow soldering conditions

- Example for DFN1006-2 package:

- Tilting measurements on PCB with 40 samples each with and without SWF

- Tilting angle reduced by ~10% with SWF

### Side Wettable Flanks for QFN and DFN Packages

### **Examples of alternative SWF Solutions**

Saw plate saw

SUCCEED

AT THE

- Partial sawing of the DFN packages (leadframe) after molding prior to e- Sn plating

- Final singulation after Sn plating

VELOCITY

- Dimples

- Etched during leadframe manufacturing

- Plated with NiPdAu as the bottom pads

- No Sn plating at package assembly

Tin plated pad with lead end

solderability

Exposed Cu

Partial

saw

Advantage : Allow to realize SWF for packages with multi I/Os Disadvantage : Only possible for  $\ge 200 \mu m$  thick leadframe

## Side Wettable Flanks for QFN and DFN Packages Outlook : Immersion Sn Plating as universal Solution

E-less, immersion Sn plating can be applied after full singulation of packages

SUCCEED VELDEITY

AT THE

- In opposite to barrel plating the packages are fixed on a carrier or still in leadframe This enables a good layer thickness conformity

- Disadvantage is the slow growth rate of Sn in this process, layer thickness will be < 3 µm</li>

- Plating systems and surface treatments which still guarantee good wetting after storage have been developed by chemistry suppliers

■ Height of SWF will be ≥ leadframe height , > 100 µm

### **Summary and Conclusions**

= = = = = =

SUCCEED

- The described galvanic tin plating method for SWF ensures solder wetting of side flanks after storage

- With current leadrame thicknesses a SWF height of ≥ 100 µm can be achieved

- DFN packages with SWF combine advantages of packages with and without leads

- AOI capability of DFN packages with SWF was proven by a leading AOI equipment supplier

- DFN packages with SWF give additional benefits in mechanical robustness

- To realize SWF for multi I/O packages (≥ 6 I/Os) e-less (immersion) Sn plating will be evaluated

# Thank you for your attention Questions?

### References

AT THE

SUCCEED

ELOCITY

ECHAOLOGY

[1] "Martin Ka Shing Li, Max Leung, Pompeo Umali, "Singulation of IC packages, plating contact pads of the leadframe, and including contact pad edge regions formed by the first series of cuts", US Patent 13/876,819, 19 August 2014.