#### **IPC Midwest 2011**

#### **Cleaning Challenges in an HDI World**

#### Mark Northrup

#### Executive Summary

Electronic assembly innovations drive more performance using highly dense interconnects. Assembly residues may increase the risk of premature failure or improper functionality. The challenge for OEMs is to quantify safe residue levels and how residues impact long term reliability and functionality of hardware. To compound this problem, the question of "how clean is clean enough" is more challenging as conductors and circuit traces are increasingly narrower.

Highly dense bottom termination components decrease conductor pitch, spacing and standoff heights. The problem is that current spacing trends can yield spacing between printed circuit traces as small as 2 mils. As electrical fields rise, contamination at these narrower traces becomes more problematic due to voltage swings, high frequencies, leakage currents, and high impedance.

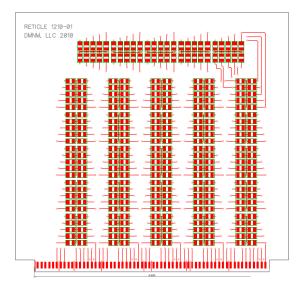

The purpose of this research is to build a new test board that provides a more accurate correlation and prediction of assembly residues to one or more aspects of long term reliability. The test board will be populated with a series of bottom termination components and cleaned. The research will follow a three phase strategy:

- Phase 1: PCB layout/Component Library Selection Geometries/Sample Size

- Phase 2 DOE Matrix: PCB Surface Finish, Flux & Cleaning Chemistries, Cleaning Systems/Analysis Techniques using IC, IR, HPLC, GCMS

- Phase 3 Conclusion: DFM approach for PCB designers layout relative to cleanliness limitations to establish a defined PCB design layout to facilitate an acceptable electrical measurement (i.e. fork, divider, capacitance, etc.) via a library of components (i.e., QFN, PLCC, BGA, etc.) geometries to test cleaner/chemistries capabilities

## Cleaning in an HDI World

#### Phase I

Mark Northrup & Andrew Buchan – IEC Electronics Mike Bixenman – Kyzen Corporation Joe Russeau – Precision Analytical Laboratory, Inc. Tim Jensen – Indium Corporation

### Phase I Topic Points

- Background

- Problem Statement and Research Purpose

- Research Time Line (Multi Phase Study)

- Phase I Project Goals

- IPC-B-52 Test Vehicle

- Pro's and Con's

- PCB Circuit Designs

- Many influencing factors to consider

- Flux Technologies

- Solubility Studies; FTIR Scan of Flux Types; Flux Volumes

- New HDI Test Board A Beginning

- Characteristics to Measure; Cleanliness Staking the Ground

- Organics

- Questions / Thoughts?

#### Background

For many years there has been a huge disconnect between the engineers that design the assembly and the chemists responsible for developing the assembly materials. In short, engineers and chemists don't speak the same language.

In today's HDI environment, this disconnect in language can cause more issues than it solves. The challenges of cleaning the smaller pitched components used in the HDI World means that the two disciplines need to be married together to better understand how to overcome these challenges...

#### **Problem Statement**

- Higher I/O = tighter pitch

- Higher I/O and lower gap height makes cleaning underneath part far more difficult

- Smaller gaps and spaces tend to be underfilled with flux.

- Flux at the periphery of the part is thinner and tends to be more difficult to clean.

- Flux near center of part tends to be easier to clean, but may also be the most problematic due to insufficient thermal exposure.

#### **Research Purpose**

- Build a new test board that provides

- Accurate correlation and prediction of assembly residues effects on reliability

- Support for a wider range of electrical / chemical testing

- o High Voltage / Hi-Pot

- o Low Level Leakage Current

- o Rate of Current Change (di/dt)

- o Frequency

- o IC, FTIR, GC-MS, etc.

- o Environmental

#### **Research Time-Line**

- Phase 1 Test Board Design

- PCB Layout

- Component Selection( Blanks )

- Phase 2 DOE Testing

- PCB Surface Finish

- Flux Types

- Cleaning Agents

- Cleaning Machines

- Phase 3 DFM for PCB Designers

- Layout guidelines to facilitate acceptable electrical performance

#### Phase I Goals

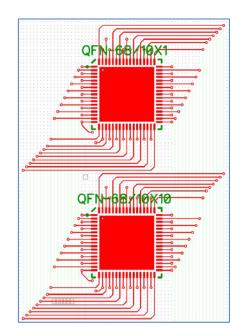

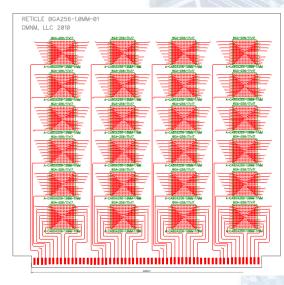

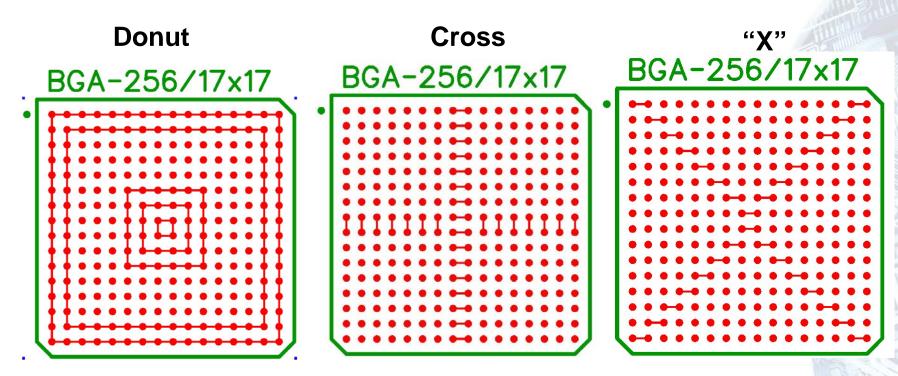

- Define best test pattern layout

- Ex. Doughnut, Cross and X-design

- Define the best component list and orientations to create a realistic cleaning challenge.

- Define the testing plan and methods of evaluation

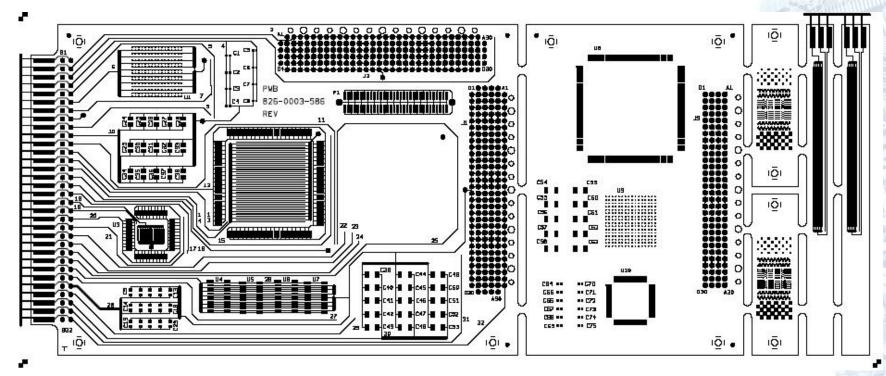

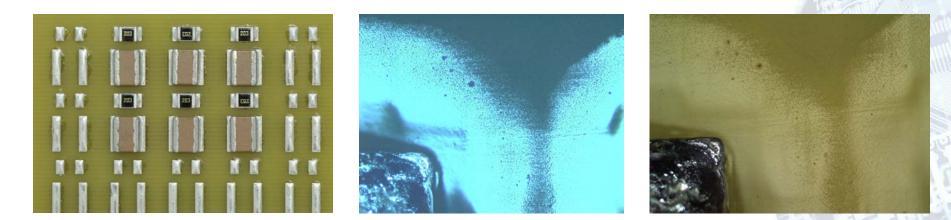

#### IPC-B-52 Test Vehicle

The B-52 is the most current test vehicle available to evaluate the impacts of flux residues.

Topside View

#### IPC-B-52 Pro's and Con's

#### Pros:

The B-52 improves flux and cleaning evaluations by adding in the effects and cleaning limitations created by components.

#### Cons:

- Designed for only low level leakage current testing and low voltage tests

- Unprocessed boards have failed at test voltages above 50 and 100 VDC.

- Not useful for evaluating other key electrical elements that flux residues influence

- High Voltage / Hi-Pot Testing

- Rate of Current Change Testing (di/dt)

- High Frequency Testing

- Small HDI components (01005's, 0201's, QFN's, etc) are not part of the board design and are not being characterized currently as part of the B52 research effort.

- Adopted pass / fail criteria is 100 megohm resistance levels and no visual presence of dendrites or corrosion.

- Criteria used for B-52 was originally developed for the B-24, which has no components and much different line widths and spacings.

- Visual inspections are difficult because of board layout and large ground plane. As such, it is very easy to miss items that may have impacts on tests.

### **PCB Circuit Designs**

#### **Parameters**

- 1. Test Pattern

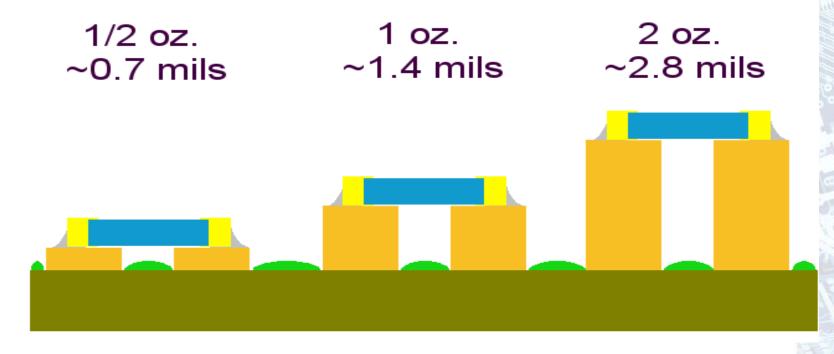

- 2. PCB Pad Sizes, Pitches, & Z-offsets

- 3. Directionality ( Devices relative to cleaning system )

- 4. Type of Fluxes ( Clean & No-Clean)/ Flux Volumes

- 5. Types of Solvents

- 6. Types of Cleaners

- 7. Ionic Levels Warranted

- 8. Inspection techniques (Visible, IR, UV, etc.)

- 9. Organic levels (FTIR, HPLC, GCMS, etc.)

- 10. Environmental Conditions

Electrical Characteristics to Measure

- 1. High Voltage / Hi-Pot

- 2. Leakage Current

- 3. Rate of Current Change (di/dt)

- 4. Frequency

- Electrical Parameters Under Evaluation

- 1. High Voltage / Hi-Pot

- 1. Zero Volts

- 2. 10 Volts

- 3. 100 Volts

- 4. 500 Volts

- Electrical Parameters Under Evaluation

- 2. Leakage Current

- ✓ mA✓ uA

- ✓ nA

- Electrical Parameters Under Evaluation

- 3. Rate of Current Change (di/dt)

- Amount (A, mA, uA )

- ✓ Rate (mS, uS , nS)

- Electrical Parameters Under Evaluation

- 4. Frequency

- ✓ MHz✓ GHz

- ✓ THz

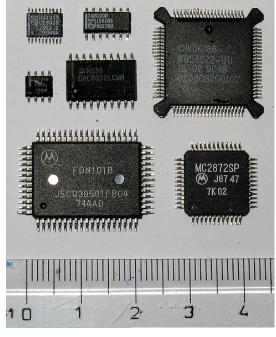

#### Package Styles

**E**

1051

+ 4.7 10v

105 16V

6.8

20

1

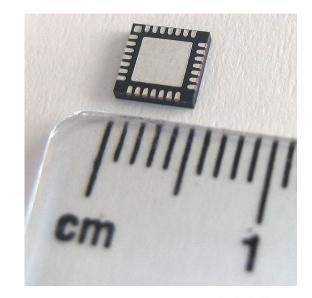

### Minimum Pitch and/or Spacing Barriers?

SMT Rectangular passive components (mostly resistors and capacitors):

01005 (0402 metric): 0.016 × 0.008 in (0.41 × 0.20 mm) 0201 (0603 metric): 0.024 × 0.012 in (0.61 × 0.30 mm) 0402 (1005 metric): 0.04 × 0.02 in (1.0 × 0.51 mm) 0603 (1608 metric): 0.063 × 0.031 in (1.6 × 0.79 mm) 0805 (2012 metric): 0.08 × 0.05 in (2.0 × 1.3 mm) 1206 (3216 metric): 0.126 × 0.063 in (3.2 × 1.6 mm) 1210 (3225 metric): 0.126 × 0.1 in (3.2 × 2.5 mm) 1806 (4516 metric): 0.177 × 0.063 in (4.5 × 1.6 mm) 1812 (4532 metric): 0.18 × 0.12 in (4.6 × 3.0 mm) 2010 (5025 metric): 0.2 × 0.1 in (5.1 × 2.5 mm) 2512 (6432 metric): 0.25 × 0.12 in (6.3 × 3.0 mm)

#### **Circuit Designs**

SMT

QFN

BGA

#### **Test Patterns**

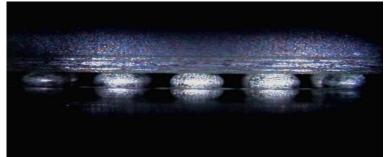

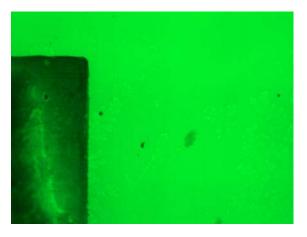

### Flux Technologies

- Flux type and its impact on reliability

- As components decrease in size, residue bridges conductors

- Does this impact reliability, even for no-clean flux?

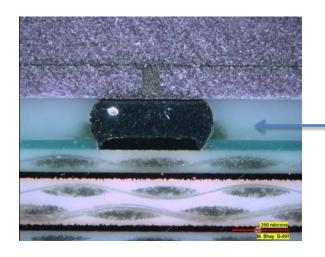

Flux Residue Next to Solder Bump

Source: IPC CH65B Guidelines for Cleaning Printed Circuit Assemblies, 2011.

#### **Z-Axis Offset**

### **Flux Residues**

- Numerous manufacturers worldwide

- Wide variation within formulations

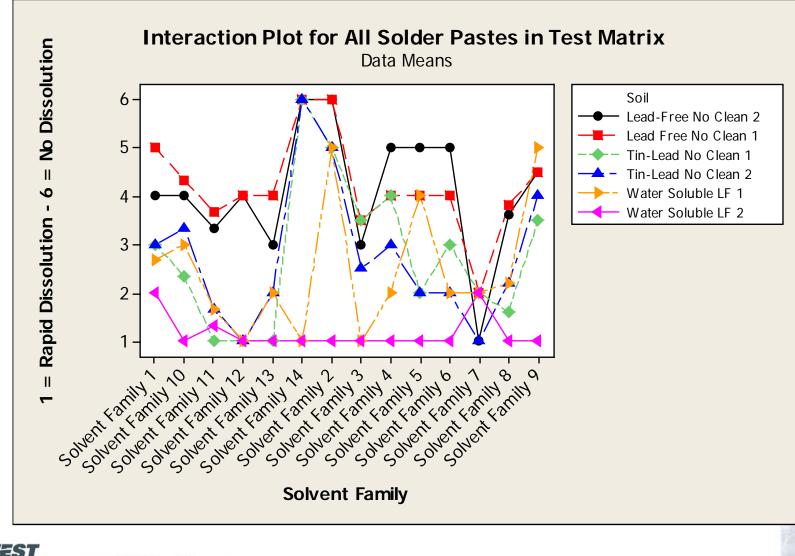

### Solubility Studies on Flux Types

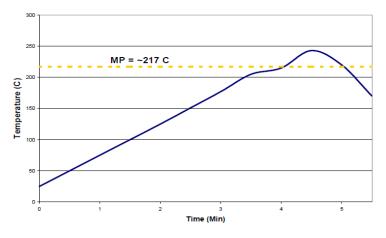

#### **Temperature Impact**

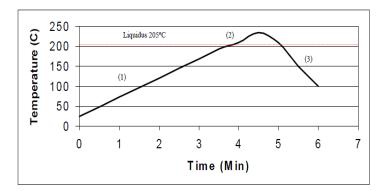

Solder Paste with SnAgCu Lead Free Alloy Melting Point Approximately 217°C

Solder Paste with 86.9Sn10In3.1Ag (Indalloy #254) Solidus 204°C Liquidus 205°C

Solder Paste with Indalloy #281 & 282 Ind281 (58Bi 42Sn) 138°C Eutectic Ind282 (57Bi 42Sn 1Ag) 140°C Liquidus

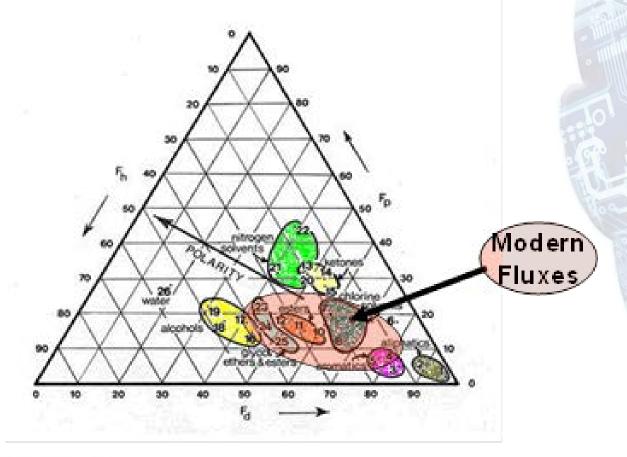

#### **Solvent Families**

Solvents that dissolve soils

- Solvate the reactants and reagents in the soil so they dissolve

- Good solvents for the soil

- 1. Should be inert to the reaction conditions

- 2. It should dissolve the reactants and reagents

- 3. It should have a desirable boiling point

- 4. It should be easily removed

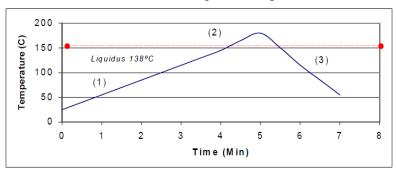

#### Second Solvent Criteria

Like Dissolves Like

- Non-polar reactants dissolve non-polar solvents

- Polar reactants dissolve in polar solvents

- There are three measures of polarity in a solvent

- Dipole moment

- Dielectric constant

- Miscibility in water

- Solvents with large dipole moments and dielectric constants are considered polar

- Solvents with low dipole moments and dielectric constants are considered non-polar

### Solubility Model

• Expose reflow flux residues to solvent families

#### **Cleaning Agent Options**

- Cleaning agent must be matched to soil

- Cleaning agent must be matched to the equipment

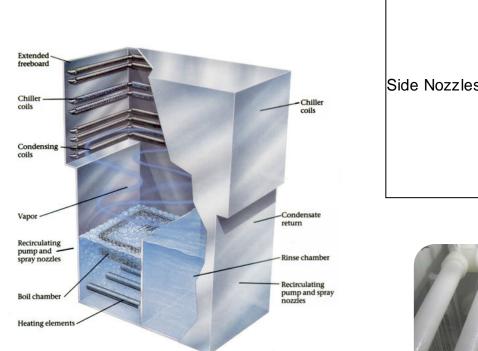

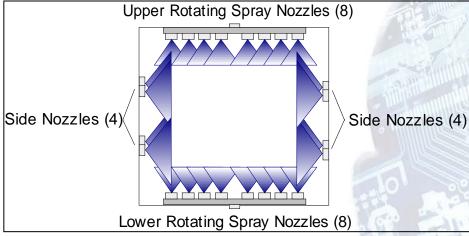

#### **Energy Options**

#### Flux Volumes

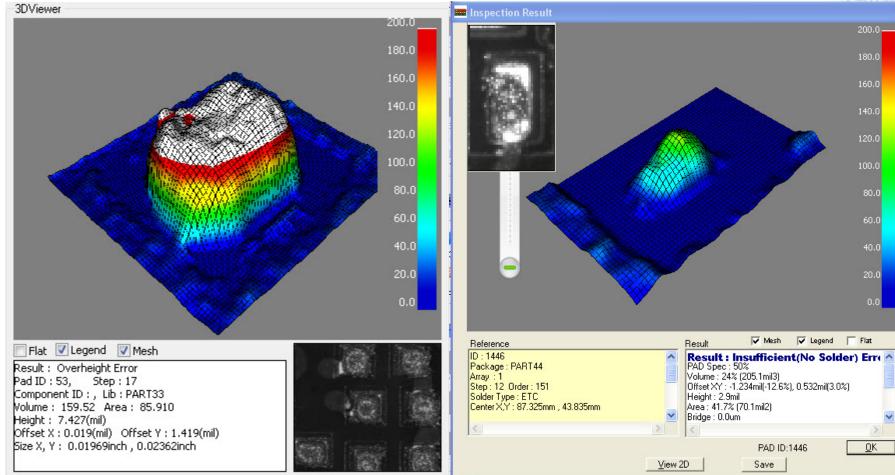

159.52% Volume of Flux on a BGA pad

24% Volume of Flux on a QFN pad

### Cleanliness – Staking the Ground

- Utilize Ion Chromatography to evaluate ionic cleanliness

- Anions (F<sup>-</sup>, Cl<sup>-</sup>, Br<sup>-</sup>, NO<sub>2</sub><sup>-</sup>, NO<sub>3</sub><sup>-</sup>, PO<sub>4</sub><sup>-3-</sup>, SO<sub>4</sub><sup>-2-</sup>)

- Cations (Li<sup>+</sup>, Na<sup>+</sup>, NH<sub>4</sub><sup>+</sup>, K<sup>+</sup>, Mg<sup>2+</sup>, Ca<sup>2+</sup>)

- Weak Organic Acids (Examples: Adipic, Succinic, Glutaric, etc)

- Develop "Stop Light" Criteria for different residues for defined Electrical Characteristics to estimate field performance effects.

- Electrical (HV, Leak., Rate, Freq.)

- Clean vs. No-Clean

- Environmental 85RH/85C, 95RH/95C, 90RH/90C

- Bare boards

- Stop Light Model

Red = Bad (residue levels exceed limit)

Yellow = Good to Caution (residue levels at or approaching limit)

Green = Pass (residue levels are below set limit)

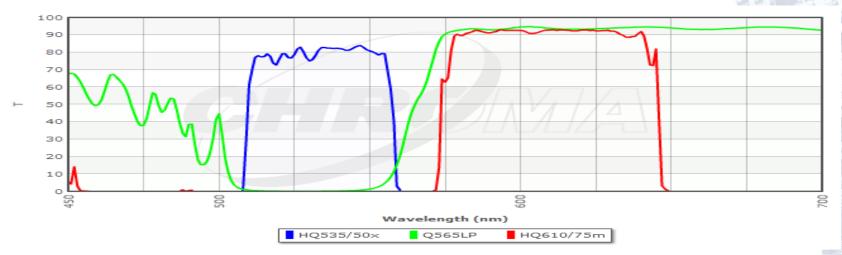

#### FTIR Scan of Various Flux Types

Utilize FTIR , GC-MS, HPLV, and Electrical Test to characterize effects of Organics on HDI field performance

Inspection Techniques (Visible, IR, UV, etc.)

- ➢ Visible

- Infrared (Near, Mid, Far)

- Ultra-Violet (Near, Mid, Far)

Inspection Techniques (Visible, IR, UV, etc.)

### Questions / Thoughts

# We would like your input & feedback to minimize oversights in this study?