### IPC Technical Conference

Yield Enhancement in BGA

Substrate Manufacturing and IC

Packaging

### Agenda

- Difference between AOI and AFI.

- The Challenge in AFI.

- Design elements in the Inspection.

- Typical defects.

- The 3rd Dimension- BGA Substrates for FC with CB.

- The Challenge in Technology and DI.

#### What is AFI

- Definition of HDI.

- AFI Automated Final Inspection.

- How is it done today.

- Why is it not implemented in the PCB Market, final inspection.

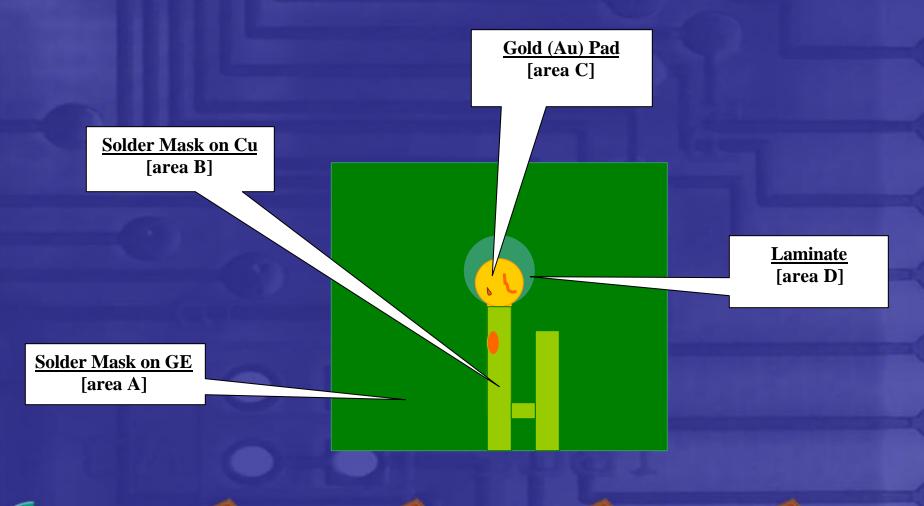

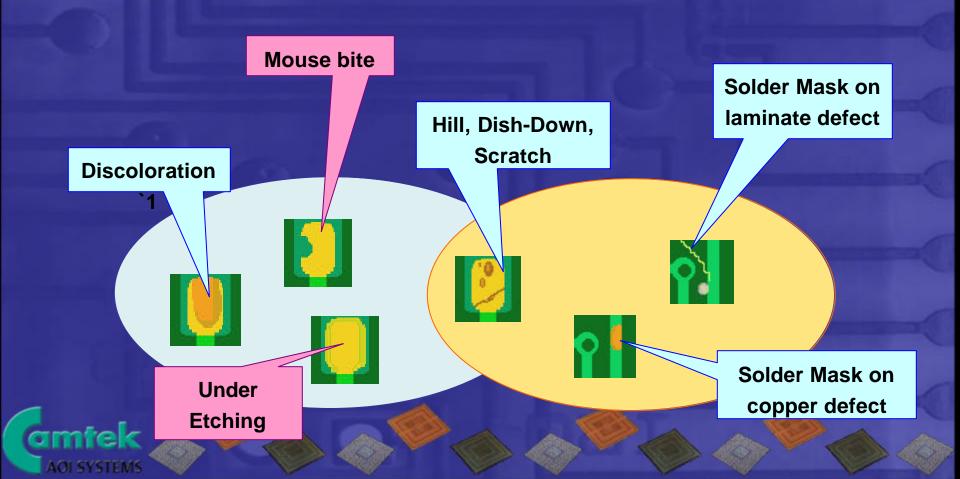

### Interconnect – Surface Defects

- In Process.

- Strive to isolate Cu and laminate.

- DRC and CAM Interconnect.

- No attempt to identify Surface.

- Ignore surface anomalies.

- Final or Pre-Assembly.

- Inspection of Interconnect Pads.

- Flaws in Gold, OSP, SM, plating, Balls and Bumps.

- Flaws that may pass assembly, but fail in service life.

### Interconnect - Surface Defects

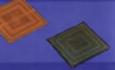

#### Inspection through Process

#### The Unique Challenge of AFI

- AFI looks for interconnect surface defects, resulting from process or handling issues.

- Correlating the Type, Size, Design Location and extent on the interconnect reliability. Not Obvious.

### The Unique Challenge of AFI (2)

- The Inspection needs to differentiate all surface defects from their background.

- \*The need for Intelligence that would qualify their significance according to a pre set customer spec.

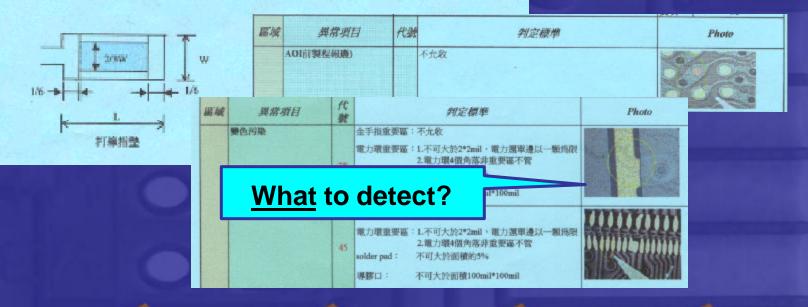

#### Customer Criteria

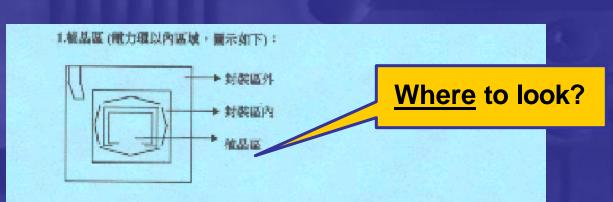

2.打練區定義 (未特別規定時,皆依此規範檢驗):

### The heart of things

- Problem Subjective judgment due to uncertainty in defect reporting, due to non-deterministic defect description in specs and variety of defects.

- The Ideal The Inspection tool should effectively, implement qualities criteria, and replace human decision.

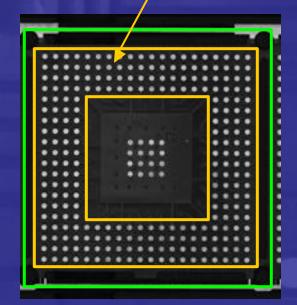

### Design Elements of Inspection

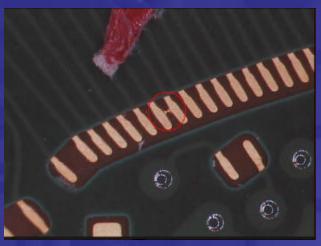

**BGA Gold pads**

Wire bonding Gold pads

**Power lines**

Solder Mask area

"Mold gate"

Die Bonder Vision fidutcials

### Different Areas of Inspection

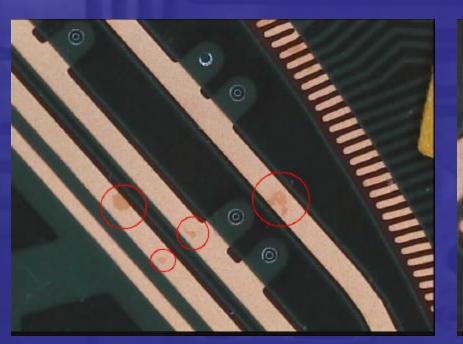

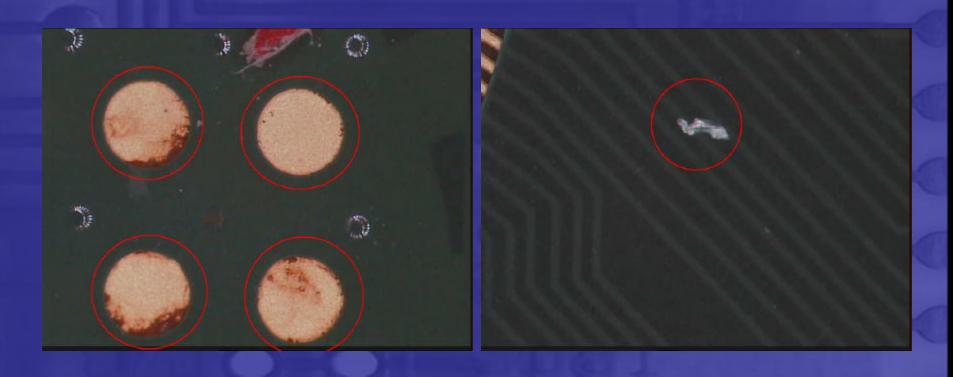

#### Discoloration

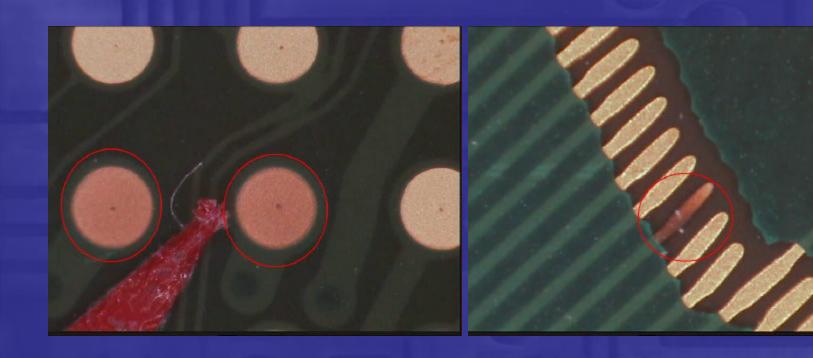

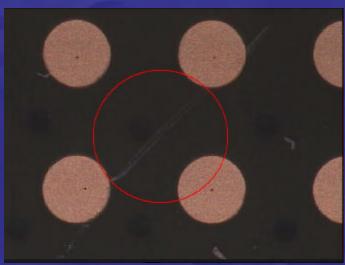

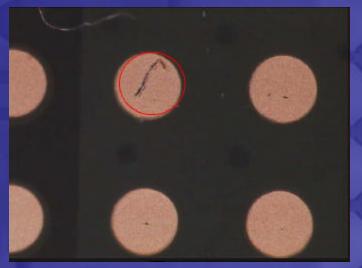

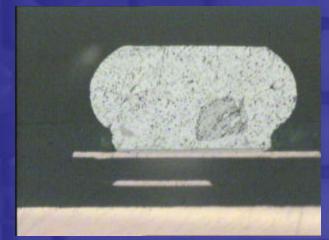

### Contamination and Foreign Materials

#### Dish-down and Dents

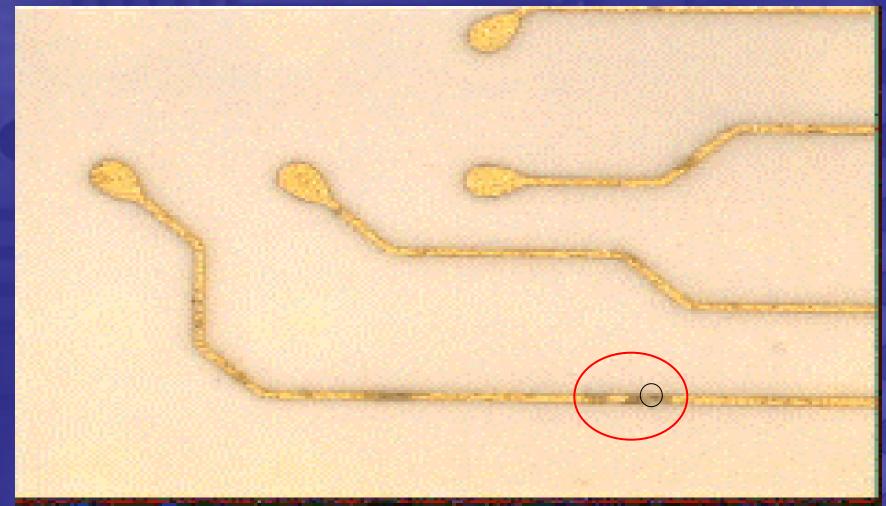

### Bare Copper / Skip Plating

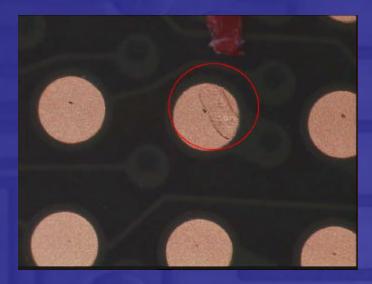

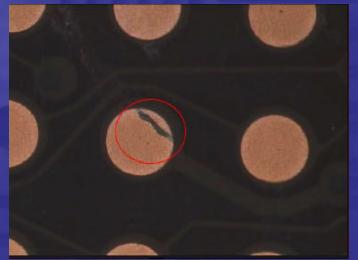

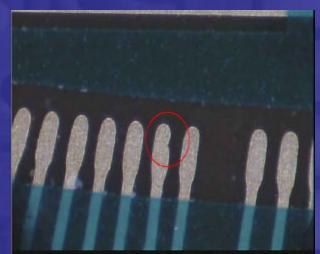

#### Scratches on Gold and SM

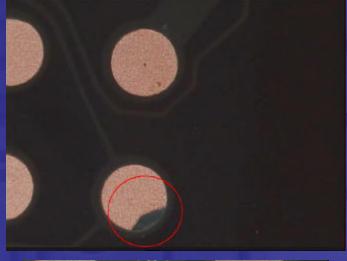

## Solder Mask violations and Solder Mask peeling

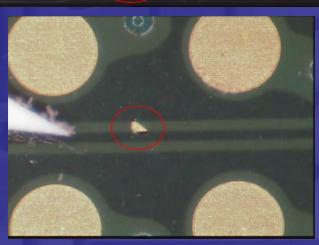

### Extra Copper/Gold and Shape violations

### Sorting AFI Defects

Pegasus provides defects <u>Auto Classification</u> capability and SPC analysis

# The Third (3<sup>rd</sup>) Dimension of Flip-Chip

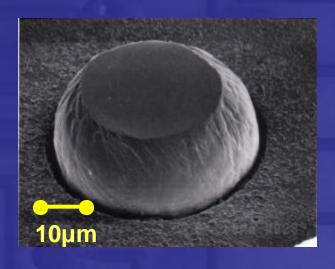

### **Bumps on Substrates**

**Flattened Solder Bump**

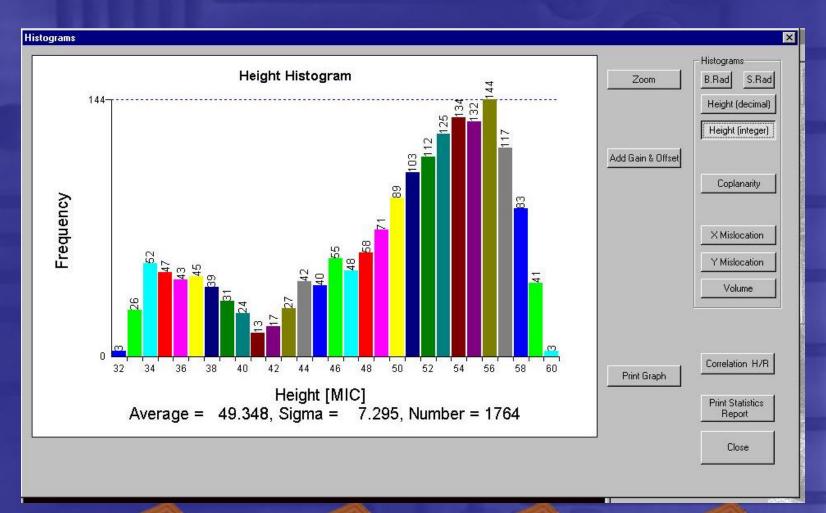

#### SPC - Bumps Height Metrology

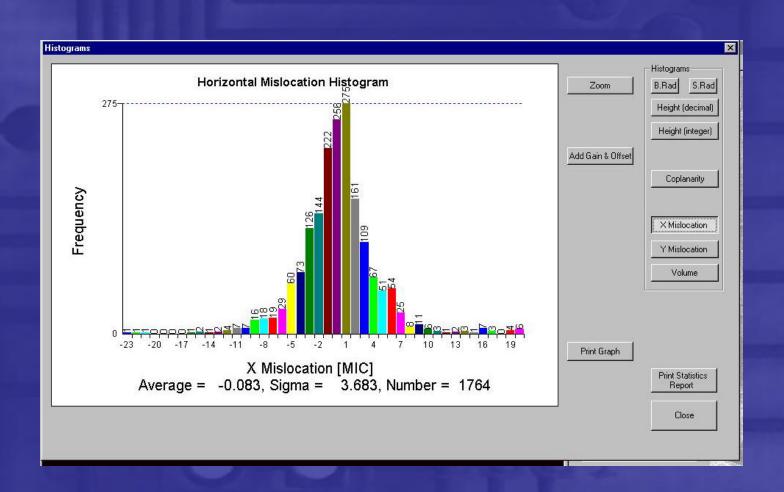

### SPC - Wrong Location in X axes

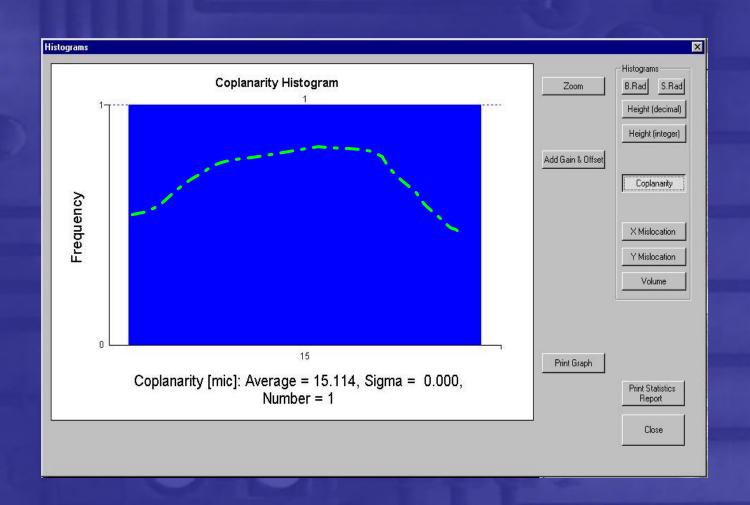

### **SPC - Bumps Co-Planarity**

### SPC - Substrate Warpage

# The challenge in the Technology

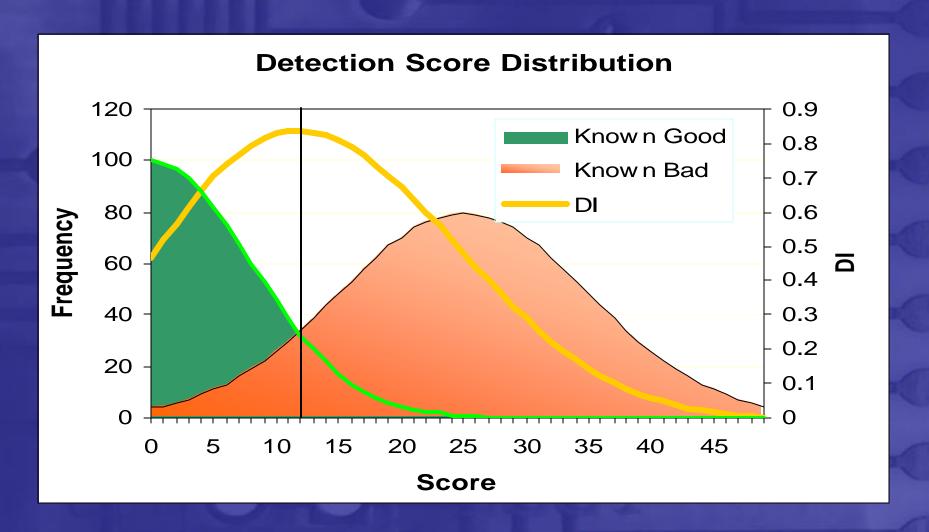

### The Trade Off between Detection -- False Alarm

$$DI = \left[1 - \frac{FA}{TC}\right] \left[1 - \frac{MD}{KD}\right]$$

DI – Detection Index

FA – Number of False Alarm Calls.

TC – Total number of calls.

MD - Number of Missed Defects.

**KD – Number of Known Defects.**

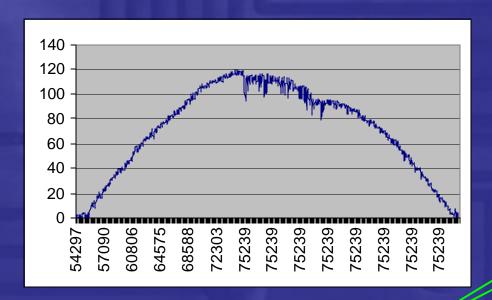

#### **Detection Score Distribution**

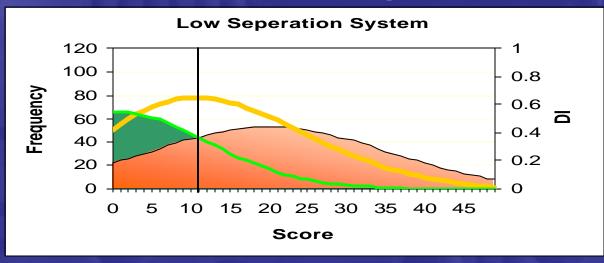

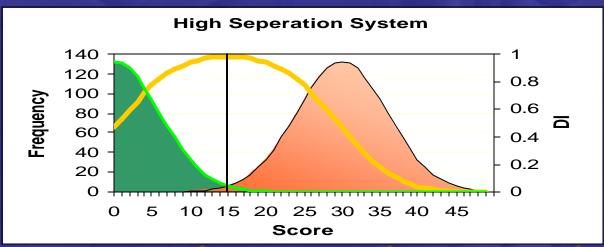

## Low - High Separation System

### Thank You!

Yossi Pinhassi Udi Efrat Moti Yanuka