# Solid, Reliable and Planar Microvias Using (Mostly) Conventional Multilayer PCB Technology

Ormet Circuits, Inc. 2236 Rutherford Rd. Suite 109 Carlsbad, CA 92008 760.931.7090 www.ormetcircuits.com

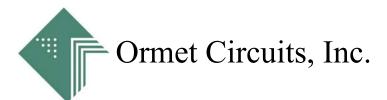

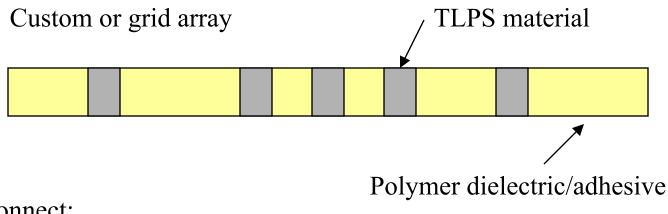

#### **TLPS Composites: Conceptually**

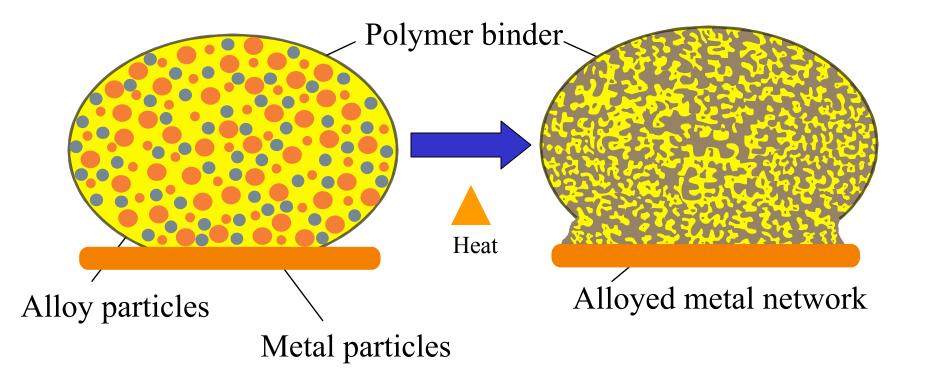

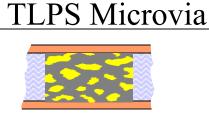

# Conductor materials do not remelt -Transient Liquid Phase Sintering (TLPS)

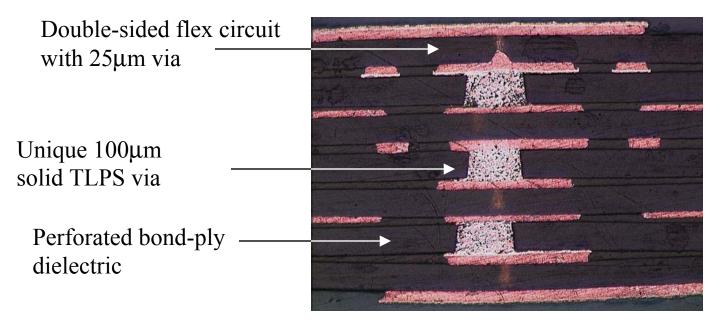

# **Unique TLPS Microvia Technology**

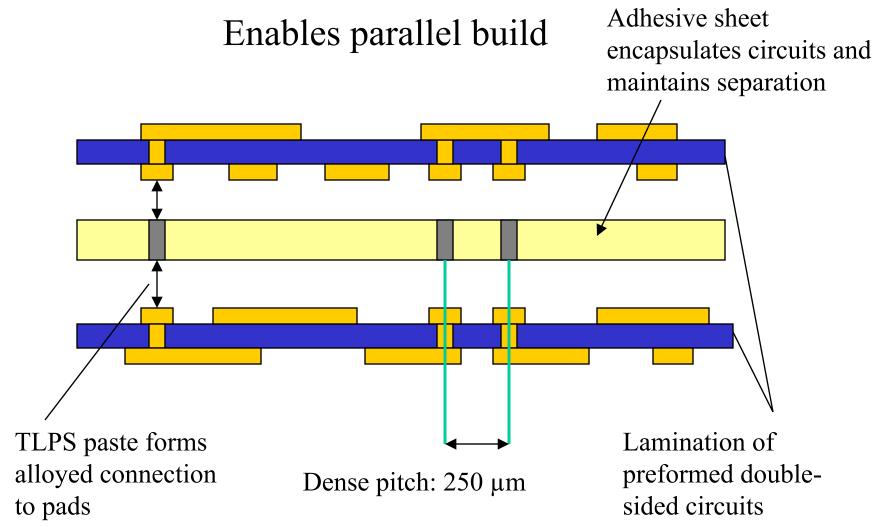

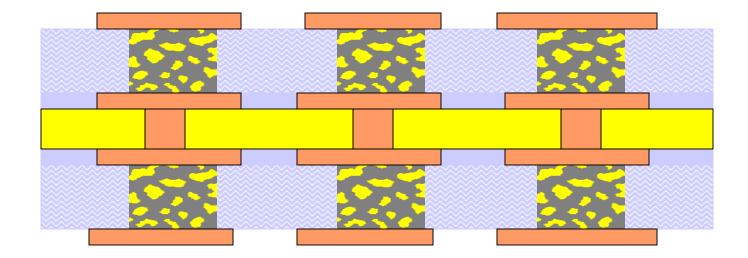

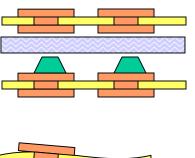

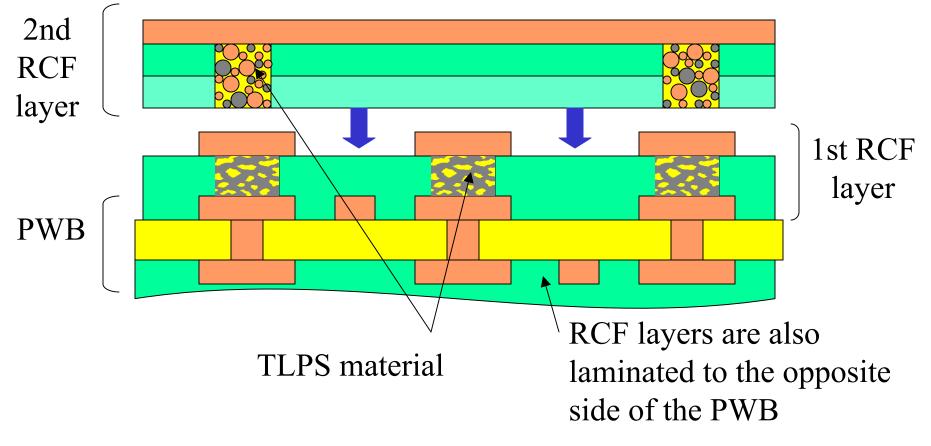

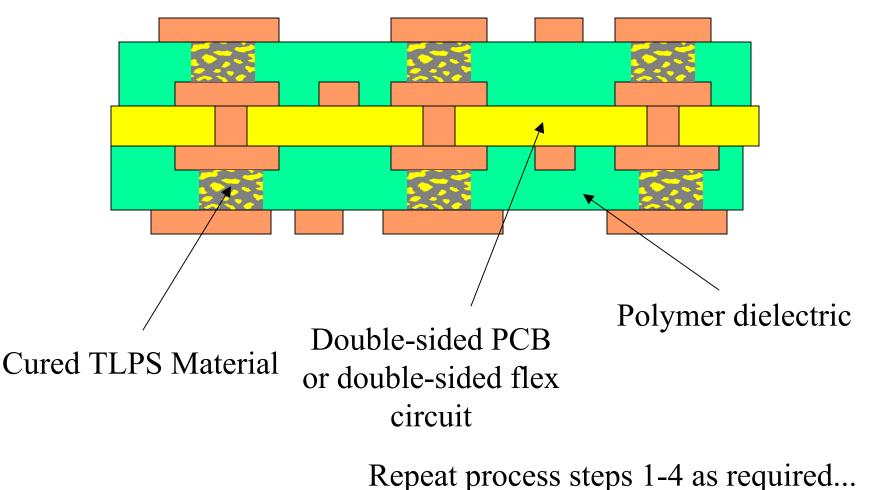

# A simple solution for layer-to-layer vertical interconnect

Connect:

- •Conventionally produced double-sided circuits

- •Dissimilar circuit types

- •Dissimilar density circuits

- •Double-sided flex circuits

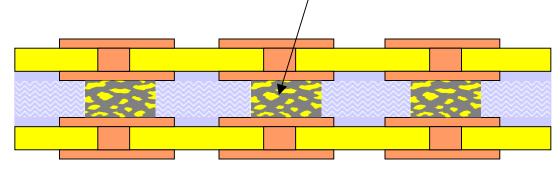

# **Unique TLPS Microvia Technology**

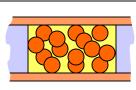

## TLPS Composite Filled Bond-Ply

# Advantages of this TLPS Microvia Technology

- Buried via layer-to-layer connections can be made at any location

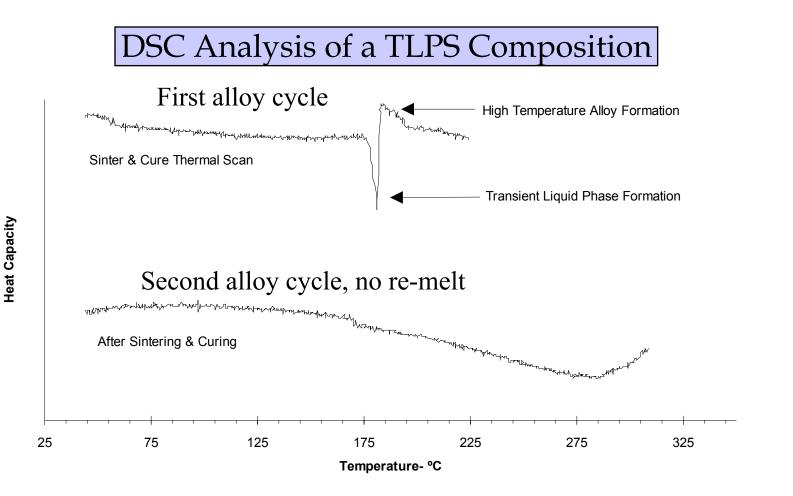

- Via diameters range from  $75\mu m$  to  $400\mu m$  ( $50\mu m$  feasible)

- Reliable, alloyed connection to the circuit pads

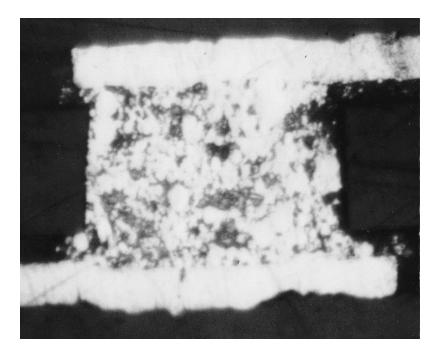

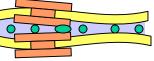

Cross-section of 8-layer multichip module

#### **Reliability Results:**

TLPS Filled Bond-Ply in Multilayer Flex Structures (125 μm vias on 200 μm pads)

- Thermal Shock: Air to Air (-55C to +150C)

- 100 cycles: Average  $\Delta R = -0.9\% (\pm 1.3\%)$

- 480 cycles: Average  $\Delta R = -2.4\% (\pm 4.6\%)$

- 1000 cycles: Average  $\Delta R = -3.2\% (\pm 3.2\%)$

- Humidity: 7 day, 85C/85 RH

- $-100 \ \mu m \ via \ in \ 4 \ layer: \Delta R = 5\% \ (\pm 8\%)$

- $-125 \ \mu m \ via \ in \ 6 \ layer: \Delta R = 6\% \ (\pm 20\%)$

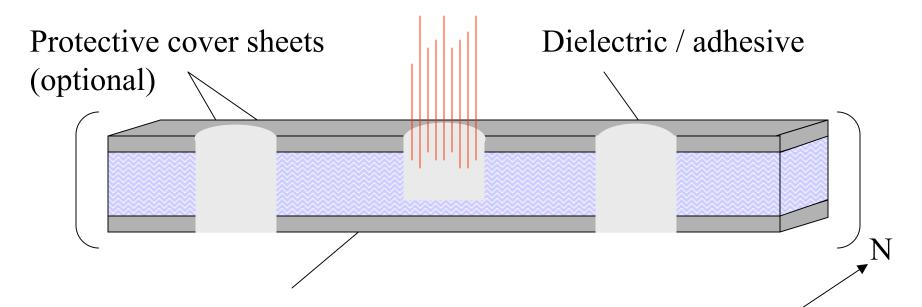

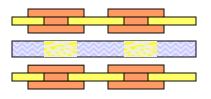

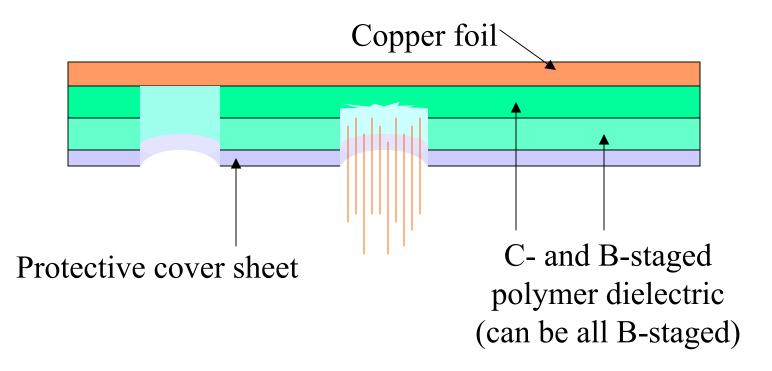

# **Unique TLPS Microvia Process: Step 1**

#### **Prepare Dielectric / Adhesive Sheet**

Laser or mechanically drill holes

Stack multiple plies for drilling depending on method/design

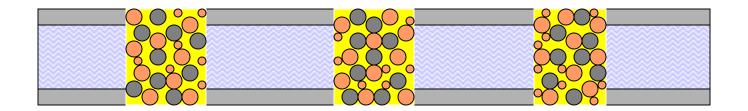

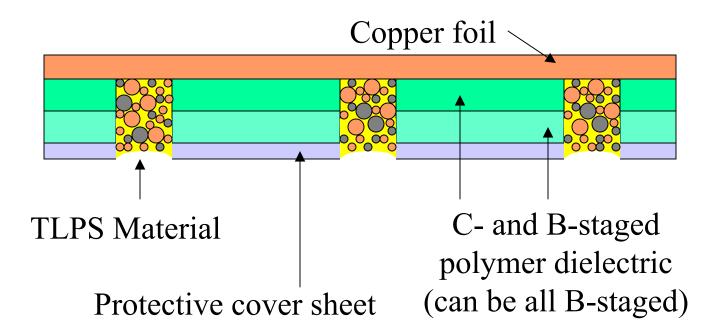

#### **Unique TLPS Microvia Process: Step 2**

#### Fill Holes with TLPS material

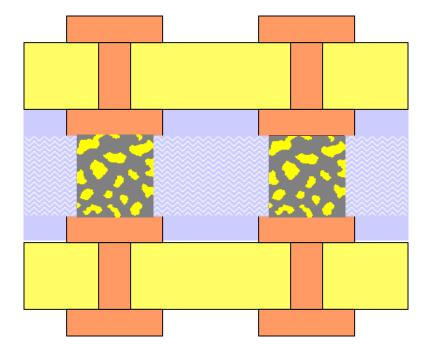

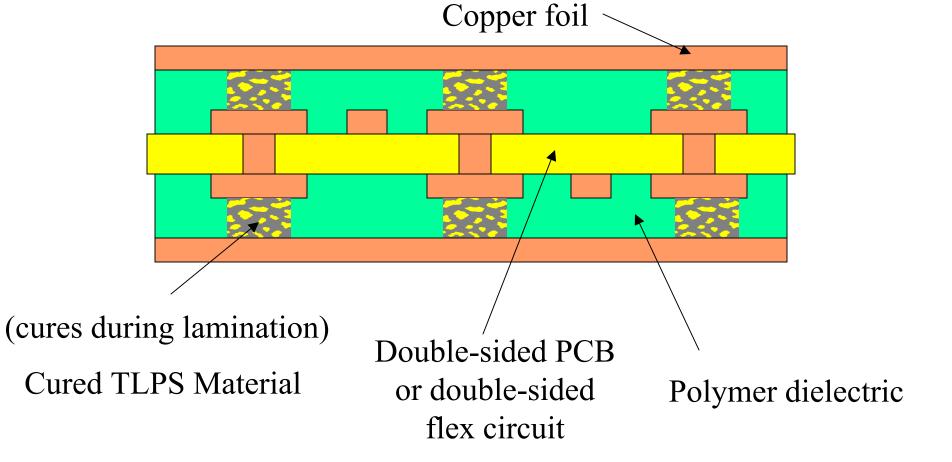

# **Unique TLPS Microvia Process: Step 3**

#### Lamination

Protective sheets removed before lamination

Dielectric reinforcement maintains uniform separation

TLPS material co-processes under standard lamination conditions

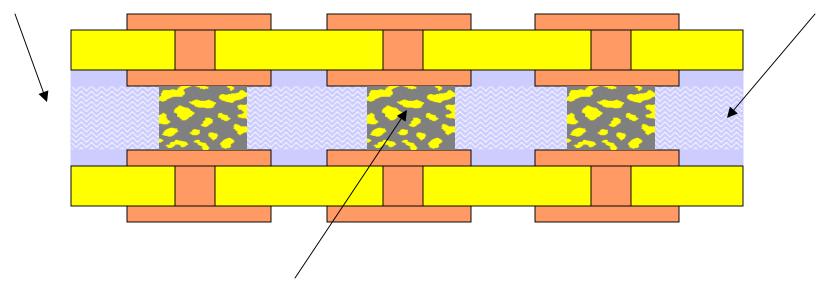

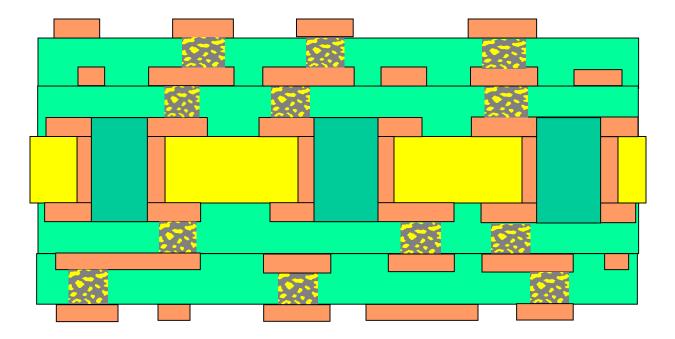

# **Unique TLPS Microvia and FR4 PCE**

TLPS material co-processes under standard lamination conditions

14-layer board made from seven 2-sided boards

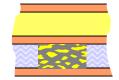

# **TLPS Microvia Process: Step 3 (alternate)**

#### Lamination with Foil

Dielectric reinforcement Protective sheets removed before lamination maintains uniform separation TLPS material co-processes under standard

lamination conditions

#### **TLPS Microvia Process: Step 4 (alternate)**

# **Etch Foil**

# Unique TLPS Microvia Advantages vs. the Competition

| 88 |  |

|----|--|

|    |  |

|    |  |

|    |  |

Others

#### **TLPS** Advantages

Consistent and reliable alloyed connections - not just particle contact

Compliant vias that won't 'punch through'

Via layers fabricated in parallel with circuit layers

Reinforced bond-ply gives consistent dielectric separation (However, TLPS is also compatible with single and dual stage RCFs.)

Foil patterned after lamination

#### **Process step 1: Laser drill through polymer**

#### **Process step 2: Fill with TLPS Material**

#### **Process step 3: Laminate to circuit board**

#### **Process step 4: Etch copper circuit**

#### 2+2+2 Construction (PCB core)

# Summary

- TLPS Microvia is a proven, reliable technology for HDI.

- TLPS Microvia has been adapted for compatibility with PCB materials and typical lamination conditions.

- TLPS microvias will not remelt and are alloyed to the capture pads.

- Solid TLPS microvias do not capture contaminants, do not distort outer layer topography, and can be stacked.

- TLPS Microvia is a patented technology currently available for specific application development and license.