### **Building HDI Structures using Thin Films and Low Temperature Sintering Paste**

### **Catherine Shearer, James Haley and Chris Hunrath**

Ormet Circuits Inc. - Integral Technology California, USA chunrath@Integral-HDI.com

### Abstract

Circuit complexity and density requirements continue to push PCB fabrication capability limits. Component pitch and routing requirements are continually becoming more aggressive and difficult to achieve in good yield with current fabrication strategies. The trend is to bring the PCB closer to the density requirements currently required for semiconductor packaging. The ability to place interconnecting vias in any location on any layer is crucial to PCB fabricators in meeting this high density interconnect (HDI) trend.

The two fundamental elements in any type of PCB, conductors and dielectrics, both have to be considered when building "any layer" HDI. These PCB's have specific challenges for processing while maintaining thermal and electrical performance. Careful consideration of the interplay of the fundamental elements is critical to fulfilling all of these requirements. New methods and materials designed specifically with these challenges in mind are becoming available for building HDI

Using materials specifically designed for HDI PCBs can significantly reduce the challenges producing these boards. However, along with easing the challenges of fabrication, these materials must also demonstrate the right combination of properties to meet electrical and thermal requirements while also being reliable. Validation of these new technologies is currently underway.

### Background

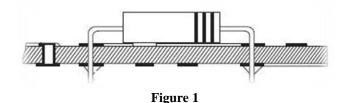

Back in the day, just taking advantage of double-sided-clad increased density. Being able to route traces in the same location on each side of the PCB, interconnected with plated through holes, added significant density compared to a single sided PCB. (see figure 1) Logically, as chips became more powerful with more I/Os, adding layers became the natural progression.

However HDI is not just about layer count. Adding layers has a diminishing return as the through holes and vias grab valuable real estate. Buried vias and "subs" provide an intermediate solution to higher density requirements, but these techniques greatly increase the process complexity and time in the PCB fabrication facility.

As the high density trend marched onward, build-up or sequential lamination became popular as laser drilling and better plating technology enabled blind microvias. Sequential build up has the big density advantage of placing vias anywhere on any layer, but each layer has the process steps of an individual PCB. Lamination and plating capacity must be greatly increased to accommodate this solution. (see figure 2)

Figure 2

There is a growing gap between cost-effective PCB manufacturing and HDI PCB requirements. New technologies – materials and methods - are needed for the industry to meet current and future demands.

#### Introduction

What if vias could be formed without plating? More importantly, what if the vias could be formed <u>before</u> lamination? If vias could be made this way, trips through plating and lamination can be greatly reduced. Making this possible would require the insertion of a conductor into vias in the dielectric layers between the individual circuit layers.

This can be done several ways. Some methods do this to C-stage (cured) dielectrics and some to B-stage (uncured) dielectrics.

Ideally, the conductive material would be in liquid or paste form so it may be inserted into the vias after drilling, but before lamination. In applying the ink or paste, measures must be taken to ensure that the surface of the dielectric is not contaminated with conductive residue that can lead to electrical leakage, migration, etc.

Creating the interconnecting vias before lamination can greatly simplify the PCB manufacturing while still enabling via placement anywhere on any layer. In addition, formation of conductive vias prior to lamination may be combined with traditional processes for circuit formation and lamination, thus allowing the most efficient and cost-effective use of the PCB shop.

### **First Element: The Conductor**

#### Sintered Vs. Non-Sintered

Sintering refers to a process where a mixture of particles is fused together, usually thermally. Sintering mixtures can be used for structures, dielectrics as well as conductors.

Conductive sintering products have been used in electronics for some time with ceramic thick film technology (cermet). Cermets require high temperatures (>800°C) for sintering and often ceramic substrates as the dielectric base material.

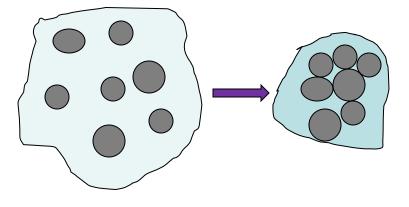

Non-sintering conductive pastes based on polymers – rather than ceramics - have been used with PCB materials as well as in printed electronics. These polymer thick film (PTF) materials are typically uncured liquid polymers, usually epoxy or acrylic based, filled with conductive particles. As the polymer cures and shrinks, the particles come in to contact with each other and the substrates making the connection. (see figure 3)

Figure 3

PTFs have the benefit of low cure temperatures and are compatible with all kinds of polymer substrates.

Two challenges with PTFs are changes in conductivity due thermal expansion and oxide on the surface of the individual particles. Silver is a popular choice for the latter because its oxide is reasonably conductive.

The resistance behavior of PTFs is altered by temperature changes in reliability testing as well as in-service conditions. The need to pass traditional reliability testing therefore makes it challenging to implement PTFs in z-axis interconnect..

#### **Transient Liquid Phase Sintering**

TLPS (Transient Liquid Phase Sintering) takes advantage of the fact that a liquid metal (e.g. tin) will interdiffuse and with a non-molten metal (e.g. copper) to form a solid metallurgical joint at relatively low temperatures. This type of interdiffusion – in this case between copper and tin – results in a metallurgical bond between the two metals that is stronger than a mere layer-to-layer interface.

Interdiffusion between metals has long been used in electronic assembly to create strong, environmentally robust electrical interconnects. Solder joints of all kinds rely on a copper/tin diffusion and intermetallic formation to provide a strong, lasting bond.

A conductive paste may be formulated with TLPS characteristics so that sintering of the metals in the paste is possible at normal PCB laminating temperatures (as low as 180°C). The use of tin in such a TLPS paste has the added benefit of forming metallurgical bonds not just through the bulk of the paste interconnect, but also with the copper foil circuitry – just like solder would. (See figure 4) However, unlike solder, the TLPS paste will not wet beyond the vias footprint and will not remelt during subsequent processing. Thus, the TLPS-paste-filled-via metallurgically ties the circuit layers in the Z-axis during standard lamination conditions. Like plated vias, TLPS paste interconnects provide a continuous metallurgically bonded electrical pathway.

Figure 4

Within the bulk of a TLPS paste via, copper and alloy particles 'micro-weld' together to form a network of copper particles joined by copper-tin intermetallics and alloys. The re-melt temperatures of the various phases are well above reflow temperatures and for all intents and purposes, non-reversible in the PCB. (see Table 1)

| Table 1             |               |               |  |

|---------------------|---------------|---------------|--|

| Sintered            | Melting Point | Percentage of |  |

| Interconnect Matrix | (°C)          | Matrix        |  |

| Components          |               |               |  |

| Cu                  | 1085          | >85%          |  |

| Cu6Sn5              | 415           |               |  |

| Cu3Sn               | 640           |               |  |

| Bi                  | 271           | < 15%         |  |

TLPS pastes can provide the via conductor stability necessary to enable a change in the PCB manufacturing sequence. Because the bonds are metallurgical and not just relying on particle contact, they have the ability to meet traditional electrical and thermal reliability requirements.

This opens many possibilities in PCB design and fabrication.

### **Second Element: The Dielectric**

TLPS pastes have been used successfully with both C-stage and B-sate dielectrics. Using B-stage dielectrics have the benefit of creating the z-axis connections while bonding layers together. Of course a B-stage dielectric becomes a C-stage dielectric once laminated and cured. Consideration must be given to the flow characteristics of this layer for two important reasons. First, any resin that might flow and travel between the innerlayer copper foil surface and the TLPS paste before the intermetallic is formed will prevent the best possible interconnect. Second, flow of the resin may push the TLPS particles before they are locked in place.

Successfully controlling these two characteristics comes from understanding and managing the process, but the right choice of materials can lead to high repeatability and high yields.

### **B-Stage Materials For Tlps Paste Z-Axis Interconnects**

While flow of the B-stage resin may cause sintering issues, it is essential for layer-to-layer bonding. Loss of adhesion as well as lamination voids will cause issues in the PCB structure, and any successful HDI system must be free of these two defects.

Ideally, a B-stage material well suited for a TLPS interconnect would flow in the z-axis only. This would allow bonding and in-fill between the copper circuits without pushing the paste around laterally before sintering. Such a material would be impossible to make; however, it is possible to manage the x-y flow and make very reliable connections.

Standard flow prepregs rely on the glass fabric for z-axis thickness control and for resin retention to prevent voiding. They are the industry standard building block, even in HDI build-up methods.

Using standard prepregs with TLPS requires a greater understanding of their flow characteristics because of the potential for the prepreg resin to alter the shape or position of the TLPS-paste-filled-via as it flows. Things like heat rise and shelf life become even more critical.

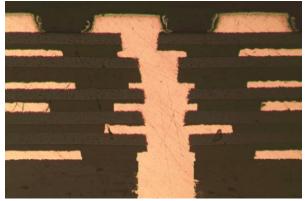

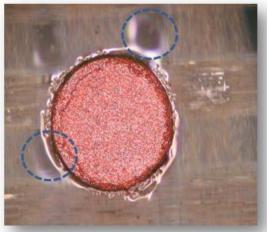

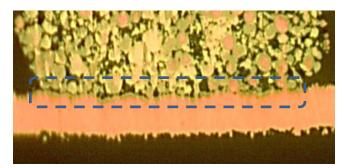

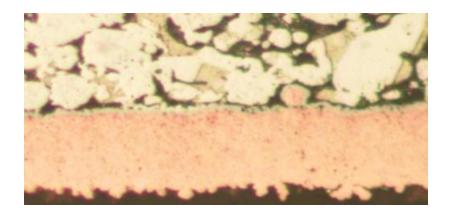

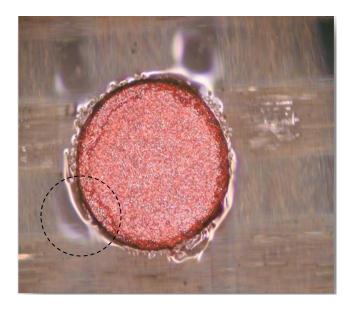

HDI builds often require thinner, low glass/resin rich prepregs. This has the advantage of better laser drilling and better fill in fewer plies; however, the higher resin content has a disadvantage in the TLPS paste interconnect process. The higher proportion of resin exacerbates the flow problem. Not managed, the flowing resin can push the paste, even to the point of sweeping it away. Figure 5 shows a laser drilled, paste filled via before lamination. Note the gaps in the glass fabric.

Figure 5

These areas are resin rich and can move the paste in the via and potentially interfere with sintering quality he formation of a continuous metallurgical network during lamination.

In order to reduce the need to pre-engineer the process for suitable flow characteristics, no-flow prepregs may be substituted for standard prepregs in the TLPS paste via process. No flow prepregs, more accurately called "very low flow" prepregs, do not rely on the glass as much for flow control. This offers better predictability in lamination and will help preserve the shape and position of the TLPS-paste-filled-via before sintering.

No-flow prepregs come in many different varieties from epoxy to polyimide, lead free compatible and so on. These materials need to be studied individually for compatibility with both the fabrication process and the PCB requirements, but may offer many opportunities for straightforward implementation with TLPS interconnects.

### **Films For Tips Interconnects**

Non-glass reinforced bonding films provide many advantages for HDI both in fabrication and signal integrity.

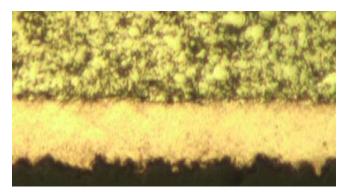

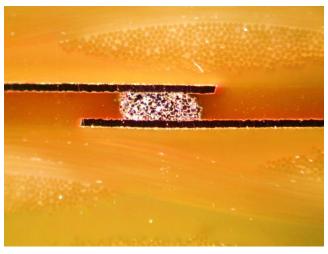

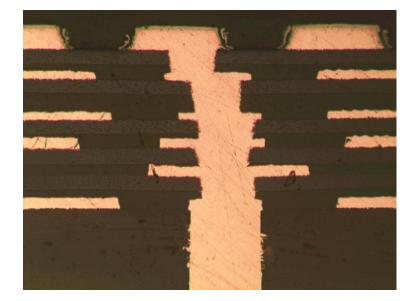

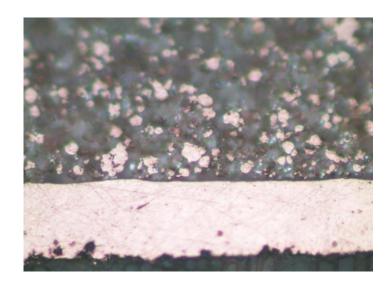

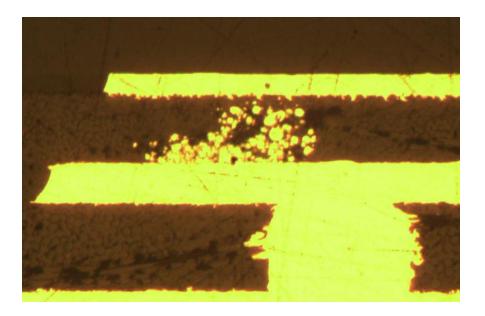

Laser drilling B-stage materials is not normally done, but is required to take advantage of the pre-lamination via formation sequence. With glass fabric materials, the ends of the fibers tend to melt, forming "slag" droplets at the ends of the bundles. (see figure 6)

Figure 6

Films tend to laser drill better, even in B-stage form. This is due to a uniform composition - all polymer instead of polymer plus glass. The type of laser used needs to be matched to the film as optically transparent films do not respond well to UV laser energy.

Many bonding films are available to the industry for flexible PCB's. These films are designed to be flow-reduced because it is common to machine the film prior to lamination. This kind of flow characteristic is very good for TLPS paste. Unfortunately, flex films contain one or more plasticizers which not only impart flexibility, but are integral to the flow control. Many plasticizers soften readily with heat and undergo large amounts of thermal expansion. Neither of these is desirable in HDI stack up structures.

Considering the requirements for HDI PCBs implementing TLPS interconnect, it is possible to develop a film without the plasticizers needed for flex. HDI PCb's are free from the dynamic bending requirement. This opens up some interesting formulation possibilities.

The new film concept is to replace the "rubberized" matrix with a polymer matrix that will behave more like the glass weave, but without the negatives. A proprietary high-temperature polymer is crosslinked to better mimic woven glass without the differential lasing characteristics, poor dielectric performance and resin wetting issues common to glass. This matrix is combined with a primary high-temperature B stage resin with high bondability, long shelf life and will not advance during via formation and TLPS paste installation steps. This system can provide ease of use with interconnecting TLPS pastes, offering process latitude and thermal reliability.

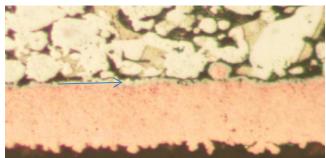

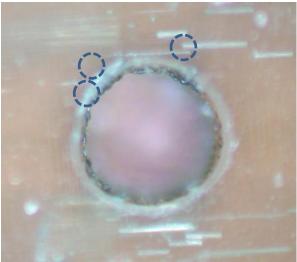

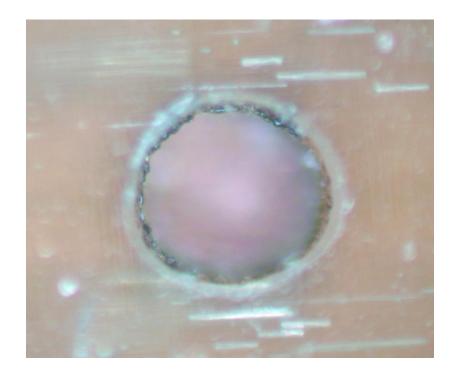

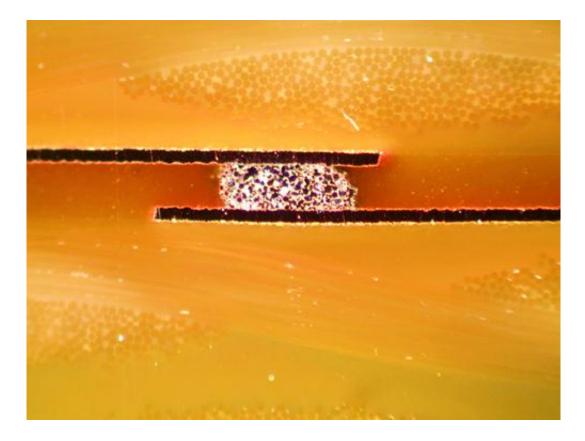

By designing the dielectric film with both the paste interconnect process and the HDI PCB form-factors in mind, implementation of TLPS z-axis interconnect becomes straightforward. The entire materials set has been designed to work together, with minimal impact to standard PCB manufacturing processes, and to support thin high-density PCBs with high electrical performance characteristics. With this film design, proper flow control of the resin can be tailored to the TLPS paste to maintain the unsintered paste in a well-defined via shape and not allow resin interference with the formation of a metallurgical bond to the copper pads. (see figure 7) The interconnect is therefore dense, continuously metallurgically interconnected from pad-to-pad, and consistent from via-to-via.

Figure 7

The film system is not dependent on glass fabric, thermal aging, etc. for flow control so the resin effect on the TLPS via is predictable and consistent over a long shelf life. Also, the film is a stand-alone dielectric without the electrical performance and thickness constraints imposed by glass, but with thermal properties similar to a lead free compatible glass reinforced system. The TLPS interconnects can therefore be short; in addition to the capability of placement anywhere in the PCB, and the overall structure can be very thin.

The intended result of this system approach is an HDI process that's less demanding on the PCB shop while providing the same reliability as copper plated and filled microvias.

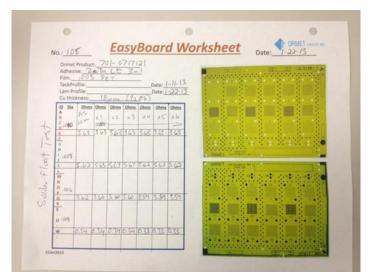

This new film design was put into a test vehicle to examine the effects of thermal shock on the TLPS z-axis interconnects. (see figure 8)

Figure 8

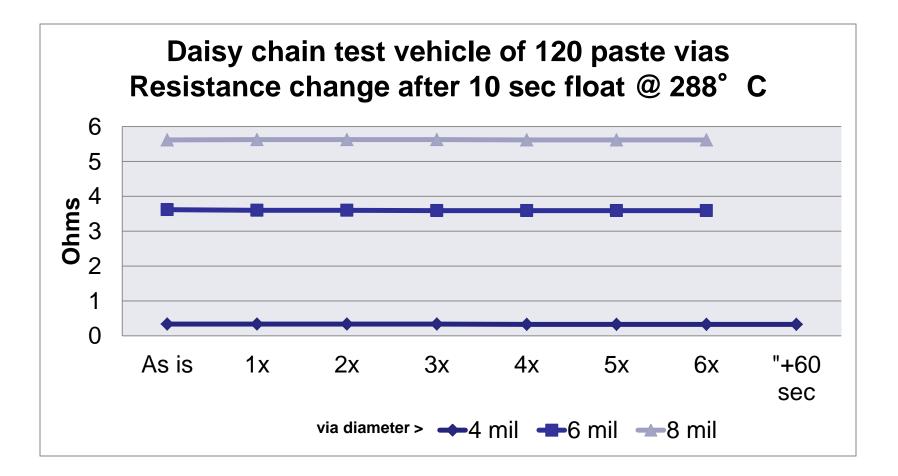

Above are some resistance measurements on a "daisy chain" test vehicle with six 10 second solder floats at 288°C. (see figure 10)

4, 6, 8 and 10 mils vias were tested. 100% of the interconnects had very little or no change in resistance. The 4 mil via daisy chain was put back in the 288° C solder for a full minute and re-checked for resistance, again, no change.

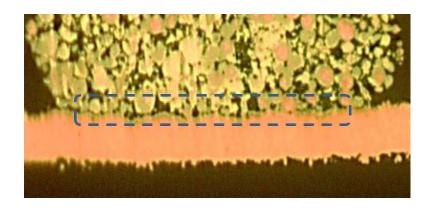

Figure 9 shows a continuous alloy formation with the copper foil at the bottom of the via.

Figure 9

### Conclusion

Combing a TLPS paste with a film that is engineered without the constraints of flex can produce thermally reliable z-axis interconnects. The TLPS paste offers a plating like metallurgical bond to the copper innerlayers while the film allows proper sintering and controlled z-axis expansion. Together these materials give the PCB manufacturer ease of implementation of high reliability sintered-paste interconnects and more construction options for HDI structures.

### Building HDI Structures using Thin Films and Low Temperature Sintering Paste

2013

James Haley – Ormet Circuits Catherine Shearer – Ormet Circuits Chris Hunrath – Integral Technology

2013

ATION that INSPIRES INNOVATION

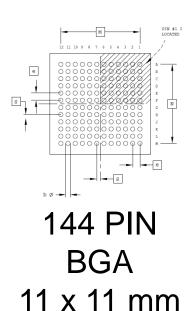

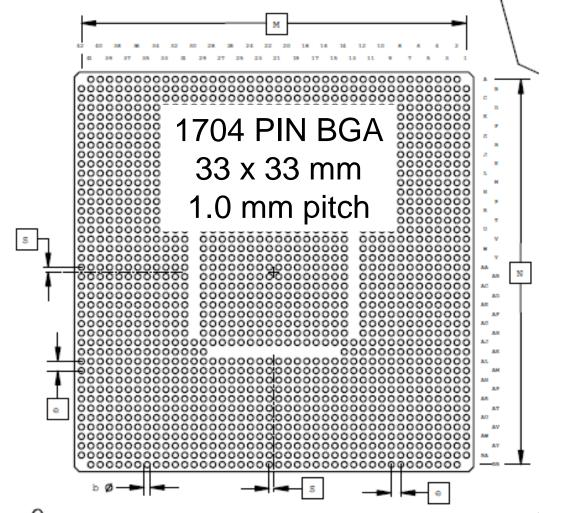

## HDI- Driving more connections

0.5mm pitch

# Sequential Build-Up

- Structure is layered 1 at a time on each side.

- Allows unrestricted via placement.

2013

Requires repeated trips through the PCB manufacturing process.

## Changing the Build-Up Sequence

- Via formation before lamination

- Buried vias

- Copper plated through holes and vias.

- No connections formed during the lamination cycle.

- Z-axis connections other than plated copper

- Conductive material is applied to individual layers.

- Connection is made during lamination.

- There are several methods and materials to do this.

### **Conductive Pastes for Z-axis connections**

Many different types are curable at PCB temperatures.

- Particle to particle connection made when polymer matrix cures and shrinks.

- Most do not sinter.

## Sintering

• Sintering refers to a process where a mixture of particles is fused together, usually thermally.

- Thermal sintering usually happens at high temperatures (>800°C).

- Sintering mixtures can be used for structures, dielectrics as well as conductors.

- If sintering can be done at temperatures compatible with organic PCB laminating temperatures, strong bonds can be formed.

# **Transient Liquid Phase Sintering**

- Transient Liquid Phase Sintering takes advantage of the fact that a liquid metal will interdiffuse with a non-molten metal to form a solid metallurgical joint at relatively low temperatures.

- Interdiffusion starts at 150°C

- Well with in the range of PCB lamination.

- This type of interdiffusion in this case between copper and tin results in a metallurgical bond between the two metals that is stronger than a mere particle surface-to-layer contact.

### Sintering is not the same as melting. What happens at assembly temperatures.

| Sintered<br>Interconnect<br>Matrix Components | Melting Point<br>(°C) | Percentage<br>of Matrix |

|-----------------------------------------------|-----------------------|-------------------------|

| Cu                                            | 1085                  |                         |

| Cu6Sn5                                        | 415                   | >85%                    |

| Cu3Sn                                         | 640                   |                         |

| Bi                                            | 271                   | < 15%                   |

## Forming Conductors in B-Stage

- Allows changes in PCB processing sequence.

- TLPS is applied to B stage layer before lamination.

- B-Stage for TLPS material needs do the following;

- Laser drill compatible.

- Maintain B stage properties through paste process steps.

- Bond and flow in the z-axis.

- Keep TLPS paste in place until sintered.

- CTE, Td compatible with lead free assembly.

**INFORMATION that INSPIRES INNOVATION**

## Standard B Stage

- Not made for B Stage processing

- Pre-tacking

- Laser drilling

- TLPS paste drying

## **B-Stage Structures**

- Glass cloth in prepreg is integral to both it's B stage and C stage characteristics.

- Allows handling of B stage form

- Controls flow and pressed thickness

- Standard processing allow opportunities for undesirable paste flow through gaps in glass.

that INSPIRES INNOVATION

- Replace the glass with a polymer matrix.

- Holds the paste particles in place until sintered (final lamination)

- Use a Second polymer to provide bonding and high temperature characteristics.

- Second polymer does not cure during initial paste processing.

- Pre-tacking

- Laser drilling

- Paste drying

**INFORMATION that INSPIRES INNOVATION**

# **TLPS Interconnect in Film**

## Metallurgical Bond to Copper Layers

2013

• Matrix keeps high temperature B stage polymer from interfering with paste/layer interaction.

TLPS Paste and Film create thermally stable structure

# Conclusion

- TLPS materials provide metallurgical bonds to both particles within the paste and the copper foil circuits of various PCB layers.

- Dielectric materials should be chosen carefully for use with TLPS pastes.

- Films can offer processing and reliability advantages if;

- Flow characteristics allow good paste sintering.

- B stage properties can be maintained through paste processing.

- Cure properties of the film provide thermal performance.

- In combination, the paste and film offer copper plating like reliability while enabling beneficial changes in HDI PCB construction.