## <u>The Coming of</u> The MultiChip Module

2013

Dieter Bergman IPC Director of Technology Transfer - Emeritus

# **MultiChip Module Status**

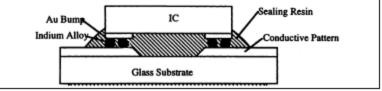

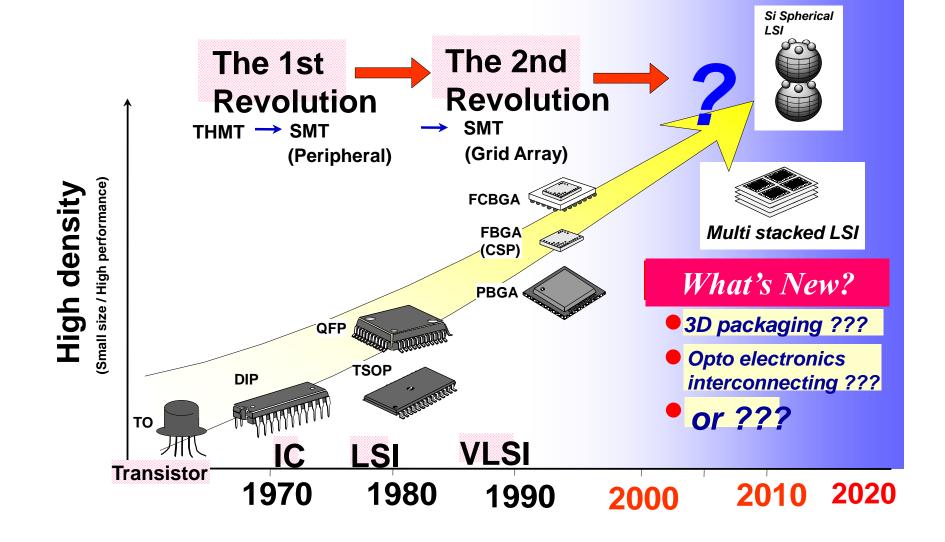

- It isn't a new idea since back in the 1980's everyone was trying to combine different components into a single package

- It started with Hybrids then different forms of SMT

- Since that time many methods have been used to bring higher operating performance to electronic assemblies

- Coined phrases such as System-in-a Package, Package-on-Package, or Application Specific I/C abounded

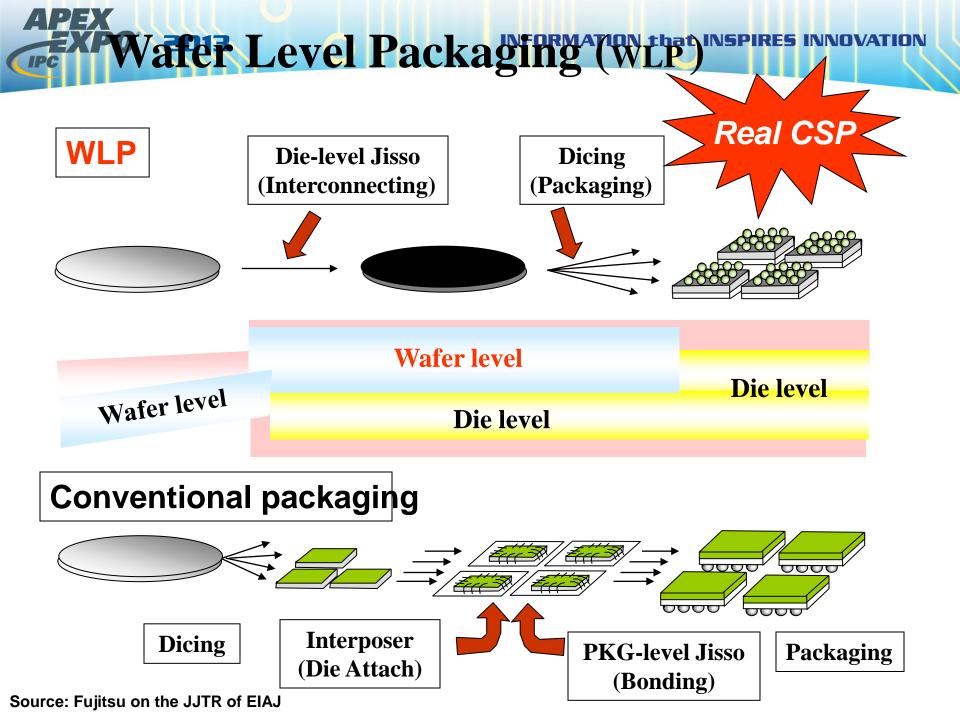

- However with the breakthrough of being able to create a Via between wafers (Through- Silicon-Vias) other new forms are evloving

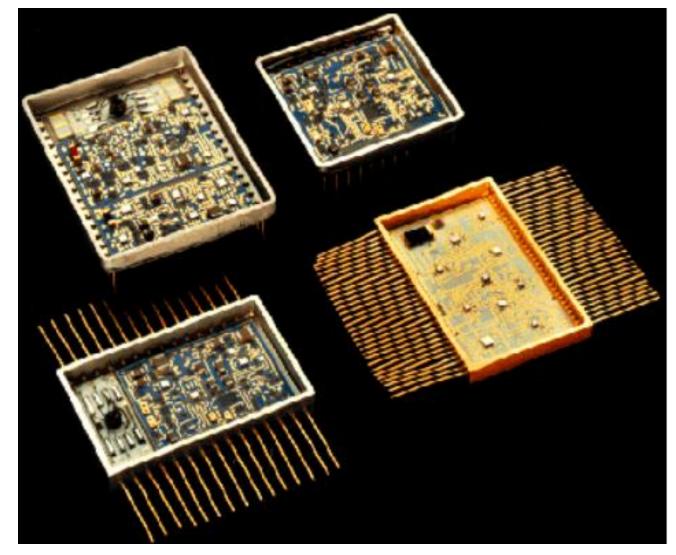

## **The Hybrid Microcircuit Era**

Many different packages and lead forms for input or output signals

2013

ION that INSPIRES INNOVATION

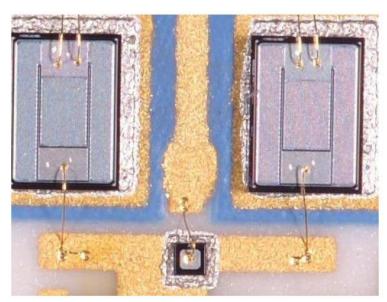

## **Design Services Helped**

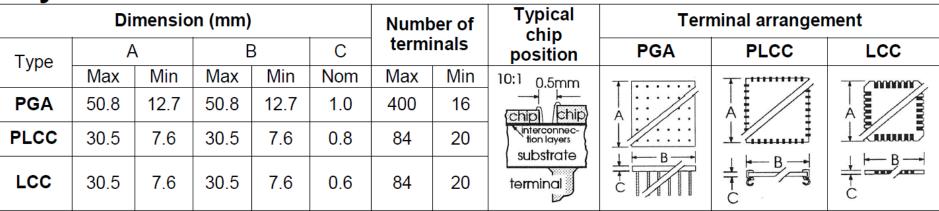

#### CERAMIC MULTI-CHIP MODULES

2013

- Signal frequencies up to 5GHZ

- Excellent thermal matching between chips

- Risk of cracks in chips eliminated

- Simple reliable construction

- Small developments costs

- The quality system correspond to ISO 9001

#### **Physical Data**

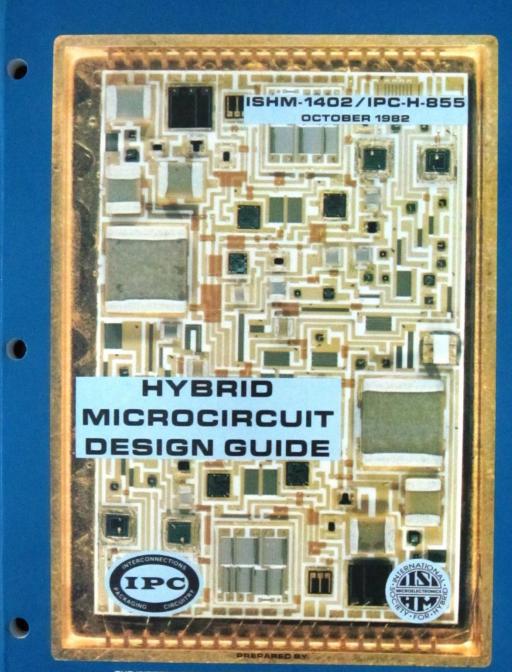

## Working Together to Establish Ceramic Reliability

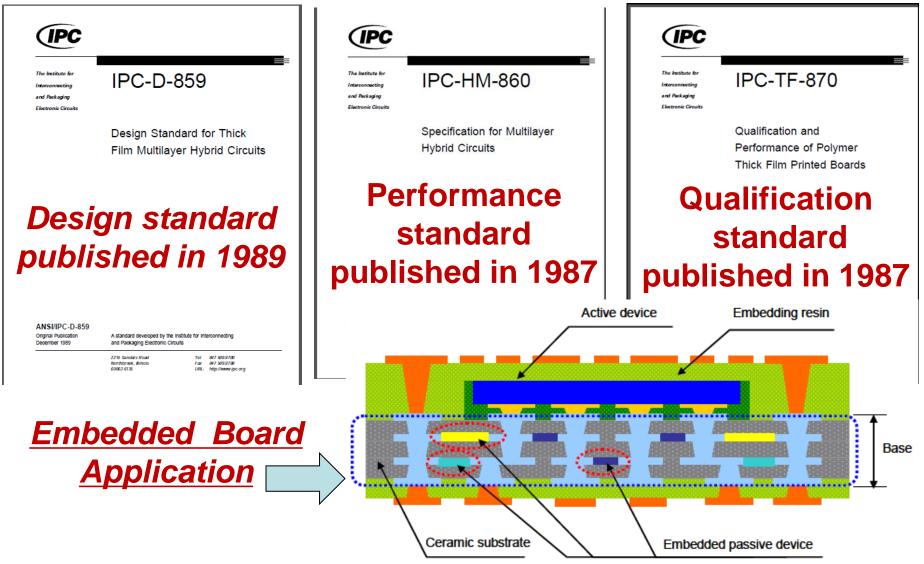

- In 1980 IPC had a Hybrid Circuits Committee made contact with the ISHM board of directors to see if ISHM and IPC would work together.

- Their Board of directors approved the idea

- As a result 5 workshops were held hosted by ISHM and IPC.

- IPC's technical editor created the review drafts from the meetings

- The results were published in 1982

One Publication effort with quantities split between IPC and ISHM with either Organization to sell to their members

2013

THE INTERNATIONAL SOCIETY FOR HYBRID MICROELECTRONICS THE INSTITUTE FOR INTERCONNECTING AND PACKAGING ELECTRONIC CIRCUITS in Today's and Future Technology

## **Surface Mounting Reliability**

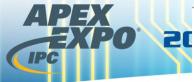

- 1985 ; US Secretary of Defense indicates "Surface Mounting is a technology at risk"

- EIA, IPC & SMTA form the Surface Mount Council made up of about 35 individuals.

- The Council never wrote standards but brought focus on what was needed.

- They published their first status and Action Plan in 1987

## **Council Membership**

- The Surface Mount Council is made up of key industry representatives dedicated to promoting the use of surface mount and advanced electronic packaging technology in the design and production of electronic hardware.

- Council Members represent user, supplier and equipment manufacturing companies engaged in surface mount implementation for automotive, telecommunication, computer, instrument, government, consumer, and medical electronics.

## **Council Mission Statement**

2013

The mission of the council is to facilitate, coordinate, and promote the orderly implementation of surface mount and advanced electronic packaging technology through standardization, the development of technical documents, and other means.

<u>1985 - 1999 Council Accomplishments</u>

#### Worst-case use environment Use category Tmin Tmax **ΔT°C** Cycles/ Typical Approx. to °C °C years of accept. year hrs service failure risk % 0 +6035 12 365 1-3 1) Consumer 1 +15 20 2 1 460 5 0.1 2) Computers +60-40 +85 35 12 7-20 0.01 3) Telecom 365 4) Commercial -55 12 +95 20 365 20 0,001 aircraft 20 12 185 5) Industrial & -55 +95 10 0.1 automotive **&40** 12 100 Passenger 860 12 60 **&80** 12 20 Compartment 6)Military -55 40 12 100 +95 10 0.1 Ground & ship **&**60 12 265 3 1 7) Space -55 +95 8 760 5-30 0.001 leo to 100 12 365 geo 8)Military avionics a +95 365 -55 40 2 10 0.01 60 2 365 b 80 2 365 С 820 1 365 9)Automotive -55 +125 60 1 000 5 0.1 1 under hood &100 300 1 &140 2 40

Reliability Matrix For SMT Solder Joints

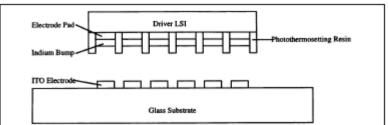

Figure 5–5 Newly Developed Chip on Glass Technology

Figure 5-6 Schematic Cross-Sectional View of Connection for Chip on Glass

#### **Fostered and Coordinated by the Council**

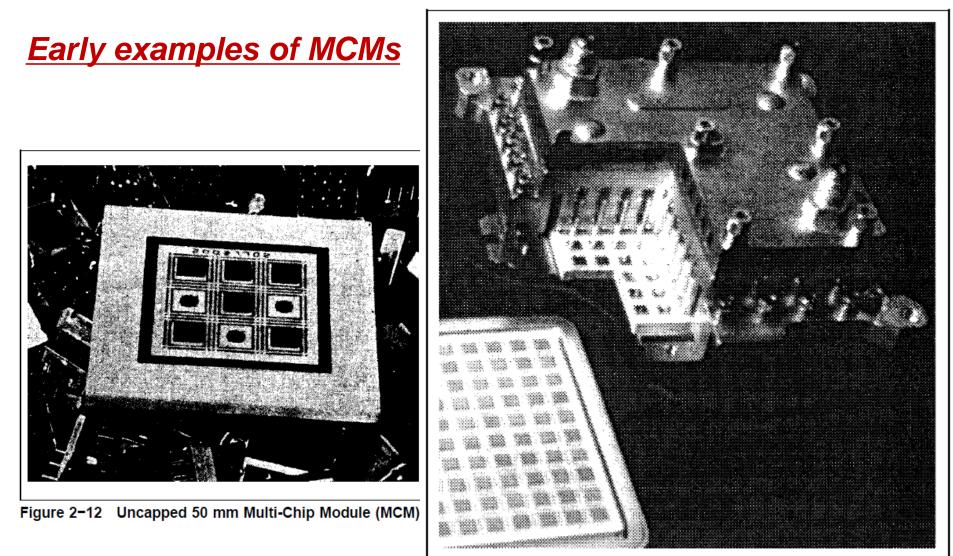

Figure 2–13 IBM Thermal Conduction Module with 100-130 Flip Chips and Hat with Piston Assemblies

## **Detail Attention to Cooling**

## Published 1992

Section 3 MCM-C Design Considerations (Ceramic/Glass Based Materials) 3.0 INTRODUCTION 3.1 Layout 3.2 Conductor Pattern 3.3 Conductor Routing

3.4 Land Patterns

3.5 Wire Bonds

3.6 Vias

3.7 Resistors

3.8 Substrate Requirements Section 4 MCM-L Design Considerations

(Organic Based Materials) 4.0 INTRODUCTION

4.1 Design Layout

4.2 Conductor Pattern

4.3 Land Pattern

4.4 Holes

4.5 Resistors

4.6 Substrate Materials

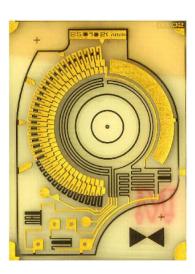

Section 5 MCM-D Design Considerations

(Deposited Dielectric Films)

5.0 INTRODUCTION

5.1 Layout

5.2 Conductor Pattern

5.2 Conductor Pattern

5.3 Conductor Routing

5.4 Land Patterns

5.5 Vias

5.6 Resistors

5.7 Integrated Circuit Die (Chips)

5.8 Dielectrics .

5.9 Substrates

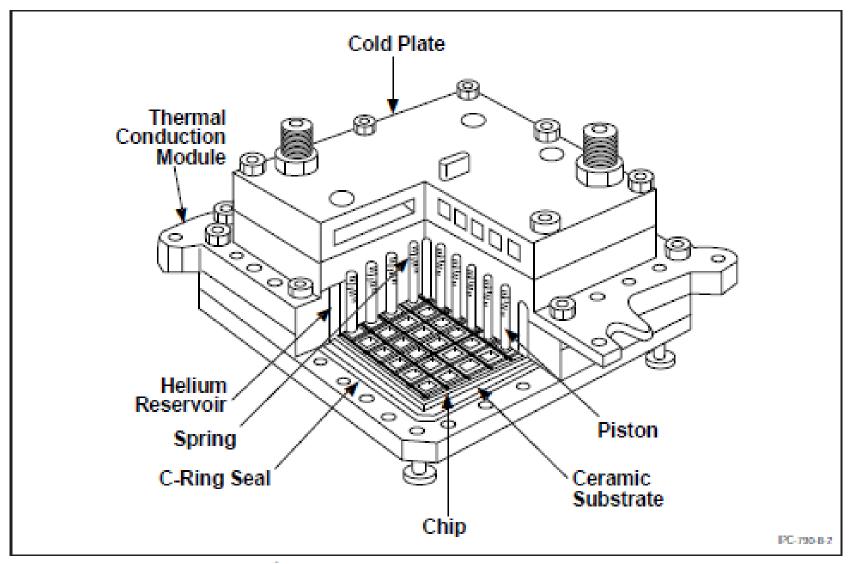

#### IPC-MC-790

Guidelines for Multichip Module Technology Utilization

#### "LOGICAL FUNCTIONAL BLOCKS GROUPED TO MAXIMIZE INTERCONNECT WITHIN A COMPACT ASSEMBLY, YET MINIMIZE INTERCONNECT TO THE NEXT LEVEL"

IPC-MC-790

July 1992

A standard developed by IPC

2215 Sanders Road, Northbrook, IL 60062-6135 Tel. 847.509.9700 Fax 847.509.9798 www.ipc.org

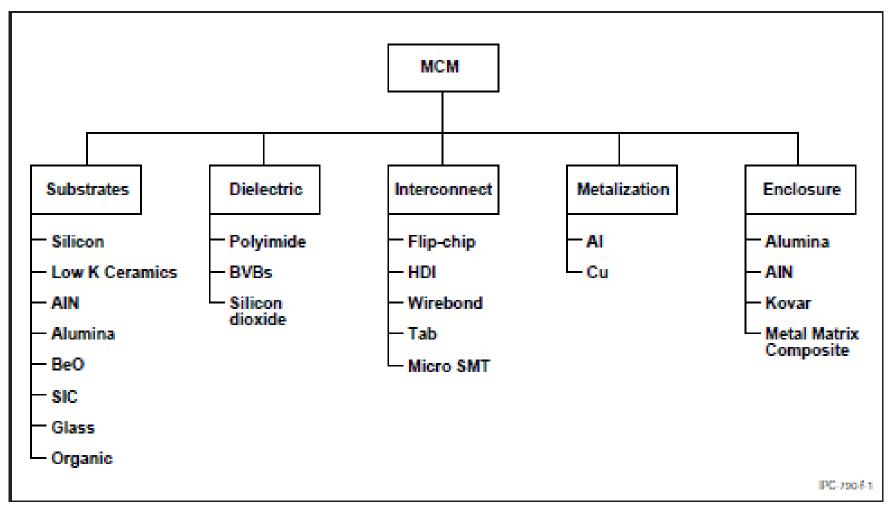

## **MCM Characteristics**

120

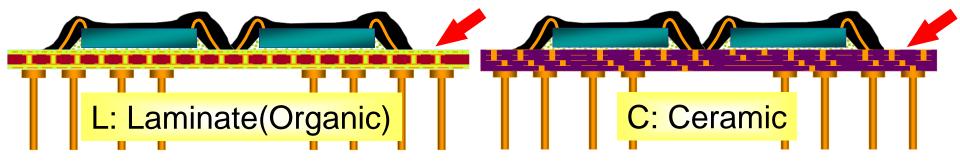

- Multichip modules identified by the letter C normally are constructed of ceramic or glass ceramic alternatives. These materials have a dielectric constant that is 5.

- Performance of the MCM-C considers the dielectric properties between single planes or between single planes and ground planes.

- The materials act as both the dielectric and the supporting plane for the components.

- Conductors are usually a fireable metal material such as tungsten, molybdenum, and the screenable frit metal thick film conductors of gold, silver, palladium and copper.

- When these materials are used to form the conductors, the conductor width is <0.15 mm Vias necessary during the interconnecting process are formed during the conductor screen printing,

- The vias are usually the same materials as the conductor.

- For most Multichip C applications, the number of active devices is greater than the passive components

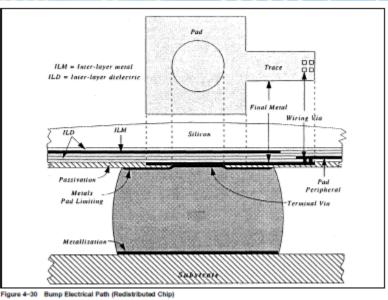

- Multichip Modules identified by the letter D are normally constructed using unreinforced dielectric materials that are adjacent to the signal plane.

- The dimensional stability of this type of module is determined by the underlying substrate which is usually made of ceramic, silicon, copper, glass-reinforced laminate, or other metal or metal composites.

- The dielectric materials normally have a dielectric constant of <5.

- The additive dielectrics may be deposited on the substrate or may be deposited on a metal platen and peeled off to be reapplied elsewhere in fresh situations.

- Conductors are sputtered or plated. The materials may be aluminum, copper, or gold. Photolithography is used to provide the imaging of the conductor patterns.

- Vias may be formed during the conductor deposition/ plating processes. When deposition and plating are used in combination, the vias are plated after conductor deposition

APEX EXPO 2013

**INFORMATION that INSPIRES INNOVATION**

## **Multichip Module L**

- Multichip Modules identified by the letter L use laminated printed board fabrication technology.

- Laminated layers may be reinforced or unreinforced and consist of such resin materials as epoxies, polyimides, or acrylics, reinforced with fiberglass, quartz, Kevlar, etc.

- The dielectric materials normally have a dielectric constant of <5.

- Conductors are almost always copper. These are deposited additively or are generated as part of the printed board subtractive process. Vias are copper, electrolessly plated initially, followed by additional electrodeposition.

- When the MCM-L requires control of the coefficient of thermal expansion, lamination techniques use materials that have low CTE such as copper-invar-copper.

- MCM-L were usually the lowest cost solution

- In 2000 the SMC had completed most of their work, and decided to adjourn the council.

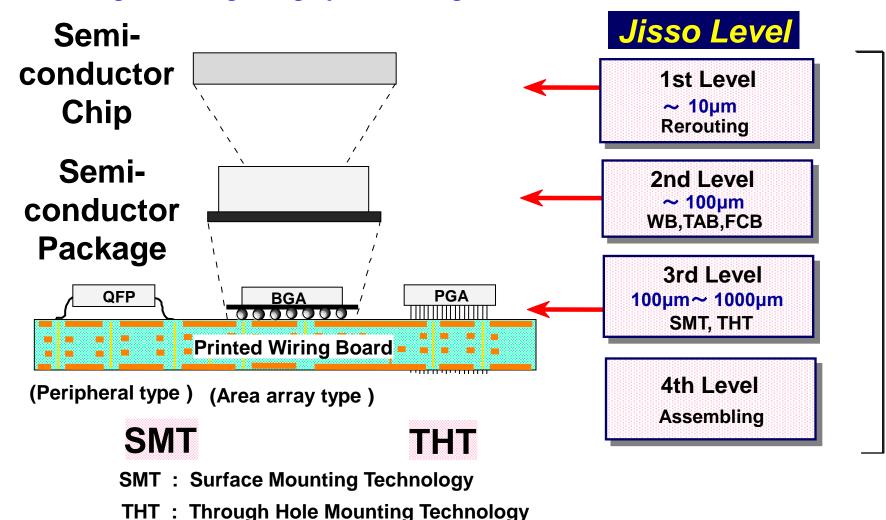

- Japan had just complete what they called a Jisso Technology Roadmap.

- At an IEC meeting in Japan, Kisao Kusuga, NEC, a key developer of the Jisso concept requested that US and Europe join Japan in the effort.

- IPC hosted the first meeting of the JIC in Chicago.

- The JIC has 3 subgroups JEA (Jisso East Asia), JNAC (Jisso North America), JEC, (Jisso European Council)

- The council meets yearly; JIC 14 scheduled for Seoul, Korea in April 2013

#### Mission Statement for the Jisso International Council (JIC) by IPC, JEDEC and EIAJ in May, 2000

The purpose of this council is to promote a strategic partnership among global organizations interested in the total solution for interconnecting, assembling, packaging, mounting, and integrating system design.

To accomplish these objectives, members will cooperatively work: to support and encourage standards development at a national or international level, to encourage the development of technology roadmaps, to address environmental issues, and to monitor market trends.

These activities will be based on the principles of free enterprise, cooperation, and will be undertaken in a spirit of responsibility to the worldwide electronics industry.

Jisso International Council, May 2000

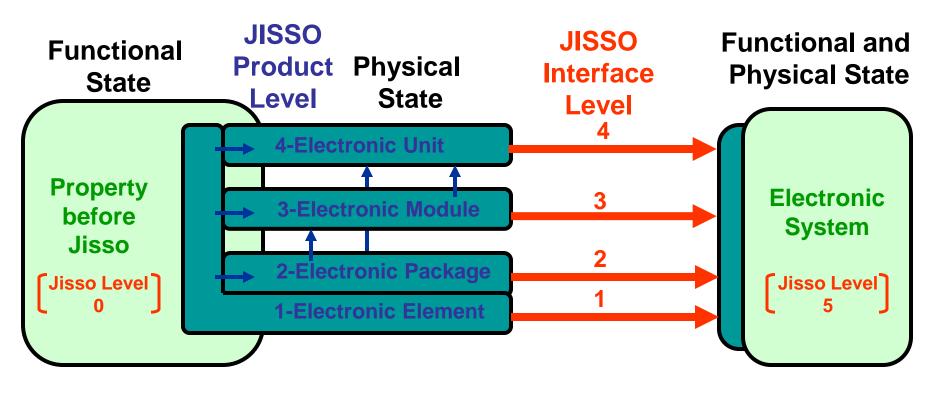

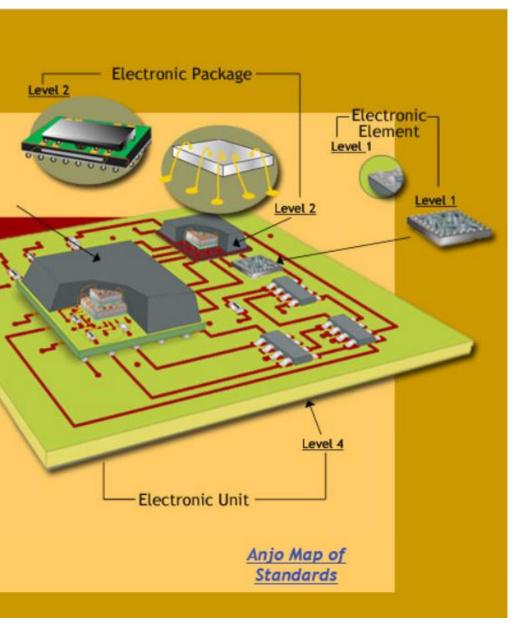

# The Concept of Jisso

A Total Packaging solution for Interconnecting, Assembling, Packaging, Mounting and Integrating system design.

#### Jisso Technology Revolution on High Density Mounting toward the 21st century

APEX

### JISSO Levels Concept

**Suppliers**

User

## **Definition of Basic Jisso Levels**

Level 0 - Property before Jisso

2013

- Includes standards, patents and proprietary methodology

- Jisso Product Level 1 Electronic Element

- Bare die/Wafer ready to be mounted, semi-finished component

#### Jisso Product Level 2 – Electronic Package

- Electronic, Optoelectronic, Mechanical MEMS, Includes finished components

- Jisso Product Level 3 Electronic Module

- Electronic, Optoelectronic, Mechanical MEMS

- Jisso Product Level 4 Electronic Unit

- Electronic, Optoelectronic, Mechanical MEMS

- Level 5 Electronic System

- Electronic, Optoelectronic, Mechanical, Backplane, Housing or Cabling

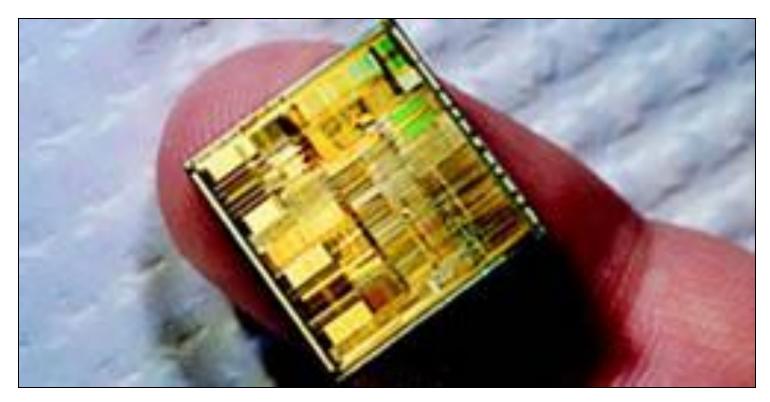

#### Individual Electronic Element Example

2013

Example courtesy of Intel

() AT Q Q Q V

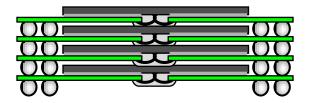

#### Individual Electronic Package Example

|  | - +<br>- L - +<br>- L - + S1 + - S2 + |  |

|--|---------------------------------------|--|

|  |                                       |  |

#### **Electronic Module Examples**

4 Layer Ball Stack Module

High Density Memory Module

Examples courtesy of Tessera

#### **Electronic Unit Example**

#### 20GB Ruggedized Solid State 2.5 inch Flash Drive Assembly

Example courtesy of Tessera

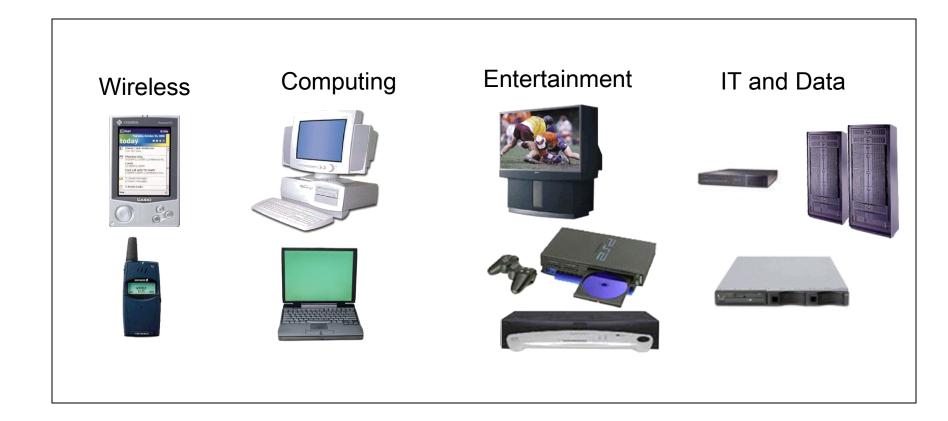

#### **Electronic System Examples**

## http://jisso.ipc.org/ on the IPC website

Jisso is a term that reflects the total packaging solution for electronic products. The characteristics of the Jisso concepts consider the bare die, its Packaging as an off-the-shelf product, or in a Module combined with other parts, mounting and interconnecting on a product substrate and integrated in the entire system design.

Level 3 -> Electronic

Module

**JISSO INTERNATIONAL COUNCIL**

There are several <u>levels</u> of Jisso, and several groups that bring together the global views of Jisso standards.

#### VISIT THEIR WEBSITES

| - <u>JNAC</u> | JEC  | JISSO JAPAN |

|---------------|------|-------------|

| <u>IPC</u>    | EIPC | JEITA       |

| JEDEC         | EECA | <u>JPCA</u> |

| <u>iNEMI</u>  |      | JARA        |

JISSO INTERNATIONAL COUNCIL

## **JISSO Council Proposal**

- 1. New Terminology Proposal

- 1) Needs of New Terminology

- 2) Definition

- 3) Objective(Needs for Standardization)

- 2. Classification

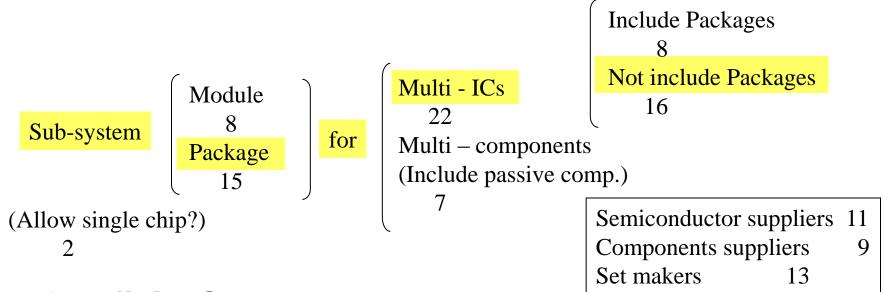

#### **Current Understanding of MCM**

2013

MCM Concept in Japanese Companies (JEITA Survey results, 2001)

#### Indefinite Concept

(a narrow sense - a wide sense)

- SiP,MCP also indefinite

- Other term(FCM,Hybrid IC, , ,) in a narrow sense

Need a new generic term

## New Terminology Proposal

*Terminology: Multi Device Sub-assembly(MDS)*

Definition:

The MDS is a sub-system which consists of multiple electronics devices including at least one integrated circuit. It is connected to a motherboard which functionally integrates it into a system. (A generic term which includes Hybrid IC/MCM/MCP/FCM/ FCP/SiP/SIMM/DIMM)

Objective:

Jisso Level 3 common standard between users and suppliers

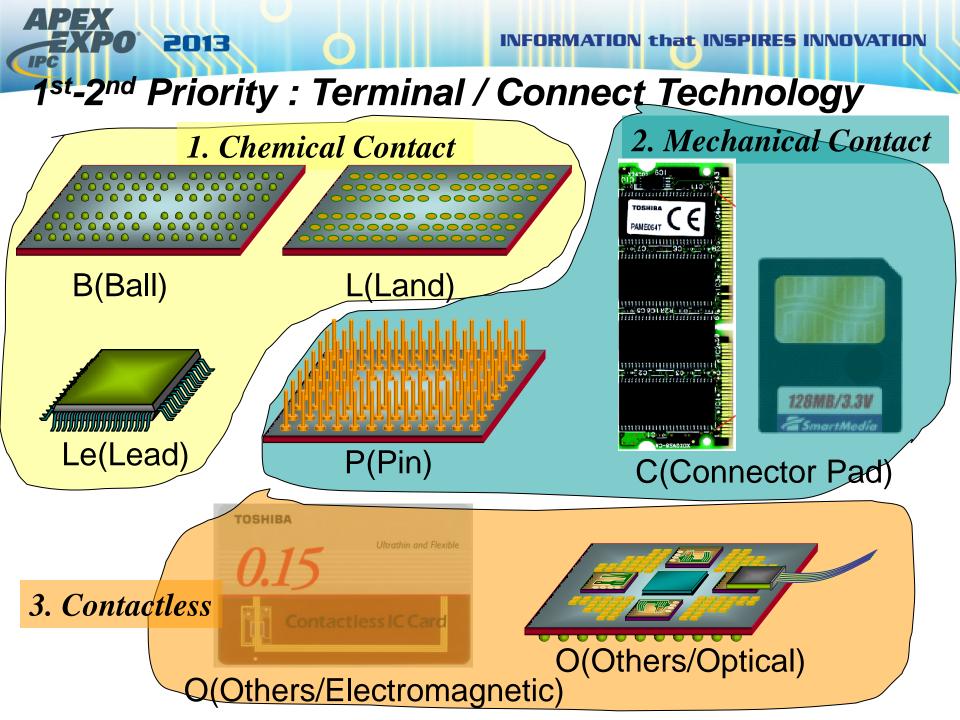

#### **Classification of MDS**

2013

| Prioritization  | Category                                                                                                                                  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------|

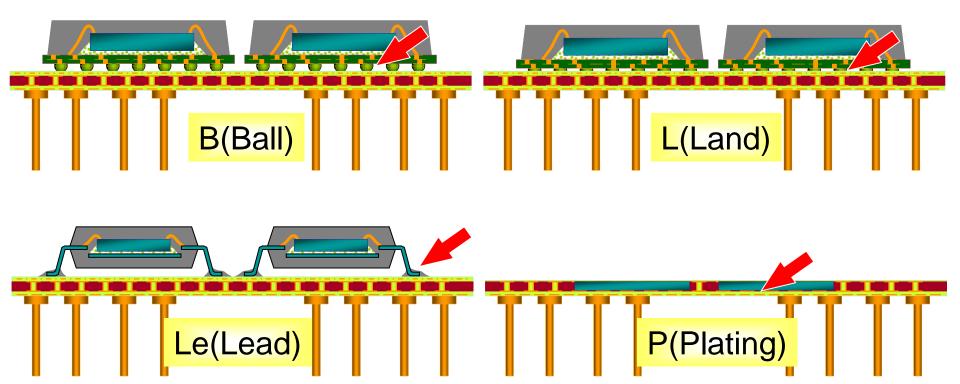

| 1 <sup>st</sup> | Terminal<br>B(Ball) / L(Land) / Le(Lead) / C(Connector Pad) / P(Pin) /<br>O(Others: Optic,Electromagnetic)                                |

| 2 <sup>nd</sup> | Terminal Connect Technology<br>1:Chemical(Solder/Conductive resin) 3:Contactless(Optic/Electromagnetic)<br>2:Mechanical(Connector/Socket) |

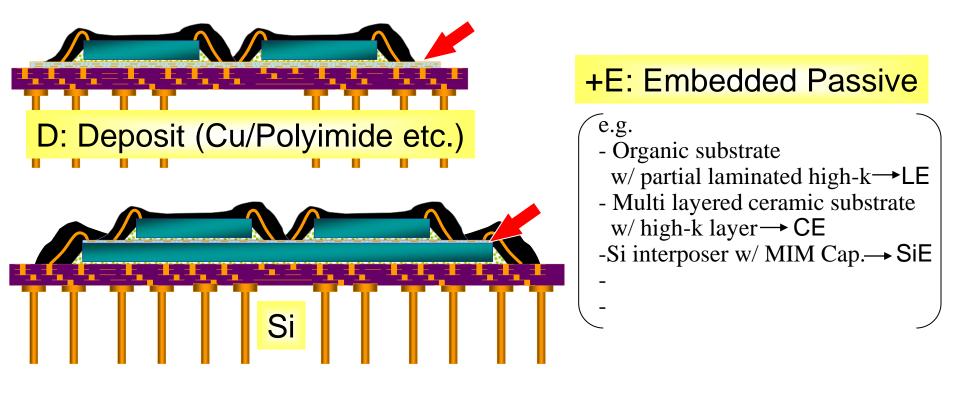

| 3 <sup>rd</sup> | Substrate Material<br>C(Ceramic) / L(Laminate) / D(Deposit) / Si / O(others)<br>+ E(Embedded Passive)                                     |

| 4 <sup>th</sup> | Devices<br>1(Same IC) / 2(Various IC) / 3(IC+Discrete and/or Passive)                                                                     |

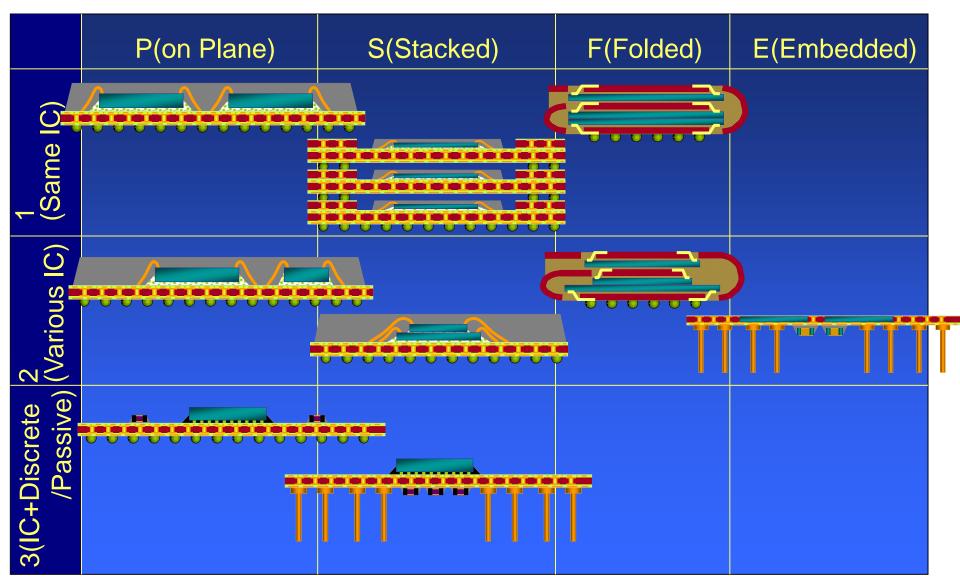

| 5 <sup>th</sup> | Devices Configuration<br>P(on Plane) / S(Stacked) / F(Folded) / E(Embedded in Substrate)                                                  |

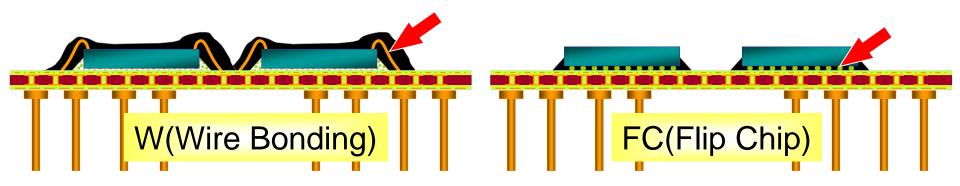

| 6 <sup>th</sup> | Interconnect Technology for IC Assembly<br>W(Wire) / FC(Flip-chip) / Le(Lead) / B(Ball) / L(Land) / P(Plating) / M(Mixed)                 |

### 4<sup>th</sup>-5<sup>th</sup> Priority : Devices / Configuration

6<sup>th</sup> Priority : Interconnect Technology

### **Typical Examples of MDS Classification**

Stacked MCP for Mobile Phones "MDS-B1-L-2S-W"

Transmeta Crusoe "MDS-B1-C-3P-FC"

DIMM/SIMM "MDS-C2-L-1P-Le"

Flash+SRAM in Tessera Folded Stacked "MDS-B1-L-2F-Le"

Can Define/Classify Current/Published Products, but Hard to Understand.

## **Involvement through ISO and IEC**

- The JIC promoted the concept of working with IEC and ISO standards in order to accomplish their mission.

- The mapping of standards to the "Total Packaging Solution" was an attempt to have all the building blocks in place in order to have technology become main stream

- Several JIC meetings were hosted by the IEC, however JIC is not an official group

- Countries submit resource documents and the are turned into International standards supported by COUNTRIES.

- In some instances these may become international Law due to cooperative effort.

- The IEC National committees just adopted the IPC-A-610

as the global Workmanship standard

# **Major Committees of Interest**

- TC47 Semiconductor Devices [JEDEC]

- TC91- Electronics assembly technology

Electronic Assembly Physical Characteristics

Design Automation for Electronic Assembly

- TC111 Environmental standardization for electrical and electronic products and systems

- TC119 Printed Electronics

#### **IEC/PAS 62588**

Edition 1.0 2008-09

1

0

U

Ш

1<

#### PUBLICLY AVAILABLE SPECIFICATION

Marking and labeling of components, PCBs and PCBAs to identify lead(Pb), Pb-free and other attributes

Copyright @ 2007, IPC/JEDEC; 2008, IEC

PAS 62588 @ IEC:2008(E)

INTERNATIONAL ELECTROTECHNICAL COMMISSION

#### Marking and Labeling of Components, PCBs and PCBAs to Identify Lead(Pb), Pb-Free and Other Attributes

#### FOREWORD

- 1) The International Electrotechnical Commission (IEC) is a worldwide organization for standardization comprising all national electrotechnical committees (IEC National Committees). The object of IEC is to promote international co-addition on all questions concerning standardization in the electrical and electronic fields. To this end and in addition to other activities, IEC publishes International Standards, Technical Specifications, Technical Reports, is entrusted to technical committees; any IEC National Committee interested in the subject dealt with may participate in this preparatory work. International, governmental and non-governmental organizations liaing with the International Organizations. IEC Collaborates closely with the International Organizations.

- 2) The formal decisions or agreements of IEC on technical matters express, as nearly as possible, an international consensus of opinion on the relevant subjects since each technical committee has representation from all interested IEC National Committees.

- 3) IEC Publications have the form of recommendations for international use and are accepted by IEC National Committees in that sense. While all reasonable efforts are made to ensure that the technical content of IEC Publications is accurate, IEC cannot be held responsible for the way in which they are used or for any misinterpretation by any end user.

- 4) In order to promote international uniformity, IEC National Committees undertake to apply IEC Publications transparently to the maximum extent possible in their national and regional publications. Any divergence between any IEC Publication and the corresponding national or regional publication shall be clearly indicated in the latter.

- IEC provides no marking procedure to indicate its approval and cannot be rendered responsible for any equipment declared to be in conformity with an IEC Publication.

- 6) All users should ensure that they have the latest edition of this publication.

- 7) No liability shall attach to IEC or its directors, employees, servants or agents including individual experts and members of its technical committees and IEC National Committees for any personal injury, property damage or other damage of any nature whatsoever, whether direct or indirect, or for costs (including legal fees) and expenses arising out of the publication, use of, or reliance upon, this IEC Publication or any other IEC Publications.

- 8) Attention is drawn to the Normative references cited in this publication. Use of the referenced publications is indispensable for the correct application of this publication.

- 9) Attention is drawn to the possibility that some of the elements of this IEC Publication may be the subject of patent rights. IEC shall not be held responsible for identifying any or all such patent rights.

A PAS is a technical specification not fulfilling the requirements for a standard but made available to the public.

IEC-PAS 62588 was submitted by IPC/JEDEC and has been processed by IEC technical committee 91: Electronics assembly technology.

| The text of this PAS is based on the following document: | This PAS was approved for<br>publication by the P-members of the<br>committee concerned as indicated in<br>the following document |

|----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| Draft PAS                                                | Report on voting                                                                                                                  |

| 91/767/PAS                                               | 91/783/RVD                                                                                                                        |

Following publication of this PAS, the technical committee or subcommittee concerned will investigate the possibility of transforming the PAS into an International Standard.

An IEC-PAS licence of copyright and assignment of copyright has been signed by the IEC and IPC/JEDEC and is recorded at the Central Office.

This PAS shall remain valid for an initial maximum period of 3 years starting from the publication date. The validity may be extended for a single 3-year period, following which it shall be revised to become another type of normative document, or shall be withdrawn.

#### test methods suitability

-

|                       | Types and terminals of device              |                    |                           |                                                                       | Rapid temperature change test |                           |                         |                           |                               |                           |                     | Mechanical               |

|-----------------------|--------------------------------------------|--------------------|---------------------------|-----------------------------------------------------------------------|-------------------------------|---------------------------|-------------------------|---------------------------|-------------------------------|---------------------------|---------------------|--------------------------|

|                       | Termina                                    | als                | Number<br>of<br>terminals | Examples                                                              | Pull test                     | Shear<br>strength<br>test | Torque<br>shear<br>test | Resistance<br>measurement | Monotonic<br>bending<br>limit | Cyclic<br>bending<br>test | Cyclic<br>drop test | shear<br>fatigue<br>test |

|                       | Bectrodes on 2<br>sides<br>(bent leads)    | ۲                  | 2                         | Tantalum<br>capacitor,<br>inductor                                    | -                             | A,B                       | ×                       | -                         | (40)                          |                           | с                   | -1                       |

|                       | Bectrodes on 3<br>sides                    |                    | 2                         | Rectangular chip<br>resistor/film<br>capacitor                        | 12                            | A,B                       | 2                       | 20                        | 124                           | 24                        | с                   | 2                        |

|                       | Bectrodes on 5<br>sides<br>(including cap) | \$40               | 2                         | Laminated<br>capacitor,<br>thermistor,<br>laminated<br>inductor, fuse | -                             | A,B                       | 2                       | -                         | -                             | -                         | с                   | -                        |

|                       | Multi terminals<br>(terminals on<br>sides) | 1000 C             | 4 or more                 | Resistor array,<br>capacitor array                                    | -                             | A,B                       | -                       | -                         | -                             | с                         | с                   | -                        |

|                       | Gull wing – 1                              | ۲                  | 4 or more                 | Transformer                                                           | A,B                           | с                         |                         | -                         | с                             | -                         | с                   |                          |

|                       | Gull wing – 2                              | -                  | Up to 6                   | Switch                                                                | -                             | Ð                         | A,B                     | -                         | 140                           | -                         | с                   | -                        |

|                       | Gull wing – 3                              | 4                  | 4 or more                 | Connector                                                             | 2                             | A,B                       | A,B                     | 2                         | с                             | 22                        | С                   | 22                       |

|                       | Bectrodes on<br>bottom                     |                    | 2                         | Inductor, tantalum<br>capacitor                                       |                               | A,B                       | Ð                       | -                         | 1.71                          | 1.71                      | С                   | -                        |

|                       | Round electrode<br>(including cap)         | Ø                  | 2                         | MELF<br>capacitor/resistor<br>/fuse                                   | -                             | A,B                       | B                       | -                         | 121                           | 040                       | с                   | 2                        |

| Semiconductor devices | Leads on two<br>sides<br>(bent lead)       |                    | 2                         | Diode                                                                 | ÷                             | A,B                       | C                       | -                         | (*)                           | 642                       | с                   | -1                       |

|                       | Gull wing leads                            |                    | 3 to 6                    | Small transistor                                                      | с                             | в                         | С                       | -                         | 120                           | 220                       | С                   | -                        |

|                       | Gull wing leads<br>J-lead packages         |                    | 6 or more                 | QFP, SOP<br>J-lead                                                    | A,B                           | 2                         | 21                      | с                         | С                             | С                         | в                   | Ð                        |

|                       | Non-lead                                   |                    | 6 or more                 | QFN, SON                                                              | σ                             | 70                        | 70                      | A,B                       | с                             | в                         | в                   | B                        |

|                       | Ball electrodes on<br>bottom               | <del>600 000</del> | Multiple                  | BGA, FBGA                                                             | -                             | -                         | -                       | A,B                       | с                             | в                         | B                   | Ð                        |

|                       | Bectrodes on<br>bottom without ball        | <del></del>        | Multiple                  | LGA, FLGA                                                             | -                             | -                         | -                       | A,B                       | с                             | в                         | в                   | в                        |

FR4 IPC- 4101 slash sheet to SolderTemps

| FR4 Material Properties |            |              |              |              |                     |  |  |  |

|-------------------------|------------|--------------|--------------|--------------|---------------------|--|--|--|

| Laminate                | Exposure   | Exposure     | Exposure     | Exposure     | Comments            |  |  |  |

| Properties              | Level      | Level        | Level        | Level        |                     |  |  |  |

|                         | Α          | В            | C            | D            |                     |  |  |  |

| Standard                | 4101/126   | 4101/99      | 4101/101     | 4101/124     | Brominated          |  |  |  |

| Nomenclature            | 4101/130   | 4101/128     | 4101/127     | 41010/125    | Un- <u>Bromin</u> . |  |  |  |

| Tg                      | 170        | 150          | 110          | 150          |                     |  |  |  |

| <b>-</b> .              |            |              |              |              |                     |  |  |  |

| Td                      | 340        | 325          | 310          | NA           |                     |  |  |  |

| Solder float            |            |              |              |              |                     |  |  |  |

| extremes                |            |              |              |              |                     |  |  |  |

| 260°C                   | 30         | 30           | 30           | NA           |                     |  |  |  |

| 288°C                   | 15         | 5            | 5            |              |                     |  |  |  |

| 300°C                   | 2          | NA           | NA           |              |                     |  |  |  |

| CTE in                  | 14 - 18    | 14 - 18      | 14 - 18      | 14 - 18      |                     |  |  |  |

| X&Y                     | PPM/ºC     | PPM/ºC       | PPM/ºC       | PPM/ºC       |                     |  |  |  |

| CTE in Z                |            |              |              |              |                     |  |  |  |

| A alpha1                | 60 max     | 60 max       | 60 max       | NA           |                     |  |  |  |

| B alpha2                | 300 max    | 300 max      | 300 max      |              |                     |  |  |  |

| C 50-260°C              | 3.0% max   | 3.5% max     | 4.0% max     |              |                     |  |  |  |

| Copper                  | 0.7        | 0.7          | 0.7          | 0.7          |                     |  |  |  |

| Adhesion                | Newton/MM  | Newton/MM    | Newton/MM    | Newton/MM    |                     |  |  |  |

| Copper                  | 17µm       | 17µm         | 17µm         | 17µm         |                     |  |  |  |

| Ductility               | 5% min     | 5% min       | 5% min       | 5% min       |                     |  |  |  |

| Moisture                | 0.5% max   | 0.5% max     | 0.5% max     | 0.8% max     |                     |  |  |  |

| Content                 |            |              |              |              |                     |  |  |  |

| End Usage               |            |              |              |              |                     |  |  |  |

| Benign end              | OK for use | OK for use   | OK for use   | OK for use   |                     |  |  |  |

| use                     |            |              |              | + durability |                     |  |  |  |

| Median end              | OK for use | OK for use   | OK for use   | OK for use   |                     |  |  |  |

| use                     |            | Plus test    | + durability | + durability |                     |  |  |  |

| Severe end              | OK for use | OK for use   | OK for use   | NA           |                     |  |  |  |

| use                     | + quality  | + durability | + durability |              |                     |  |  |  |

## What Have We Learned ?

- Cooperative effort can make a difference

- Communication is key

- Good marketing helps sell ideas

- Publish or perish

- Users feel comfortable with choices to meet their needs and application

- There needs to be a focus group supported by organizations ready to set direction and to create a mission and Status and Action Plan.

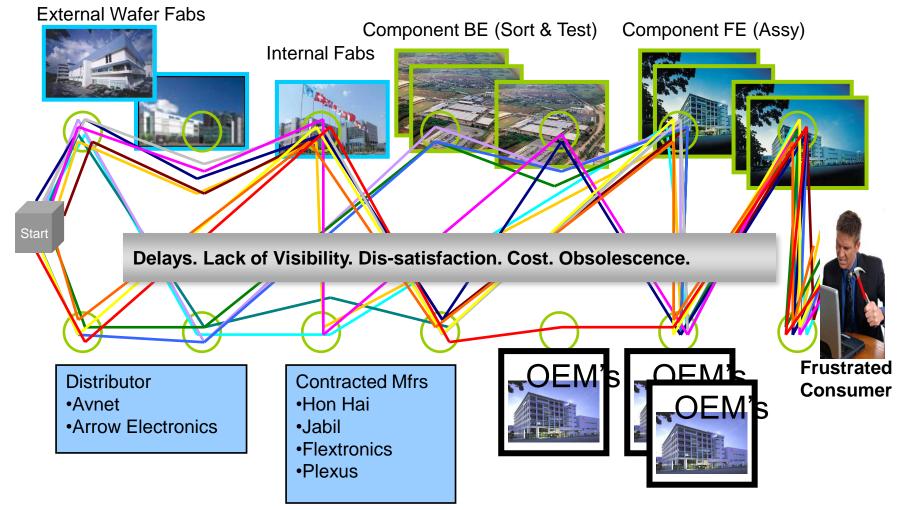

## Present Day Technology and Implementation

• Lots of activity in the last few years

- Much of it was driven by the visionary leaders

- Of all the end-use environments, the main drivers have been the Commercial products

- The supply chain becomes more convoluted and more difficult to manage

- The printed board mounting platform has become very complex and OEMs want assurance of reliability

- Trade associations work to help develop new test methods and techniques for product life

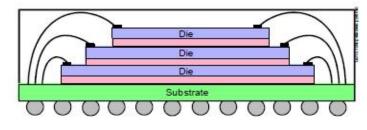

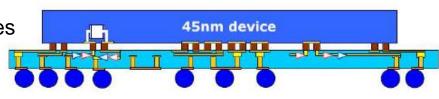

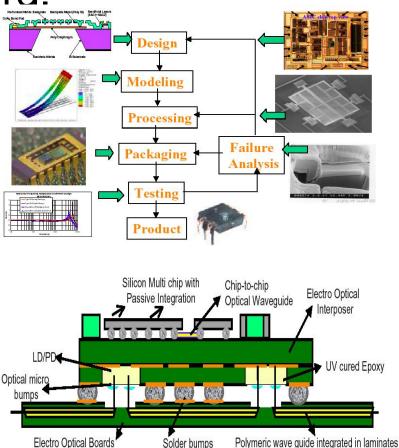

## APEX 2013 INFORMATION that INSPIRES INNOVATION 3D Package Technology

- Stacked Die in Package

- Standard wire bond assembly process

- Billions of packages shipped annually (memory)

- Represents > 15% of semiconductor die area

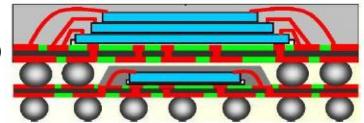

- Package-on-Package

- Hundreds of millions ship annually (logic and memory)

- Advantage in logic/memory test separation

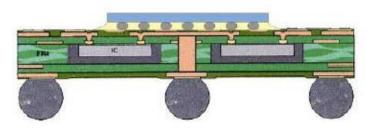

- Embedded Die in PCB

- Limited production since 2005

- Recent renewed interest (PCB and wafer-based)

- Die/Wafer Interconnection Using TSV

- Ultimate SiP in size and performance

- TSV production to date only with non-3D structures

- Face-to-face production without TSV in 2007

Source: Imbera

Source: ST Complements of Prismark

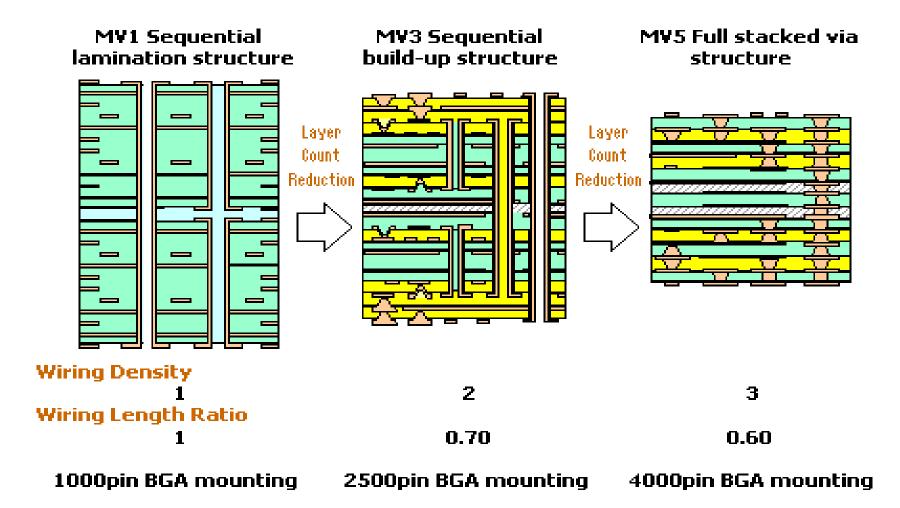

## **Substrate Technology Evolution**

## **Establishing Focus**

- Reliability is the ability to function as expected under the expected operating conditions for an expected time period without exceeding expected failure levels

- Proof of Performance

- End item reliability can only be determined by the OEM.

- PWB Fabricators often have little or no visibility to end item requirements.

- Quality is the ability to produce the product in the manner specified by the customer in the documentation package provided including any test or legal requirements

- Meets Requirements

- OEM's define PWB quality requirements necessary to meet their reliability needs.

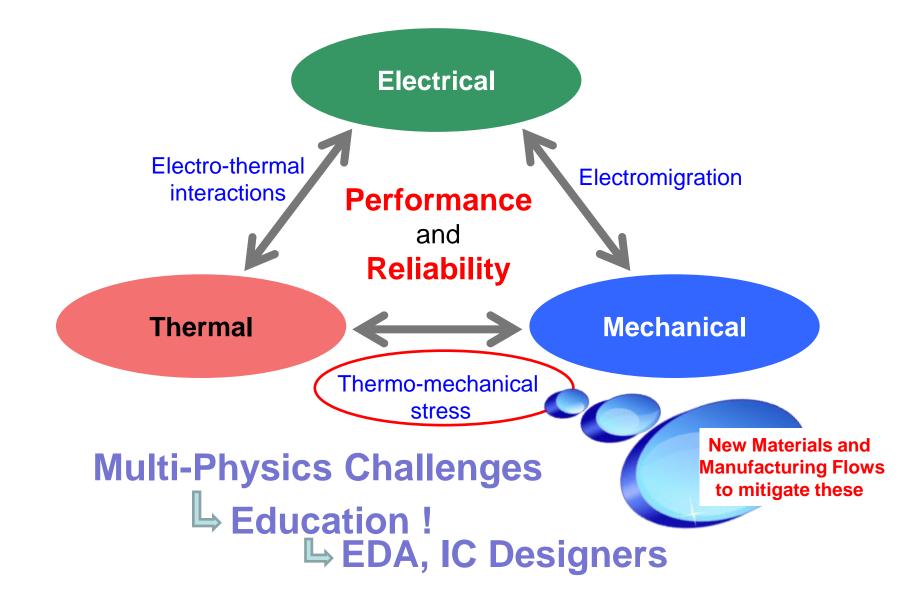

# 2013 SUES to CONSIDER INSPIRES INNOVATION

### • Die

Electrical load: voltage, current, power, surge,

Environmental load, die itself and interaction within package

## Package

Environmental and mechanical load Internal die interconnection Package type: Leaded/leadless, BGA, CSP, WLP, Flip chip

### • PWB

Materials (FR-4, Polyimide), Lay up (copper, HDI), Finish PTH, Microvia, Via in pad, Embedded Components

## Assembly

Electrical, environmental (thermal, mechanical, chemical, etc)

### System

**Product specific**

All of these are OEM design considerations.

# **Collision of Quality and Reliability Requirements**

• OEM products must survive 2 primary environments:

- 1. Product Assembly (Reflow/wave & rework)

- 2. Field Service (thermal cycles & shock/vibration)

- Traditional PWB Quality Requirements are primarily measurements used for PWB fabrication process validation but have limited use for determining reliability.

# **Modern Reliability Challenges**

- Components are much smaller than they were a few years ago.

- Components are placed more densely on PWBs.

- PWBs go through more severe reflow processes, and often multiple times.

- Lead-Free solder increases processing temperatures

- As a result PWB designs have changed

- PWB features are very small

- High aspect ratio vias

- (old designs seldom higher than 5:1, today can be 10:1)

- *Many* more vias per pwb than in the past

- Laminate materials must be more robust

- Assembly temperatures are higher

- Must have low z-axis expansion for greater via life.

## **New Evaluation Methods**

- Reliability

- A- Thermal shock

- B- Vibration

2013

- C- Thermal Cycle

- D- HAST

- E- IST

- F- Pressure Vessel

- G CAF

- H Whisker Growth

- J Assembly Simulation

- X System Specific

## <u>Quality</u>

- Visual Inspection

- Visual 10X 40X

- Dimensional

- Microsection

- Continuity/ In-Circuit

- Customer Specific

- PCQRR

- <u>Durability -New</u>

- HATS

- IST

- Solder Float

- Solder Reflow

Microvias 190°C

Polyimide 210°C

#### Mounting Substrate

The product is as strong as the weakest link – Have lower requirements for sub assemblies makes no sense.

#### Product Application per end use

|                        | 1                 |                   | 1                 |                   |                   |

|------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|

| End-use Environment    | A-Interposer      | B-Module          | C-Portable        | D-Product         | E-Back Plane      |

| 1-Consumer             | 100 cycles @ 150  |

| 2-Computers and        | 100 cycles @ 150  |

| Peripherals            |                   |                   |                   |                   |                   |

| 3-Telecomm             | 250 cycles @ 150  |

| 4-Commercial Aircraft  | 350 cycles @ 150  |

| 5-Industrial and       | 500 cycles @ 150  |

| Automotive Passenger   |                   |                   |                   |                   |                   |

| Compartment            |                   |                   |                   |                   |                   |

| 6-Military             | 500 cycles @ 150  |

| (ground and shipboard) |                   |                   |                   |                   |                   |

| 7-Space                | 1400 cycles @ 150 |

| 8-Military Aircraft    | 500 cycles @ 150  |

| 9-Automotive           | 500 cycles @ 150  |

| (under hood)           |                   |                   |                   |                   |                   |

| 10- Bio Medical & Life | 500 cycles @ 150  |

| support                |                   |                   |                   |                   |                   |

RoHS = 260°C

Tin/Lead =  $230^{\circ}$  C

2013

#### **Assembly Process Simulation**

| Product Application per end use          |              |                 |            |           |              |  |  |

|------------------------------------------|--------------|-----------------|------------|-----------|--------------|--|--|

| End-use Environment                      | A-Interposer | <b>B-Module</b> | C-Portable | D-Product | E-Back Plane |  |  |

| 1-Consumer                               | 6X260°C      | 6X260°C         | 6X260°C    | 6X260°C   | 6X260°C      |  |  |

| 2-Computers and<br>Peripherals           | 6X260°C      | 6X260°C         | 6X260°C    | 6X260°C   | 6X260°C      |  |  |

| 3-Telecomm                               | 6X260°C      | 6X260°C         | 6X260°C    | 6X260°C   | 6X260°C      |  |  |

| 4-Commercial Aircraft                    | 6X260°C      | 6X260°C         | 6X260°C    | 6X260°C   | 6X260°C      |  |  |

| 5-Industrial and<br>Automotive Passenger | 6X260°C      | 6X260°C         | 6X260°C    | 6X260°C   | 6X260°C      |  |  |

| Compartment<br>6-Military                | 6X230°C      | 6X230°C         | 6X230°C    | 6X230°C   | 6X230°C      |  |  |

| (ground and shipboard)                   |              |                 |            |           |              |  |  |

| 7-Space                                  | 6X230°C      | 6X230°C         | 6X230°C    | 6X230°C   | 6X230°C      |  |  |

| 8-Military Aircraft                      | 6X230°C      | 6X230°C         | 6X230°C    | 6X230°C   | 6X230°C      |  |  |

| 9-Automotive                             | 6X260°C      | 6X260°C         | 6X260°C    | 6X260°C   | 6X260°C      |  |  |

| (under hood)                             |              |                 |            |           |              |  |  |

| 10- Bio Medical & Life support           | 6X230°C      | 6X230°C         | 6X230°C    | 6X230°C   | 6X230°C      |  |  |

# **Issues Facing Designers**

## High Density High Speed High Functional

QFP, SOP

2013

**Module, 3D,** Merging with Package and Device

BGA, CSP LGA

**Environmental Protection**

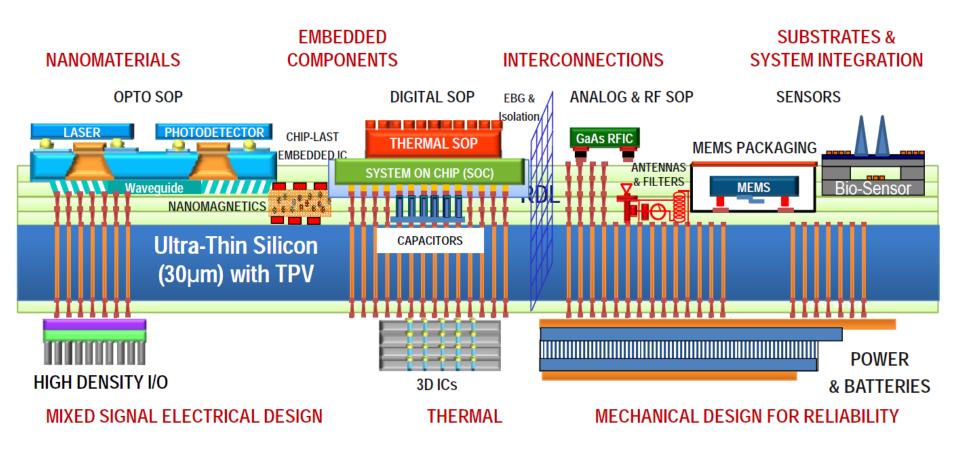

# **Complex Technologies**

- Different materials & technologies mounted on the same board.

- Embedded Active Devices

- Embedded Passive Devices

- > MEMS

- > Optoelectronics

- > SiP

- Sensors, Others

## **Tech Supply Ghain Movation** A Complex Ecosystem

## **Ongoing Efforts to Accelerate 3D Rollout**

- 3D development efforts at industry consortia

- SEMI & Si2 drive manuf./design standards

- GSA's 3D IC Working Group ongoing since 2009

- JEDEC: Wide I/O Standard, rev 1 released in Jan

- HMCC released first interface spec issued in Aug

- Many technical books

2013

Little or no coordination

APEX EXPO 2013

**INFORMATION that INSPIRES INNOVATION**

## **Tomorrow's 5.5D System Integration**

Source: Rao Tummala, Georgia Institute of Technology, 3D Systems Packaging Research Center,

# **Conclusions**

- Get involved and let your needs be heard

- Study implementation standards

- Identify reliability issues with case studies

- Participate in email forums with colleagues

- Understand the needs of the customer whose requirements are in the contract.

- Comprehend the meaning of manufacturing instructions (notes) on documentation

- Know the methods and techniques of Data Transfer from Design to Manufacturer