## In-Circuit Test Probe Contact on Lead Free Printed Circuit Board Assemblies

Cyril Cooper Celestica Limited United Kingdom

#### Abstract

The in-circuit test (ICT) of printed circuit boards (PCBs) assembled with Lead Free solder was anticipated to be problematic by industry test engineers, due to contact failures associated with the perceived lack of pin probability of Lead Free solder pastes and fluxes. The introduction of Lead Free processing could potentially present new challenges to the established ICT process.

A good electrical contact between test probes and test targets on the unit under test (UUT) is fundamental to the success of ICT. The testing of tin-lead soldered PCBs is a mature process, supported by years of effort, many studies and numerous improvement projects, carried out on pin probable solder paste, flux development, design for test (DFT), test probe and fixture design.

A study of Lead Free processing and the impacts to test and inspection equipment was undertaken. All available information from customer product introductions, test equipment vendors and industry resources was collated and the risks involved in moving from tin-lead solder to Lead Free solder were identified.

This paper describes the method and experimentation used to investigate ICT probe contact on Lead Free boards. A test vehicle was designed with different sized test pads and vias and an ICT fixture was manufactured. Process and test influencing factors were identified, including various Lead Free solder pastes and board finishes. Using Six-Sigma methodology, a number of experiments were designed, results analyzed and the significance of the experiment parameters (factors) investigated. Recipes were developed for achieving good ICT probe contact on Lead Free boards.

#### Introduction

The European Union's Restriction of Hazardous Substances (RoHS) legislation requires that all products shipped into Europe, contain less than the specified limits of six banned substances, including lead, by July 2006. Some companies, however, such as network infrastructure and high-end computing manufacturers, will be able to exercise Lead Free exemptions until 2010.

At the start of this study there were a number of Lead Free boards in production, however, the only information that could be collected for ICT was from low-volume qualification builds. In the absence of a volume Lead Free customer board, a probe test vehicle was designed to investigate possible contact problems at ICT. Prior to this project, the effects of Lead Free solder on ICT pin probability had not yet been analyzed and understood. If encountered, significant ICT probability problems would have a devastating effect on delivering Lead Free PCBs to original equipment manufacturers (OEMs).

#### Lead Free Qualification Matrix

Numerous Lead Free test and inspection equipment trials and evaluations have been carried out by equipment vendors and institutions, but the magnitude of the assembly process change from tin-lead to Lead Free required that all eventualities or issues that may arise during and after the transition to Lead Free were identified and resolved.

To ensure that all eventualities were covered, a detailed matrix was generated and applied to the two technologies. The first steps were to gather, collate and review the documentation produced and analyze the results to see if any conclusions could be reached. The matrix that was developed contained all aspects of test and inspection, including automatic paste inspection, automatic optical inspection, manual X-Ray inspection, automatic X-Ray inspection, flying probe, in-circuit test and functional test.

The main objective of the Lead Free qualification matrix was to identify the activities required to qualify test and inspection equipment as being capable of testing Lead Free PCBs. The aim was to highlight a series of projects and initiatives that must be undertaken to understand the capabilities and limitations of the current test and inspection equipment when applied to PCBs assembled using Lead Free solder. In turn, these projects could highlight capability gaps that must be closed to ensure complete success during the transition process. Much of the matrix was completed with relative confidence by reviewing the numerous studies and evaluations that had taken place in the industry over the past few years.

Inspection equipment was reasonably well documented in the industry as being Lead Free capable, although supporting data from actual Lead Free production was scarce. Information was gathered internally from a high-volume Lead Free product at a Celestica facility that further proved that the equipment was capable of Lead Free inspection<sup>1</sup>.

Test equipment was not yet documented in the industry as being Lead Free capable and investigation was required. Research showed that flying probe, ICT and functional test could be potentially impacted due to contact problems associated with flux residue and board finish. It was also noted that Lead Free solder joints were more susceptible to failure during board bend than tin-lead solder joints<sup>2</sup>. Some of the areas of concern which required further investigation are shown below.

Lead Free ICT considerations:

- Type and quantity of flux residue (from reflow, wave, noclean)

- Solder does not flow as well as tin-lead

- Solder joint susceptibility to board strain

- Board finish (including organic solderability preservative (OSP))

- Test targets (test pads, test vias, plated through hole leads, press fit leads)

- Probe selection (manufacturer, head style, force, material)

- Number of fixture actuations for effective test

- Probe wear (frequency of repins)

- Fixture maintenance (frequency of preventative maintenance, probe cleaning)

- First pass yield

- Pareto of defects

- False failures and escapes

- Program debug (analog thresholds, tweaking)

#### **Probe Vehicle Project**

After reviewing the Lead Free qualification matrix, it was concluded that a project should be initiated to investigate ICT probing of Lead Free PCBs in a structured manner. A "probe vehicle" project team was formed; including members with a significant amount of Six-Sigma, process engineering and test engineering skills.

Using Six-Sigma methodology, a measurement system and a number of experiments were designed, results were analyzed and the significance of the experiment parameters (factors) investigated. A significant amount of Six-Sigma analysis took place during this project. This paper will not reproduce the project's documentation as it consisted of a main report<sup>3</sup> and 15 sub-documents.

#### Scope

During the start-up phase of the project it was quickly concluded that a large number of influencing factors and levels existed, and therefore some simplification was required. As part of this simplification initiative, the following decisions were made surrounding the scope of the project.

Factors included were:

- SMT reflow process

- Noclean process

- Test pads and test vias

- Board finish limited to OSP

- Celestica approved noclean solder pastes and fluxes

- Vacuum ICT fixture

- ICT probe selection

- Stencil design

- Number of reflow cycles

- Time from reflow to test

Factors excluded were:

- WAVE process

- WASH process

- Plated through hole (PTH)

- ICT probe wear

The main criterion for achieving good electrical contact is a low resistance electrical connection between the ICT and the unit under test. The aims of the Six-Sigma study were to measure contact resistance and analyze the results statistically. Digital photographs would be taken as supporting documentation for:

- Flux residue on ICT probes, test pads and test vias

- Condition of ICT probes, test pads and test vias

- Probe penetration into test pads and test vias

#### **Objectives**

There were two main objectives identified:

- Determine whether, and to what extent, ICT contact resistance is impacted by the introduction of Lead Free solder into the surface mount process on boards with an OSP surface finish.

- Identify the optimal recipes (supported by statistically valid data) for process/product parameters across one tin-lead solder paste and three Lead Free solder pastes to minimize overall ICT contact resistance and contact failures on boards with an OSP surface finish.

#### **Measurement System Design**

This section describes the design of the measurement system.

#### **Discussion of Methodology**

By using an existing ICT program and fixture and modifying a four terminal resistance measurement to measure a short circuit, confidence was gained that ICT was capable of measuring accurately within the 0.1 Ohm range. This assumption was further proven in separate experiments (see "Gauge repeatability and reproducibility experiments" in Section 4.0).

The measurement system consisted of three distinct parts: the board, the ICT fixture and its probes and an ICT. Several issues had to be overcome and thoroughly reviewed to ensure all requirements could be met. To overcome these issues:

- The fixture and the probe vehicle board were designed to measure the low value total resistance of the probe receptacle, test probe and the board contact point, using four terminal measurements.

- The board was designed to maximize the various probe and target levels. In addition it had to capture the most common test pad and test via sizes.

All of these requirements were achieved and the end design was a very flexible and usable board.

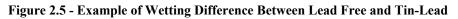

#### **Probe Vehicle Board Design**

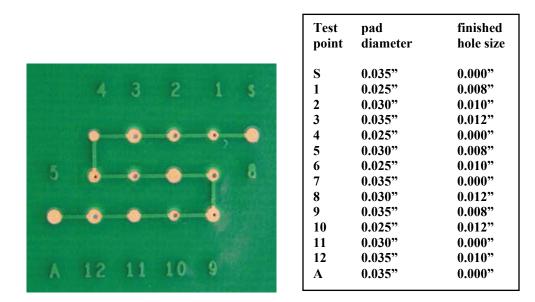

The probe vehicle board design consisted of 48 repeated test blocks, in which each test block contained 12 different pad / via hole size combinations with two additional test pads for four terminal measurements:

| Board                                         | single sided, 4 layer, 0.093" thickness |  |  |

|-----------------------------------------------|-----------------------------------------|--|--|

| Board size                                    | 6" x 9"                                 |  |  |

| Targets                                       | test via, test pad                      |  |  |

| Pad sizes                                     | 0.025", 0.030", 0.035"                  |  |  |

| Via hole sizes                                | 0.008", 0.010", 0.012"                  |  |  |

| Number of ICT four terminal measurements: 576 |                                         |  |  |

| Number of test points: 672                    |                                         |  |  |

| Board finish independent of the board design  |                                         |  |  |

A picture of the probe vehicle board and its test blocks can be found in Appendix 1 (Figures 1.1 and 1.2).

#### **ICT Fixture Design**

- In order to make accurate resistance measurements four terminal measurements were used.

- The ICT fixture contained receptacles for 0.039", 0.050", 0.075" and 0.100" probe sizes.

- The fixture could be populated with a range of different probe head styles and probe spring forces, depending on the requirements for particular experiments.

- A guided probe technique was used for 0.025" and 0.030" test targets and 0.039" probes.

The same ICT machine was used throughout all of the experiments. All multimeters and other digital meters used in the experiments were within their calibration period.

#### **Gauge Repeatability and Reproducibility Experiments**

Two separate gauge repeatability and reproducibility (GR&R) experiments were preformed on the measurement system to ensure it was capable of measuring within the range required (0.050 Ohm), and to ensure the variation in the gauge was acceptable (less than 0.005 Ohm).

### ICT GR&R

This study was performed to determine if the ICT was capable of making accurate and repeatable measurements for low value resistances of 0.100 Ohm and less. Seven precision resistors of various values were fitted inside the fixture to avoid all test probe to board contact issues. The GR&R consisted of five runs conducted by different operators at different times of the day. Each run took 20 measurements of each component in the fixture. The measurement data was collected and analyzed using statistical analysis software. Both gauge repeatability and reproducibility, and gauge linearity and bias studies were conducted. The ICT GR&R percentage of study variation of the error was 6.08% (less than 10% is excellent). The percentage of bias for the reference average was 0.0 and the percentage of linearity was 0.10. Both are excellent. The percentage of error for a 0.050 Ohm resistor was less than 1% with a standard deviation of 0.000116 Ohm. This is proof that the ICT could be successfully used for the probability project.

#### Measurement System GR&R

This study was performed to ensure the entire measurement system (ICT and the ICT fixture) was repeatable and reproducible. Data for the GR&R study was obtained from the baseline experiment (see Section 5.0 below). A part was considered to be the same if the PCB target type (test pad or test via), probe style and probe force were identical. The physical location did not have to be the same. This is important to note, as those conducting the experiments using the measurement system would expect that identical onboard factors would yield the same results. Three operators ran four different boards each. A separate GR&R was conducted for each probe size. In all cases the percent of tolerance (% P/T) was in the excellent range (less than 10%) for 0.050", 0.075" and 0.100" probe sizes (0.039" probe size were excluded, see Section 6.4 below). The gauge standard deviation was so low (less than 0.0022 Ohm in all cases), that the measurement system was deemed suitable for the probeability project.

#### **Baseline Experiment**

This section describes the experiments that were undertaken to determine the value of an acceptable contact resistance.

#### **Goodness (specification limit)**

It was necessary to consider what would be a "good" or acceptable resistance reading. The value of 0.250 Ohm was chosen as the high specification limit for contact resistance. This was determined through baseline experiments and the evaluation of production test environments. All values below this limit would be considered 'good', and would not adversely affect ICT. Values above this limit would be considered to be outliers and would be analyzed. A contact resistance between 0.250 and 1.0 Ohm would be considered to be marginal as it may affect some in-circuit tests.

#### **Tin-Lead HASL and OSP Baseline Experiment**

The objectives of this experiment were to:

- Establish a best case ICT probe contact resistance. This would be used as a baseline, the benchmark against which future experiments with different board finishes, solder pastes etc. would be compared.

- Identify any factors of significance, or any interactions between various factors and levels.

- Establish a worse-case standard deviation for the screening experiment sample size calculations.

A probe making contact with a tin-lead soldered surface free of contaminants is an ideal target to hit with an ICT probe. A hot air solder levelled (HASL) board finish was chosen to collect the required data.

HASL probe vehicle boards were tested on an ICT and measurements were taken to gauge the total resistance of the probe receptacle, the probe and probe tip to the board (contact resistance). Table 1 shows the factors and levels included in this experiment.

|                     |                       | te 1 - HASE Baseline Fact |         |         |

|---------------------|-----------------------|---------------------------|---------|---------|

| Factors             | Level 1               | Level 2                   | Level 3 | Level 4 |

| Probe size          | 0.039"                | 0.050"                    | 0.075"  | 0.100"  |

| Probe style         | Chisel                | Non-Chisel                |         |         |

| Probe force         | 1-Low                 | 2-Standard                | 3-High  |         |

| Test pad size       | 0.025"                | 0.030"                    | 0.035"  |         |

| Test via size       | 0.000"                | 0.008"                    | 0.010"  | 0.012"  |

| All probes were ber | yllium copper finish. |                           |         |         |

Table 1 - HASL Baseline Factors and Levels

A total of 12 HASL probe vehicle boards were serialized and tested. The boards were tested in sequence, with tests repeated two more times for a total of 36 tests. Measurement data was collected from the ICT for each of the tests. This data was imported into statistical analysis software and analyzed to establish statistical means and variances for the contact resistance, versus the various factors and levels used in the experiment.

## Analysis of Results from the Baseline Experiment

The 0.100" high force chisel probe had the lowest mean resistance reading of all the different factors and levels.

Table 2 shows the results. Note the factors that have a P value less than the 0.05 threshold and that also have a large F value.

| Factor                        | Туре  | Levels   | Values   |            |         |        |

|-------------------------------|-------|----------|----------|------------|---------|--------|

| TpSize                        | fixed | 3        | 0.025"   | 0.030"     | 0.035"  |        |

| ViaSize                       | fixed | 4        | 0.000"   | 0.008"     | 0.010"  | 0.012' |

| ProbeSize                     | fixed | 4        | 0.039"   | 0.050"     | 0.075"  | 0.100' |

| ProbeForce                    | fixed | 3        | 1-Low    | 2-Standard | 3-High  |        |

| ProbeStyle                    | fixed | 2        | Chisel   | Non-Chisel |         |        |

| Analysis of Variance for HASI |       | •        | 1        |            |         | T      |

| Source                        | DF    | Seq SS   | Adj SS   | Adj MS     | F       | Р      |

| TpSize                        | 2     | 0.000701 | 0.000769 | 0.000384   | 1.10    | 0.334  |

| ViaSize                       | 3     | 0.000605 | 0.000726 | 0.000242   | 0.69    | 0.557  |

| ProbeSize                     | 3     | 2.224940 | 1.240145 | 0.413382   | 1180.70 | 0.000  |

| ProbeForce                    | 2     | 0.010457 | 0.010799 | 0.005399   | 15.42   | 0.000  |

| ProbeStyle                    | 1     | 0.010235 | 0.010005 | 0.010005   | 28.58   | 0.000  |

| TpSize*ViaSize                | 6     | 0.002065 | 0.002078 | 0.000346   | 0.99    | 0.432  |

| TpSize*ProbeSize              | 6     | 0.001027 | 0.000907 | 0.000151   | 0.43    | 0.858  |

| TpSize*ProbeForce             | 4     | 0.000643 | 0.000653 | 0.000163   | 0.47    | 0.760  |

| TpSize*ProbeStyle             | 2     | 0.000361 | 0.000375 | 0.000187   | 0.54    | 0.586  |

| ViaSize*ProbeSize             | 9     | 0.002476 | 0.002142 | 0.000238   | 0.68    | 0.728  |

| ViaSize*ProbeForce            | 6     | 0.001555 | 0.001563 | 0.000260   | 0.74    | 0.614  |

| ViaSize*ProbeStyle            | 3     | 0.001264 | 0.001300 | 0.000433   | 1.24    | 0.295  |

| ProbeSize*ProbeForce          | 6     | 0.018931 | 0.018837 | 0.003139   | 8.97    | 0.000  |

| ProbeSize*ProbeStyle          | 3     | 0.025686 | 0.024201 | 0.008067   | 23.04   | 0.000  |

| ProbeForce*ProbeStyle         | 2     | 0.000092 | 0.000092 | 0.000046   | 0.13    | 0.877  |

| Error                         | 518   | 0.181360 | 0.181360 | 0.000350   |         |        |

| LIIOI                         | 576   | 2.482399 |          |            |         |        |

| Table 2 - HASL   | General Linear Model |

|------------------|----------------------|

| 1 abit 2 - 11AbL |                      |

$S = 0.0187114 \quad R\text{-}Sq = 92.69\% \quad R\text{-}Sq(adj) = 91.88\%$

Factor significance:

- Probe size was the major contributor

- Probe style and probe force were minor contributors

- Test pad size and test via size were not significant contributors

#### Interactions:

- The major interaction took place between the probe size and probe head style

- There was a minor interaction between the probe size and probe force

#### **Conclusions from the Baseline Experiment**

- A PCB with a clean HASL finish is an excellent surface for ICT probes to make contact with. This includes all probe size, probe force and probe style combinations used in the experiment.

- The 0.100" probe had the lowest mean resistance reading of 0.01412 Ohm.

- Probe size was the dominant factor in contact resistance.

- Test pad size and via size were not significant (P value greater than the 0.05 threshold).

- There was an interaction between probe size and probe style.

An OSP board was run under identical conditions to identify whether there might be any special concerns using OSP in the screening and modelling experiments. No concerns were found.

#### **Finalizing Factors and Levels**

With the gauge studies complete, and the baseline specification limit of resistance established, the next step was to finalize the factors and levels for the screening experiment - including the process factors that were not designed into the board and the ICT fixture.

Paste 1 (tin-lead noclean) was used as a control in the experiment. Paste 2 (selected from Celestica's Lead Free qualification testing) was also used in the screening experiment.

The number of reflow cycles was set at one and four to cover all process extremes. Since OSP coatings are reduced through heat and the reaction with flux, four cycles would be a difficult test.

The time between reflow and test was thought to be an important factor for the test of OSP PCBs. For the purpose of the test, 15 minutes and 48 hours were selected. However, due to test control considerations, 48 hours was later changed to 60 hours.

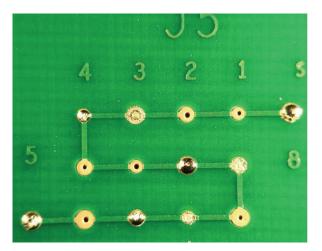

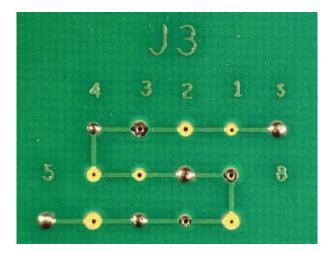

The last factor to be established was the test via / test pad solder configuration. The goal of the screening experiment was to determine if pasting vias would improve probability if the "right" configuration (stencil aperture design) was used. It was decided to test three configurations, convex, concave and no via fill (NVF). NVF refers to a configuration in which only the annular ring of the via is pasted and no paste enters the via hole. Appendix 2 (Figures 2.1 to 2.4) shows illustrations of these test pad and test via configurations.

#### **Stencil Design Experiment**

Prior to running the screening experiment, various stencil aperture designs were tested to ensure the three solder configurations could be achieved. A stencil was designed to validate 36 separate volume calculations (three distinct solder configurations, concave, convex and NVF on 12 different combinations of test pad and test via sizes).

A test board was printed and reflowed, and each joint was inspected at 30X magnification. A scoring system was used whereby 10 was the best (achieved target value) and one was the worst (opposite to target value; i.e. aiming for convex and the result was concave). A score of five was assigned to pads that ended up flat (i.e. neither concave nor convex).

The results were analyzed through an ANOVA general linear model but the results were inconsistent and inconclusive. It was determined the predominant factor causing the instabilities was via fill. Via fill was inspected and scored as yes, no or partial. Via fill was combined with via diameter and interactions were analyzed with the other factors through a second general linear model.

The paste did not consistently fill 0.008" and 0.010" via holes. As the HASL baseline analysis showed no statistical difference in results between 0.008", 0.010" and 0.012" via diameters, the decision was made to include only test pads and 0.012" test vias in the screening experiment.

#### Sample Size Calculations for the Screening Experiment

The objectives of the screening experiment were to understand which selected factors significantly affected the output measurement Y (resistance in Ohms) and to enable effective follow on modelling experiments.

A sample size calculation was necessary to ensure the capability to see the required amount of change to the output measurement Y, and to determine the quantity of boards required. The sample size calculations were probably the most difficult calculations performed during the project due to the challenge of understanding the number of runs present on the board (due to fixed fixture design and fixed board design) and how these runs married up with the three process factors not designed into the fixture and board. After extensive calculation, the number of boards required was determined to be 64. The boards were split into two 32-board sets, the first set with beryllium copper (BeCu) probes in the fixture and the second set with steel probes in the fixture.

#### **Screening Experiment**

Probe vehicle boards with an OSP finish were used and tests were performed with both tin-lead and Lead Free solder pastes.

For the screening experiment, the 0.008" and 0.010" test vias were eliminated from the test based on the results from the HASL and OSP baseline experiments, along with test pad diameter.

Consistent with the HASL baseline results, probe size had a large effect on both the mean and the standard deviation. For this reason, the experiment was redesigned to remove probe size as a four level factor, and each probe size was analyzed separately. This was necessary to gain visibility into the effects of the other factors and interactions. This allowed analysis of the experiment as an eight factor two level experiment design using statistical analysis software. Table 3 shows the screening experiment factors and levels.

| Factors                      | Level 1            | Level 2             | Level 3 | Level 4 |

|------------------------------|--------------------|---------------------|---------|---------|

| Paste type                   | Paste 1 (Tin-Lead) | Paste 2 (Lead Free) |         |         |

| Number of reflow cycles      | 1                  | 4                   |         |         |

| Time between reflow and test | 15 minutes         | 60 hours            |         |         |

| Stencil design               | Convex             | NVF                 |         |         |

| Probe size                   | 0.039"             | 0.050"              | 0.075"  | 0.100"  |

| Test target type and size    | Pad                | 0.012" Via          |         |         |

| Probe force                  | 1-Low              | 3-High              |         |         |

| Probe style                  | Chisel             | Non-Chisel          |         |         |

Table 3 - Screening Experiment Factors and Levels

Runs were not fully randomized as boards with paste 2 were run together followed by boards with paste 1. Set-up times at screen printing and reflow would have inhibited meeting the required test time requirements from last reflow if runs had been intermixed.

Factor significance:

- For 0.100" probes the main contributor was probe force, followed by time between reflow and test.

- For 0.075" probes the main contributor was probe force paste type had a very small effect.

- For 0.050" probes the main contributor was stencil aperture design, followed by probe force, followed by probe style.

- 0.100" and 0.075" probes are extremely robust. The large process window means probe force can be decreased to reduce board strain.

- Convex solder configurations outperformed NVF on 0.100", 0.075" and 0.050" probe sizes. Results varied by probe style.

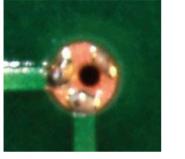

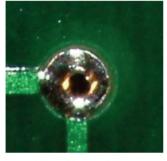

- The increased surface tension and decreased wettability of Paste 2 prevented an even flow of solder around the annular ring of the NVF configuration. This resulted in the only significant difference between the Lead Free and tin-lead pastes, as illustrated in Appendix 2 (Figure 2.5).

Interactions:

• For 0.050" probes there was an interaction between stencil aperture design, probe force and probe style.

The focus of the follow-on modelling experiment was to:

- Optimize parameters for 0.050" probe size, which would also ensure robust results for 0.100" and 0.075" probes.

- To improve the performance of 0.050" probes, by fully characterizing the interactions between stencil aperture design, probe force and probe style.

• Contrary to what was understood before undertaking the experiment, a short time between reflow and test negatively impacted performance under certain conditions. The modelling experiment would need to include factor levels closer to the low end (0.25 hours), so that the effect could be fully characterized and understood.

#### 0.039" probe measurement variation

One of the key findings during the screening experiment was a significant variation in the measurement data for the 0.039" probes. Analysis from the experiment resulted in questions surrounding the measurement system, indicating that specific reference designators were impacting 0.039" resistance above and beyond the experiment factors and levels.

For all probe sizes, the ICT fixture had been designed to make four terminal measurements. During investigation of the 0.039" measurement variation it was discovered that the fixture had been wired incorrectly due to difficulty in attaching two wires to the same 0.039" receptacle. The four terminal measurements were taking place back at the interface inside the ICT fixture. Therefore, measurements for 0.039" probes contained the resistance of the wires as well as the receptacle, probe and contact resistance. At this stage it was decided not to correct the 0.039" wiring error and this probe size was removed from follow-on experiments.

#### Beryllium copper versus steel probes

This experiment was conducted to determine if there was a contact resistance difference between beryllium copper and steel probes. After analyzing the first 32 boards tested during the first screening experiment, it was deemed necessary to look at the differences between probe finishes in a more cost effective manner than running another screening experiment with another 32 boards. Three HASL boards and three OSP boards were used to conduct the test. Table 4 lists the probe factors used in the experiment.

|                           | Table I HAU | ine ractors and Levels | ,          |            |

|---------------------------|-------------|------------------------|------------|------------|

| Factor                    | Level 1     | Level 2                | Level 3    | Level 4    |

| Probe Size                | 0.039"      | 0.050"                 | 0.075"     | 0.100"     |

| Probe Style               | Chisel      | Non-Chisel             |            |            |

| Probe Force               | 1-Low       | 2-Standard             | 3-High     |            |

| Test point Size           | 0.025"      | 0.030"                 | 0.035"     |            |

| Test target type and size | Pad         | 0.008" Via             | 0.010" Via | 0.012" Via |

Table 4 - Fixture Factors and Levels

The ANOVA general linear model was used to analyze the data generated from this experiment. No statistically significant differences were found between beryllium copper and the steel probes on HASL or OSP board finishes.

#### **Modelling Experiment**

Analysis of the screening experiment results led to the design of seven full factorial modelling experiments.

#### Sample Size Calculations for the Modelling Experiment

As with the screening experiment, a sample size calculation was necessary to ensure the capability to see the required amount of change to the Y output (resistance in Ohms) and to determine the quantity of boards required for the seven modelling experiments.

Due to the significant scope of this experiment, careful consideration was given to the physical ability to conduct the test accurately under the same environmental and process set-up conditions. A spreadsheet was developed in order to closely model throughput through the screen printer, reflow and ICT, against the time between reflow and test requirements. This was done for every board serial number, in order to look for conflicts.

#### **Modelling Experiment Overview**

A total of seven full factorial experiments were designed and run:

- 0.100" pad

- 0.100" via

- 0.075" pad

- 0.075" via

- 0.050" pad

- 0.050" via

- 0.050", 0.075" and 0.100" bare copper

96 boards were used in the pasted experiments and 12 boards were used in the bare copper experiments.

## S40-01-8

As probe style was statistically significant in the screening experiment, the range of probe styles was expanded in the various modelling experiments. Steel finish probes were used in the fixture. Table 5 lists the factors and levels used in the modelling experiments.

| Factor                   | Level 1            | Level 2    | Level 3     | Level 4 |

|--------------------------|--------------------|------------|-------------|---------|

| Paste type               | Paste 1 (Tin-Lead) | Paste 2    | Paste 3     | Paste 4 |

| Time from reflow to test | 5 minutes          | 70 minutes | 135 minutes |         |

| Number of reflow cycles  | 1                  | 2          |             |         |

| Stencil Design           | Concave            | Convex     | NVF         |         |

| Probe style              | Chisel             | Non-Chisel |             |         |

| Probe force              | 1-Low              | 2-Standard | 3-High      |         |

#### **Table 5 - Modelling Experiment Factors and Levels**

In the modelling experiments, concave solder configurations were added for test vias to confirm the assumptions that concave fillets would hold flux and cause high resistance readings. These assumptions were proved correct. Concave fillets caused a high percentage of outlier readings and, therefore, skewed the data. Concave results were removed from the data and the experiments leaving convex and NVF levels for stencil aperture design.

Each non-concave outlier (greater than 0.0250 Ohm) was inspected under a microscope for:

- Presence and quantity of flux on test pad, test via and test probes.

- Depth of probe penetration.

- Location of the probe contact relative to the test pad / test via.

- Variations in factor levels from planned to actual (such as convex pads that may have come out relatively flat or at times concave)

The major focus of the modelling experiment analysis was to develop optimal recipes across the four paste types that would minimize overall ICT contact resistance and contact failures.

All pasted results were compared with bare copper results. Results are shown for 0.050" via pasted and 0.050" via bare copper.

#### Modelling Experiment 0.050" via Pasted Results

The following is a summary of the results of microscope inspection for each outlier:

- Flat pad with a great deal of flux

- Flat pad with a great deal of flux (looked similar to cracked ice on a frozen lake)

- Slightly convex pad with a great deal of flux (looked almost like shellac)

- Slightly convex pad with a great deal of flux (looked even thicker then shellac)

- Concave pad with a great deal of flux in a pocket

- No evidence of pin contact or pin penetration (for NVF)

- No evidence of pin penetration into bare copper (for NVF)

All the six main factors had a statistically significant effect on the mean:

- Paste type

- Time from reflow to test

- Number of reflow cycles

- Stencil design

- Probe style

- Probe force

28 two-way interactions proved to be statistically significant. 40 three-way, 30 four-way and 22 five-way interactions were also statistically significant. Stencil design versus probe style had the largest effect on the mean.

There were definite differences in which pastes created more outliers.

## Modelling experiment 0.050" via bare copper results

The following is a summary of the results of microscope inspection for each outlier:

- No evidence of pin contact

- Very poor penetration

The only factor that was statistically significant was the number of reflow cycles.

The time from reflow to test, probe style and probe force factors were not statistically significant.

Seven two-way, one three-way, and two four-way interactions were statistically significant.

#### **Primary Conclusions**

The primary conclusions are as follows:

1) This project has characterized the effects of test pin probability on tin-lead and Lead Free SMT soldered test pads and test vias on boards with an OSP finish and has developed complete recipes for success. These recipes are robust for all factor settings. Using the parameters that were established:

- A worst case CPk for ICT contact of 2.11 is achieved which equates to a 6.33 sigma level of process quality.

- A best case CPk of 28.15 is achieved which equates to an 84.45 sigma level of process quality.

2) Each Lead Free paste responded somewhat differently to most factor levels when compared with each other and with the tin-lead control paste.

- There were no significant differences in performance of three pastes (paste 1, paste 2 and paste 3) as they relate to the optimized and robust parameters developed.

- All three of the paste types will yield a very low, very high-performing mean and standard deviation with the optimized parameters.

- Paste 4 also performed well and yielded comparable results to the other three pastes. It behaved very differently and required a different set of optimized parameters.

- Optimized parameters will yield zero outliers (greater than 0.250 Ohm).

3) When testing boards with an OSP surface finish, all test pads and test vias, greater than or equal to 0.012", should be pasted using any of the four pastes with the appropriate optimized parameters.

• It is best to paste test pads and test vias with a convex "dome". This provides flux with the best chance to "pool" around the base of the dome, leaving the dome clear for probing.

4) ICT contact resistance is not appreciably impacted with the introduction of Lead Free solder into the SMT process, when optimized parameters are utilized.

#### **Other Conclusions and Key Learnings**

Other conclusions and key learnings are as follows:

1) The physical appearance, volume and mechanical properties of the three Lead Free paste residues were dramatically different:

- Paste 2 left a large volume of yellow flux residue that was very brittle.

- Paste 3 left a very large volume of very thick and more ductile residue that was clear almost like thick varnish or shellac.

- Paste 4 left a very small volume of residue. It was very hard to see until alcohol was applied which turned the residue white.

2) There were statistically significant differences in the number of outliers between the four pastes. Excluding the tin-lead control, paste 4 created less outliers when concave fill was included in the analysis.

3) Paste 4 was the best performing paste under certain process conditions (factor levels), it was also the worst performing paste under certain process conditions (factor levels).

- For 0.050" and 0.075" probe sizes it performed best at five and 70 minutes from reflow to test, but was dramatically worse at 135 minutes.

- For 0.100" probe size it performed best at 70 and 135 minutes from reflow to test, but worse at five minutes.

4) NVF was eliminated as a potential test target for three important reasons:

- Convex outperformed NVF in most instances from an optimization and outlier standpoint.

- NVF is not possible to achieve using Lead Free pastes. Due to the reduced wettability of the Lead Free pastes, the solder will not wet around the annular ring of the via. If the stencil was designed to apply paste to almost the whole annular ring area, the volume would be too high and would cause catastrophic concave fill. Stencils can not be stepped in thickness as test vias are typically located all over the board.

- NVF is also difficult to achieve using tin-lead pastes. Even if volume calculations are perfect, natural variation will cause some catastrophic concave fill, or, if the volume is held on the conservative side, the whole annular ring of the joint will not be wetted.

5) There was a very strong interaction between the shape of the convex pad and the tendency to create an outlier. Almost all non-bare copper outliers had pads that were slightly convex or flat, and on a few occasions, concave. Flux would form over the slightly convex pad, resembling ice on a frozen lake. If the pad was highly convex the flux would "pool" around the base of the pad and would not cause high resistance unless the probe was significantly misaligned and hit the edge of the pad where the flux had gathered.

6) The strong performance of standard force probes is excellent news, as board stresses can be dramatically reduced.

7) Convex solder is the best test target.

- Bare copper is next best test target. Acceptable contact cannot be achieved with some probe styles on bare copper.

- Concave solder is the worst test target. Acceptable contact cannot be achieved with 0.050", 0.075" or 0.100" probes on concave solder.

## **Recipes for Achieving Good ICT Test Probe Contact**

Recipes developed with robust, optimized parameters will not be reproduced here. However, the following statements are made.

Robust, optimized recipes are valid for:

- Three paste types (paste 1, paste 2 and paste 3)

- Paste 4 requires a different recipe

- Times between reflow and test of five, 70 or 135 minutes

- One or two reflow cycles

- Test pads and test vias that have convex solder targets

- Test pads and test vias that have bare copper targets

#### Observations:

- All robust, optimized recipes produce zero outliers (greater than 0.250 Ohm).

- High probe force is only required in 11% of all combinations.

- The contact resistance mean increases as probe size decreases in 100% of all combinations.

- The contact resistance mean for convex solder targets is lower than bare copper targets in 75% of all combinations. The contact resistance mean only marginally increases in the remaining 25% of combinations.

- The contact resistance standard deviation for convex solder targets is lower than bare copper targets in 92% of all combinations.

- When "typical" noclean probe styles and forces are substituted into the recipes they are no longer robust. Outliers are created, and contact resistance means and/or standard deviations increase.

- There was no statistical difference between beryllium copper and steel probes within the scope of this project. Probe wear was not evaluated.

#### **Further study**

There are many opportunities for further study, but some of the possibilities are as follows:

- Evaluate a different RoHS compliant board finish

- Testing with a larger volume of boards for a detailed analysis of recipes, outliers and accumulation of flux

- Further evaluation of 0.008" and 0.010" via fill

- Evaluation of probe wear and preventative maintenance

#### Lead Free Production Experiences

Before the results of this study were available, a high-volume Lead Free board tested with ICT was introduced into manufacturing. Some of the details of this board are as follows:

| Board finish | OSP                                                  |

|--------------|------------------------------------------------------|

| Board size   | 10" x 13"                                            |

| Node count   | 827 nodes                                            |

| Probe sizes  | mostly 0.100" and 0.075", a small quantity of 0.050" |

| Probing      | top-side and bottom-side                             |

| Top-side     | test pads soldered at REFLOW                         |

| Bottom-side  | test pads soldered at WAVE                           |

| Process      | NOCLEAN                                              |

The ICT probing strategy for this Lead Free OSP noclean board was the same as that normally applied to a tin-lead OSP noclean board:

- Reduce and monitor the amount of WAVE flux applied

- Best practice probe cleaning and fixture maintenance

- Aggressive style of probes

- Minimize the time from reflow to ICT

- Stencil design to create top-side convex (dome) test targets

There were some Lead Free considerations:

- The ICT fixture acceptance included strain gauge analysis to ensure no high strains were applied to the board during ICT.

- The type of WAVE flux used had a high content of rosin which made the board sticky.

At the time this paper was written, yields, false fails and defect paretos were being monitored.

This particular Lead Free OSP noclean board did not introduce any additional ICT contact challenges when compared to an equivalent tin-lead OSP noclean board.

#### Acknowledgements

The author would like to particularly thank the following: Steve Konsowitz, Jeff Avitabile, Jeff Watt, Tom Dunn and Lynn Klev for their significant and professional contributions to this study; Steve Brown for his support throughout this study.

Also a special thanks to the following for their valuable contributions: Don Hersey, John McMahon, Chris Johnson, Hamdy Elarabi, Joe Laurencio, Junior Rozen, Bob Silva, Helena Cassin and Henry Fitzsimmons.

All of the above are Celestica personnel, apart from Tom Dunn of Dbar Innovations.

#### References

[1] Andrew Pollock, "Inspection of Lead Free Solder Joints on Printed Circuit Assemblies Using Automated Inspection Techniques" *SMTA 2004*.

[2] Patrick Roubaud, "iNEMI Pb-free Assembly & Rework of IPC Class 2 Assemblies, Process Robustness Assessment" *APEX, Anaheim, California 2005.*

[3] Steve Konsowitz, Jeff Avitabile, Jeff Watt and Tom Dunn (Dbar Innovations), "Pb-Free ICT Test Probability for OSP Board Surface Finish". *Celestica Internal Document 2005*.

## Appendix 1

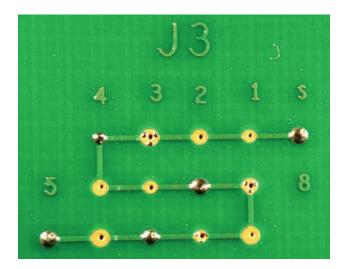

Figure 1.1 - Probe Vehicle Board

Figure 1.2 - Probe Vehicle Board Close Up View of One Test Block

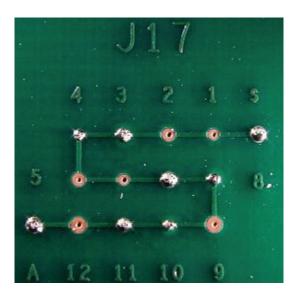

Figure 2.1 - Convex Solder Configuration on Pins 3, 4, 7, 8, 10 and 11

Figure 2.2 - Concave Solder Configuration on Pins 3, 8 and 10

Figure 2.3 - NVF Solder Configuration for Tin-Lead on Pins 3, 8 and 10

## S40-01-14

## Appendix 2 (continued)

Figure 2.4 - NVF Solder Configuration for Lead Free on Pins 3, 8 and 10

# No Via Fill Example