The Institute for Interconnecting and Packaging Electronic Circuits 2215 Sanders Road • Northbrook, IL 60062

# IPC-TM-650 TEST METHODS MANUAL

**1 Scope** The object of a planarity measurement is to determine the effectiveness of a polymer thin film in smoothing topological features created by underlying layers of circuitry or etch patterns. In this case, the polymer thin film is a dielectric material for use in High Density Interconnect (HDI) and microvia technologies.

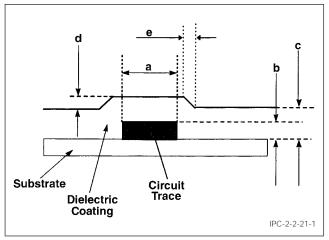

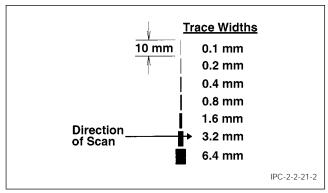

**1.1 Test Structure** Schematics given in Figure 1 (end view) and Figure 2 (top view) depict the essential features of a recommended test structure for measuring the planarity as a function of feature size.

Figure 1 Cross-Section Planarization Diagram

Figure 2 Top View of Planarization Structure

| Number<br>2.2.21                                                                                  |          |  |

|---------------------------------------------------------------------------------------------------|----------|--|

| Subject<br>Planarity of Dielectrics for High Density<br>Interconnection (HDI)/Microvia Technology |          |  |

| Date<br>11/98                                                                                     | Revision |  |

| Originating Task Group<br>HDI Test Methods Task Group (D-42a)                                     |          |  |

|                                                                                                   |          |  |

In the finished test structure, "d" is the step height over the circuit trace after the polymer has been deposited and cured. The planarity is dependent on the trace height, "b," the polymer coating thickness, "c," and the trace width, "a." Rather than fully characterizing this relationship for each polymer coating, it is best to use simplified standard procedures for measurement and for comparing different types of coatings.

Planarity is also affected by the proximity of the line feature being used for measurement to any neighboring topological feature in the test structure. Planarity is generally much lower for isolated features. Therefore, in order to consider the "worst case" conditions, isolated lines are preferred in the test structure. To satisfy this requirement, no neighboring features can be within fewer than 15 line widths of the line in question.

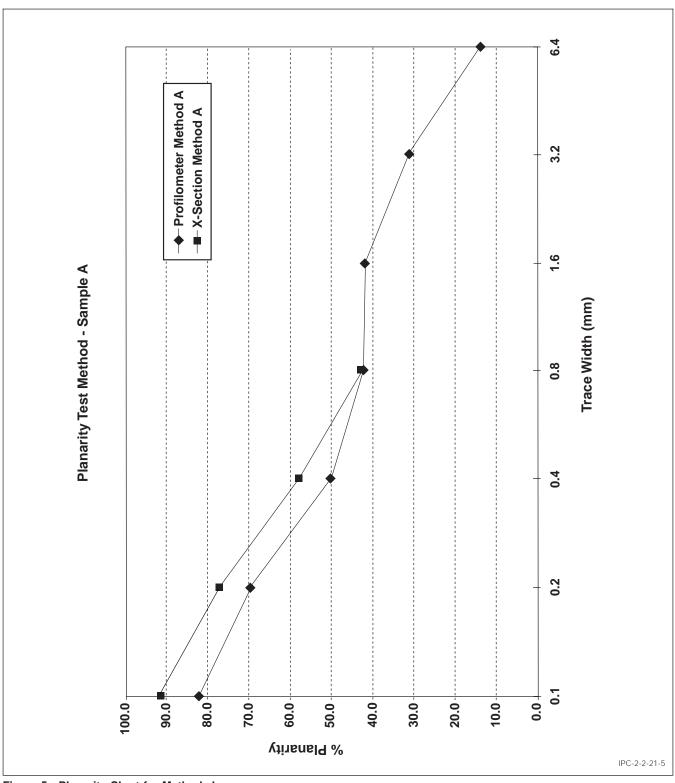

The test pattern in Figure 2 is recommended as one that provides planarity characterization over a broad range of feature sizes. All lines are isolated in accord with the above guideline. It is recommended planarity be determined over the complete range of these widths (but the specific nominal values within that range are not important). Normally, one finds the planarity is high over narrow lines, but it progressively rolls off in proceeding toward wider ones. The roll-off rate is important, and it varies from polymer to polymer. Thus any report of planarity must include the line width measured and, preferably, a plot of planarity versus line width should be reported.

### 2 Applicable Documents

**IPC-DD-135** Qualification for Deposited Organic Interlayer Dielectric Materials for Multi-Chip Modules

### 3 Test Specimens

**3.1 Prepare Test Coupons** Prepare the surface of the test structure for polymer deposition in accordance with the procedure recommended by the manufacturer of the dielectric coating (follow all procedures for cleaning the surface and for deposition of a coupling agent if one is recommended). Coat the polymer resin in accordance with the manufacturer's recommended procedure to provide an average film thickness of 63.5  $\mu$ m (± 10%) for 18  $\mu$ m copper over the substrate surface when the cure is completed. Cure the polymer thin film using

Material in this Test Methods Manual was voluntarily established by Technical Committees of the IPC. This material is advisory only and its use or adaptation is entirely voluntary. IPC disclaims all liability of any kind as to the use, application, or adaptation of this material. Users are also wholly responsible for protecting themselves against all claims or liabilities for patent infringement. Equipment referenced is for the convenience of the user and does not imply endorsement by the IPC.

| IPC-TM-650 |                                                                                         |       |  |

|------------|-----------------------------------------------------------------------------------------|-------|--|

| Number     | Subject                                                                                 | Date  |  |

| 2.2.21     | Planarity of Dielectrics for High Density Interconnection (HDI)/<br>Microvia Technology | 11/98 |  |

| Revision   |                                                                                         |       |  |

|            |                                                                                         |       |  |

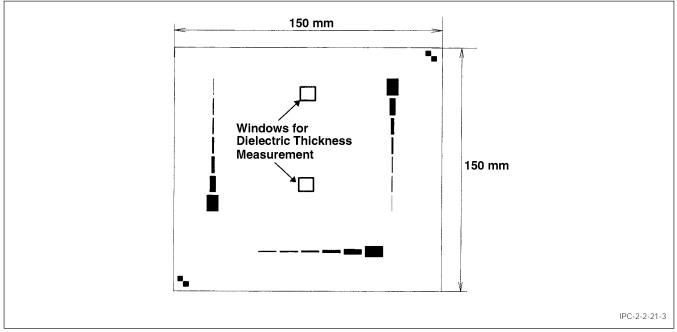

all steps recommended for full curing. For resin coated copper (RCC) foil, after laminating the foil, cure as per manufacturer's instructions, then etch the copper layer and proceed as for other deposited dielectric materials (see Figure 3).

**4 Equipment/Apparatus** This method uses profilometer measurements providing topological height variations as a function of displacement across the surface of a standard test structure.

Use a TENCOR Profilometer (Model: Alpha Step 200). Substitutions are acceptable, provided they can measure feature heights in the range used to within  $\pm$  2% and can provide a linear scan of at least 10 mm.

**Note:** As an alternate method, where a profilometer is not available, the measurements can be collected by cross-sectioning the test structures. This method will require one cross-section for each trace width in order to collect data for trace width effects.

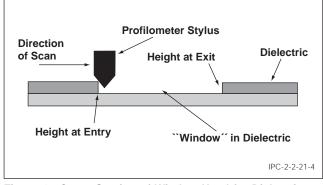

**5 Procedure** Prior to the polymer deposition, scan the profilometer stylus across all copper lines in the test structure, scanning in the direction indicated by the arrow in Figure 2. Measure and record the dimensions depicted as "a" and "b" in Figure 1 for each of the lines. After polymer deposition and cure, measure the polymer film thickness at a location distant (at least 15 line widths) from any of the test structure's copper lines. In order to do this, a ''window'' must be imaged in the dielectric down to the substrate. A ''window'' to the substrate may be opened by photo-imaging, chemical dissolution, laser ablation, or other appropriate method (see Figure 4). The sweep must allow measurements of the thickness of the dielectric entering and exiting the ''window.'' These measurements should be within  $\pm$  0.2 µm of each other. Record this dielectric thickness as dimension ''c.''

Finally, measure the dimension shown in Figure 1 as the feature step height "d" of the polymer; use the profilometer, not an optical method. In measuring "d," take the difference in height between the highest point on top of the copper line and the lowest point at least 15 line widths from the line to be measured.

# 5.1 Conditions of Test

**5.1.1** Calibrate the profilometer before making measurements using the calibration procedure specified by the manufacturer of the equipment.

**5.1.2** Measure at ambient room temperature and humidity.

Figure 3 Pattern of One Test Board Showing Three Test Substructures (Board is 150 mm sq.)

| IPC-TM-650 |                                                                                         |       |  |

|------------|-----------------------------------------------------------------------------------------|-------|--|

| Number     | Subject                                                                                 | Date  |  |

| 2.2.21     | Planarity of Dielectrics for High Density Interconnection (HDI)/<br>Microvia Technology | 11/98 |  |

| Revision   | - Microvia reenhology                                                                   |       |  |

|            |                                                                                         |       |  |

Figure 4 Cross Section of Window Used for Dielectric Thickness Measurement

**5.1.3** To standardize measurements, use test structures in which  $b = 18 \ \mu m$ ,  $c = 63.5 \ \mu m$ , and the ratio of c/b is  $3.5 \pm 0.2$ . If a dielectric film is used, which has been produced at a fixed thickness other than that outlined above, maintain a c/b ratio as described. If the standard construction with this defined ratio cannot be maintained, the actual metal and dielectric thickness must be reported.

**5.1.4** Make triplicate measurements and average the results at each line width.

# 5.2 Calculation of Planarity

**5.2.1** Planarity for an individual trace,  $P_{a}$ , can be defined by the following equation:

$P_a = (1 - d/b)100$

where "a" is the trace width, "d" is the bump height over the trace, and "b" is the copper trace height. For an ideal planar structure, the value of P is equal to 100%.

**5.2.2** Average planarity,  $P_{ave}$ , for a given trace width is calculated using the triplicate measurements:

$$P_{ave} = (P_{a1} + P_{a2} + P_{a3}) / 3$$

**5.2.3** Total average planarity,  $P_{total}$ , is the average planarity for all widths of traces (where n = number of traces widths measured):

$P_{total} = (P_{ave1} + P_{ave2} + \dots + P_{ave n}) / n$

# 5.3 Report

**5.3.1** Report the average planarity for each trace width measured (see 5.2.2).

**5.3.2** Report the total average planarity as a single average percentage of all seven trace width averages (see 5.2.3).

**5.3.3** Also report the technique, profilometer or cross-section, used to obtain the measurements.

This calculation can be performed for each trace width to develop a planarity plot.

# 6 Notes

**6.1 Cross Section Method** Due to the field of view required for the larger trace widths (> 0.8 mm), accurate measurements of the dielectric "bump" may not be possible due to the low magnification. One option is to use a higher magnification and measure the total dielectric and copper trace height from the substrate surface and subtract the minimum dielectric height over the substrate alone.

**6.1 Planarity Test Method Sample** An example of a planarity test method is given in Figure 5.

| IPC-TM-650 |                                                                                         |       |  |

|------------|-----------------------------------------------------------------------------------------|-------|--|

| Number     | Subject                                                                                 | Date  |  |

| 2.2.21     | Planarity of Dielectrics for High Density Interconnection (HDI)/<br>Microvia Technology | 11/98 |  |

| Revision   |                                                                                         |       |  |

|            |                                                                                         |       |  |

Figure 5 Planarity Chart for Method.xls