# IPC-9203A

# Users Guide to IPC-9202 and the IPC-B-52 Standard Test Vehicle

Developed by the Residue Assessment Task Group (5-32g) of the Cleaning and Coating Committee (5-30) of IPC

### Supersedes:

IPC-9203 - April 27, 2012

Users of this publication are encouraged to participate in the development of future revisions.

Contact:

**IPC**

Tel 847 615.7100 Fax 847 615.7105 November 2022 IPC-9203A

# **Table of Contents**

| 1.0 II  | NTRODUCTION                                                                  | 3.2.8   | Other Board Features.                   | 14 |

|---------|------------------------------------------------------------------------------|---------|-----------------------------------------|----|

| 1.1     | Definitions                                                                  | 3.2.8.1 | Fiducials                               | 14 |

| 1.1.1   | Process Characterization                                                     | 3.2.8.2 | Contact Fingers                         | 14 |

| 1.1.2   | Qualification                                                                | 3.3     | Board Design Modifications              | 14 |

| 1.1.3   | Validation                                                                   | 3.4     | Electronic Data                         | 15 |

| 2.0 A   | APPLICABLE DOCUMENTS                                                         | 3.5     | Formal Drawing                          | 16 |

| 2.1     | IPC                                                                          | 3.6     | Additional Patterns                     | 16 |

| 2.2     | International Electrotechnical Commission                                    | 3.7     | Bill of Materials (BOM)                 | 16 |

|         | (IEC)                                                                        | 3.8     | Known Variations on the IPC-B-52 Design | 17 |

| 3.0 T   | THE IPC-B-52 TEST VEHICLE                                                    | 3.8.1   | Variant 1                               | 17 |

| 3.1     | Revision History                                                             | 3.8.2   | Variant 2                               | 18 |

| 3.1.1   | Original IPC-B-52                                                            | 3.9     | How Much Change Is Allowed?             | 18 |

| 3.1.2   | Revision A to Revision B                                                     | 4.0 II  | PC-9202 POINTS FOR CONSIDERATION        | 18 |

| 3.1.3   | ummary of Changes – Revision A to B 4                                        | 4.1     | Process Qualification                   | 23 |

| 3.1.4   | What Did Not Change – Revision A to B 4                                      | 4.2     | Testing at 85/85                        | 29 |

| 3.1.5   | IPC-B-52 Revision B 4                                                        | 4.2.1   | Initial and Final Measurements          | 30 |

| 3.2     | The Main SIR Test Board 5                                                    | 4.2.2   | Test Duration                           | 30 |

| 3.2.1   | The Ion Chromatography (IC) Test Coupon 6                                    | 4.2.3   | Data Rounding                           | 31 |

| 3.2.3   | The SIR Mini Coupon 6                                                        | 4.2.4   | Data Exclusion                          | 32 |

| 3.2.4   | The Test Patterns                                                            | 5.0 C   | OTHER USEFUL INFORMATION                | 33 |

| 3.2.5   | Connector Patterns                                                           | 5.1     | Test Sample Surface Finish              | 33 |

| 3.2.5.1 | Pattern 1 – Connector J2 8                                                   | 5.2     | Test Sample Identification              |    |

| 3.2.5.2 | Pattern 16 – Connector J1                                                    | 5.3     | Manufacturing Processes                 |    |

| 3.2.5.3 | Pattern 4 – SM IEEE1386 Connector 9                                          | 5.4     | Test Sample Review                      |    |

| 3.2.5.4 | Capacitor Patterns                                                           | 5.5     | Testing for Electrical Shorts           |    |

| 3.2.5.5 | Pattern 2 – 0402 Capacitor Field 9                                           | 5.6     | Handling During Review                  | 34 |

| 3.2.5.6 | Patterns 5 and 8 – 0805 Capacitor Field 10                                   | 5.7     | Storage Until Testing.                  |    |

| 3.2.5.7 | Pattern 14 – 0603 Capacitor Field                                            | 5.8     | Packaging for Shipment                  |    |

| 3.2.5.8 | Pattern 15 – 1206 Capacitor Field                                            | 5.9     | When Test Runs Have Issues              |    |

| 3.2.6   | SMT Devices                                                                  | 5.10    | Interrupted Tests                       |    |

| 3.2.6.1 | Pattern 3 – PGA Pattern                                                      | 5.11    | Premature Ending of the Test            |    |

| 3.2.6.2 | Patterns 6 and 7 – QFP160 Lead to<br>Lead Pattern (6) and QFP160 Comb (7) 12 | 5.12    | Handling Outliers                       | 35 |

| 3.2.6.3 | Patterns 9 and 10 – QFP80 Comb Pattern (9) and QFP80 Lead to Lead            |         | REFERENCES                              |    |

| 3.2.7   | Open Areas (11 and 12) for Custom Patterns 13                                |         |                                         |    |

IPC-9203A November 2022

| Figure 3-1a  | Original IPC-B-52 Board (Circa 2004),             | Figure 3-17a | ,Top Side                                          |

|--------------|---------------------------------------------------|--------------|----------------------------------------------------|

|              | Top Side                                          | Figure 3-17b | Bottom Side                                        |

| Figure 3-1b  | Original IPC-B-52 Board (Circa 2004), Bottom Side | Figure 3-17c | ,Top Side                                          |

| Figure 3-2   | IPC-B-52 Board Revision A                         | Figure 3-17d | Bottom Side                                        |

| Figure 3-3   | IPC-B-52 Revision B,                              | Figure 3-18a | BGA Pattern                                        |

| rigure 3-3   | Full Board – Top Side                             | Figure 3-18b | $Soldered\ BGA\ Component\ \dots\dots\dots12$      |

| Figure 3-4   | IPC-B-52 Revision B, Full Board –                 | Figure 3-19a | QFP 160 Patterns                                   |

|              | Bottom Side                                       | Figure 3-19b | Soldered QFP 160 Component                         |

| Figure 3-5a  | IPC-B-52B, SIR Board5                             | Figure 3-20a | QFP80 Patterns                                     |

| Figure 3-5b  | IPC-B-52B, SIR Board5                             | Figure 3-20b | Soldered QFP80 Component                           |

| Figure 3-6   | IPC-B-52B, Assembled SIR Board 5                  | Figure 3-21a | SOIC Pattern                                       |

| Figure 3-7a  | Ion Chromatography (IC) Coupon6                   | Figure 3-21b | Soldered SOICs                                     |

| Figure 3-7b  | Ion Chromatography (IC) Coupon with               | Figure 3-22a | Open Area                                          |

|              | Components 6                                      | Figure 3-23  | IPC-B-52 Revision B with QFN Patterns              |

| Figure 3-8   | Solder Mask Adhesion Coupon 6                     |              | in Open Area                                       |

| Figure 3-9   | SIR Mini Coupon6                                  | Figure 3-24  | Fiducials14                                        |

| Figure 3-10a | IPC-B-52 Patterns, Top Side                       | Figure 3-25  | Contact Fingers                                    |

| Figure 3-10b | IPC-B-52 Pattern, Bottom Side 8                   | Figure 3-26  | IPC-B-52 Diagram for Bill of Materials             |

| Figure 3-11a | J2 Connector Pattern                              |              | (BOM)                                              |

| Figure 3-11b | J2 Connector Installed 8                          | Figure 3-27  | Effect of Capacitance                              |

| Figure 3-12a | SMT Connector Pattern                             | Figure 3-28  | IPC-B-52 QFN Variant 1                             |

| Figure 3-12b | SMT Connector Installed9                          | Figure 4-1   | Connector Check Card24                             |

| Figure 3-13a | 0402 Capacitor Pattern9                           | Figure 4-2   | SIR Chart                                          |

| Figure 3-13b | 0402 Soldered Capacitors 9                        | Figure 4-3   | SIR Levels at Different Test Conditions $\dots 32$ |

| Figure 3-14a | 0805 Capacitor Pattern, Top Side 10               |              | Tables                                             |

| Figure 3-14b | 0805 Soldered Capacitors, Top Side 10             | Table 3-1    | IPC-B-52 Revision B, Bill of Materials             |

| Figure 3-14c | 0805 Capacitor Pattern, Bottom Side 10            |              | (BOM)                                              |

| Figure 3-15a | 0603 Capacitor Patterns                           | Table 3-2    | IPC-B-52 Variant - Components                      |

| Figure 3-15b | 0603 Soldered Capacitors                          | Table 4-1    | Voltage Gradients                                  |

| Figure 3-16a | 1206 Capacitor Pattern                            | Table 5-1    | IPC-B-52 Pinout                                    |

| Figure 3-16h | 1206 Soldered Capacitors 11                       |              |                                                    |

November 2022 IPC-9203A

# Users Guide to IPC-9202 and the IPC-B-52 Standard Test Vehicle

#### **FOREWARD**

The electronics manufacturing process is often very complex, with dozens of variables that impact the quality and reliability of the manufactured assemblies in the end use environment. Of concern are the kinds of residues remaining on the electronic assembly and the effects that these residues have on the electro-chemical reliability of the end-product.

Surface Insulation Resistance testing measures changes to the surface insulation resistance. By its very nature, such testing must be conducted on a test coupon that should be representative of the intended end-product.

Apart from commonplace ionic residues, most modern process chemistries include non-ionic surfactant additives that are not detectable using ionic extract test methods such as Ion chromatography or Resistivity of Solvent Extracted (ROSE).

This document focuses on the IPC-B-52 standard test assembly and how it is used as a representative example of the intended end-product.

#### 1.0 INTRODUCTION

In order to determine acceptable electro-chemical performance, the most suitable test is to run SIR using a test coupon that is representative of the intended end-product material set.

The advantage of this approach is that it does not differentiate between ionic nor non-ionic matter that may be deleterious to end-product performance. Other test methods, such as Ion Chromatography or ROSE are not able to detect or measure non-ionic contaminants.

There are many other test methods that are used to ascertain what is present as and when an SIR "failure" is detected.

The IPC-B-52 test vehicle is intended to be used to evaluate and optimize a manufacturing process, and to provide objective evidence that a chosen manufacturing material set, and manufacturing process is electro-chemically compatible. This latter use is often considered as a "process validation", suitable for international specifications such as IPC J-STD-001 or IEC-61189-5-502. Such efforts are not trivial, and often an engineering analysis is required to determine the meaning of the resulting data set.

The predecessor to the IPC-B-52 was the IEC TB-57 test coupon. This was originally designed by the National Physical Laboratory in the United Kingdom and was created as part of a major EU funded research program to develop SIR testing for both material characterization (e.g., conformal coatings, solder masks, solder fluxes and pastes) as well as process material set evaluations.<sup>a</sup>

Following this research effort, Rockwell Collins evolved the TB-57 to reflect certain industry needs prevalent at that time. This became the IPC-B-52 and adopted in the original IPC 9202 and IPC 9203 specifications. It is important to note that the original design was intended to be a "worst case" example of process residue entrapment. The intended goal was of having a World standard for process characterization and validation. In the test method IEC 61189-5-502 Surface Insulation Resistance Testing Assemblies now calls out the IPC-B-52 test coupon.

This document has been written as a companion document to IPC-9202.

In the event that the user wishes to design their own test coupon for the purpose of examining their material set, then it is recommended that reference be made to IPC 9201, SIR Test Handbook, Section 3.3.8 that outlines some important design rules.

The coupon **shall** be manufactured using the same manufacturing process and surface finish intended for the end-product. This is especially important in respect to the PTH sections that are intended to replicate the requirements of thru-hole headers, vias or perhaps press-fit connectors. The user should be aware that laminate choice may impact whether or not conductive anodic filament (CAF) failures (a sub-surface electrochemical migration failure) appear in SIR testing for the IPC-B-52 assemblies. Lower quality laminates have a higher risk of CAF failures.

- **1.1 Definitions** Throughout IPC-9202 and IPC-9203 documents, the words "qualification", "characterization", and "validation" are used with respect to candidate manufacturing processes. These words mean different things to different people, and so a discussion of these terms is pertinent to these documents.

- **1.1.1 Process Characterization** Process Characterization refers to any examination of the effects of a manufacturing process. This may include screening studies, small scale investigations of parameter effects, etc. The goal is to generate data characteristic of that process.

- **1.1.2 Qualification** Qualification is a more formal term. For qualification, the goal of the data generation is to show that the process meets the criteria of a specification or standard, such as IPC-J-STD-001.

- **1.1.3 Validation** Validation is work subsequent to the qualification. Validation is testing that shows the data generated in the qualification proved to be acceptable on actual product.

IPC-9203A November 2022

Example: A process engineer runs SIR evaluations or ion chromatography assessments for a new cleaning chemistry, varying cleaning composition and processing parameters to gain an understanding of the manufacturing boundaries for the cleaning material and equipment. This would all be process characterization as the goal is an understanding of the process. After process characterization, the process engineer processes 10 IPC-B-52 test assemblies and has them tested for SIR per IPC-9202. The data generated is used to provide objective evidence that the cleaning process meets the criteria of IPC-9202 and is a Qualified Manufacturing Process per IPC-J-STD-001. The process engineer then takes hardware produced by this qualified process and does life studies on manufactured hardware to assure that the hardware meets all the design criteria, and that the hardware will function in the end use environment reliably. This would be a validation that the qualified process produces acceptable product.

#### 2.0 APPLICABLE DOCUMENTS

#### 2.1 IPC1

**IPC-A-24-G** Surface Insulation Resistance Artwork (Gerber Files)

**IPC-A-52-G** Cleanliness and Residue Evaluation Test Board Artwork (Gerber Files)

IPC-TR-467 Supporting Data and Numerical Examples for J-STD-001B (Control of Fluxes)

**IPC-5704** Cleanliness Requirements for Unpopulated Printed Boards

IPC-9201 Surface Insulation Resistance Handbook

IPC-9202 Material and Process Characterization/Qualification Test Protocol for Assessing Electrochemical Performance

#### IPC-TM-650 Test Methods Manual

- 2.3.25 Detection and Measurement of Ionizable Surface Contaminants by Resistance of Solvent Extract (ROSE)

- 2.3.28 Ionic Analysis of Circuit Boards, Ion Chromatography Method

- **2.3.28.2** Bare Printed Board Cleanliness by Ion Chromatography

- Surface Insulation Resistance

**IPC J-STD-001** Requirements for Soldered Electrical and Electronic Assemblies

IPC J-STD-004 Requirements for Soldering Fluxes

#### 2.2 International Electrotechnical Commission (IEC)<sup>2</sup>

IEC 61189-5-502 General Test Methods for Materials and Assemblies - Surface Insulation Resistance (SIR) Testing Assemblies

#### 3.0 THE IPC-B-52 TEST VEHICLE

- **3.1 Revision History** The IPC-B-52 test board was an update of the National Physical Laboratory (NPL) Test Board 57 (TB-57).

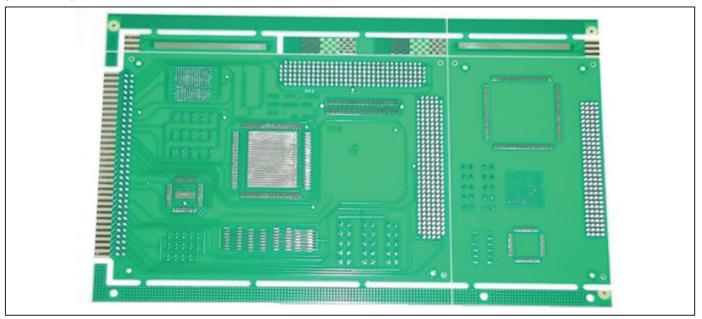

- **3.1.1 Original IPC-B-52** An image of the original IPC-B-52 test board is shown in Figure 3-1a (top side) and Figure 3-1b (bottom side).

Figure 3-1a Original IPC-B-52 Board (Circa 2004), Top Side

<sup>1</sup> www.ipc.org 2 https://iec.ch