IPC-2316

# Design Guide for Embedded Passive Device Printed Boards

Developed by the Embedded Devices Design Subcommittee (D-51) of the Embedded Components Committee (D-30) of IPC

Users of this publication are encouraged to participate in the development of future revisions.

Contact:

IPC 3000 Lakeside Drive, Suite 309S Bannockburn, Illinois 60015-1249 Tel 847 615.7100 Fax 847 615.7105

## **Table of Contents**

| 1 SC  | <b>COPE</b>                                                         |

|-------|---------------------------------------------------------------------|

| 1.1   | Statement of Scope 1                                                |

| 1.2   | Purpose 1                                                           |

| 1.3   | Terms and Definitions 1                                             |

| 2 A   | PPLICABLE DOCUMENTS 3                                               |

| 2.1   | IPC                                                                 |

| 2.2   | National Conference of Standards Laboratories (NCSL)                |

| 2.3   | International Standards 3                                           |

| 2.4   | International Electrotechnical Commission (IEC) Standards           |

| 3 G   | ENERAL INTRODUCTION                                                 |

| 3.1   | History of Embedded Passive Technologies 3                          |

| 3.1.1 | History of Additive Polymer Thick-Film<br>Resistor Technology       |

| 3.1.2 | History of Additive Thin-Film Resistor<br>Technology                |

| 3.1.3 | History of Subtractive Planar Thin-Film<br>Resistor Technology      |

| 3.1.4 | History of Distributed Planar Capacitor<br>Technology               |

| 3.1.5 | History of Polymer Thick-Film Capacitor<br>Technology               |

| 3.1.6 | History of Ceramic Thick-Film and Thin-Film<br>Capacitor Technology |

| 3.1.7 | History of Ceramic Filled Photodielectric<br>Capacitor Technology   |

| 3.2   | Embedded Passive Component Selection<br>Criteria                    |

| 3.3   | Cost Analysis                                                       |

| 3.3.1 | Fabrication and Manufacturing Cost Modeling 8                       |

| 3.3.2 | Embedded Resistor Trimming and Rework<br>Economics                  |

| 3.3.3 | Life Cycle Costs Impacted by Embedded<br>Passives [22]              |

| 3.4   | Product Safety Design Considerations 12                             |

| 4 EI  | MBEDDED RESISTORS 12                                                |

| 4.1   | Physical Characteristics 12                                         |

| 4.1.1 | Resistivity                                                         |

| 4.1.2 | Tolerances 13                                                       |

| 4.1.3 | Temperature Coefficient of Resistance 13                            |

| 4.1.4 | Power 13                                                            |

| 4.1.5 | Short-Time Overload Voltage (STOL) 14                               |

| 4.1.6 | Standard Working Voltage 14                                         |

| 4.1.7 | ESD 14                                                              |

| 4.2   | General Process Design Guidelines                                                     | 15 |

|-------|---------------------------------------------------------------------------------------|----|

| 4.3   | Material Process Guidelines                                                           | 16 |

| 4.3.1 | Additive Techniques - PTF Processing                                                  | 17 |

| 4.3.2 | Additive Techniques - Thin-Film                                                       | 24 |

| 4.3.3 | Additive Techniques - Inkjet Printing                                                 | 24 |

| 4.3.4 | Subtractive Techniques - Thin-Film<br>Processing                                      | 25 |

| 4.4   | Test and Trim                                                                         | 26 |

| 4.4.1 | Electrical Testing Tools                                                              | 27 |

| 4.4.2 | Laser Trim [Subtractive]                                                              | 27 |

| 4.4.3 | Ink Jet [Additive]                                                                    | 30 |

| 5 E   | MBEDDED CAPACITORS                                                                    | 31 |

| 5.1   | Capacitance                                                                           | 31 |

| 5.1.1 | Dielectric Constant                                                                   | 31 |

| 5.1.2 | Capacitance Density                                                                   | 31 |

| 5.1.3 | Dissipation Factor (Df)                                                               | 31 |

| 5.1.4 | Temperature Coefficient of Capacitance                                                | 32 |

| 5.1.5 | Frequency and Voltage Effects                                                         | 32 |

| 5.1.6 | Leakage Current and Dielectric Breakdown                                              | 32 |

| 5.1.7 | Aging                                                                                 | 32 |

| 5.2   | Matching Dielectric Materials to Embedded<br>Capacitor Applications                   | 32 |

| 5.3   | Materials and Processes                                                               | 34 |

| 5.3.1 | Planar Capacitance Laminate Materials for<br>Distributed and Discrete Applications    | 34 |

| 5.3.2 | PTF Capacitance Materials                                                             | 35 |

| 5.3.3 | Ceramic Thick-Film Capacitor Systems                                                  | 36 |

| 5.3.4 | Ceramic Thin-Film Capacitor System                                                    | 37 |

| 5.3.5 | Ceramic-Filled Photodielectric (CFP)                                                  | 39 |

| 6 IN  | NDUCTORS                                                                              | 39 |

| 7 R   | EFERENCES                                                                             | 40 |

| 8 IF  | PC PUBLISHED PAPERS                                                                   | 41 |

| 8.1   | IPC Printed Circuits Expo - March 2003                                                |    |

| 8.2   | IPC First International Conference on                                                 |    |

|       | Embedded Passives - June 2003                                                         | 42 |

| 8.3   | IPC Annual Meeting - September 2003                                                   | 42 |

| 8.4   | IPC Printed Circuits Expo, APEX and<br>Designers Summit Conference -<br>February 2004 | 42 |

| 8.5   | IPC 2nd International Conference on<br>Embedded Passives - June 2004                  | 43 |

| 8.6   | IPC/FED International Conference:<br>Embedded Passive Components -<br>November 2004   | 43 |

| 8.7 | Electronics Circuits World Convention |    |

|-----|---------------------------------------|----|

|     | (ECWC) 10 - February 2005             | 44 |

| 8.8 | IPCWorks 2005 - October 2005          | 44 |

#### Figures

| Figure 1-1  | Discrete Passives 1                                                                                                                                                                                                   |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

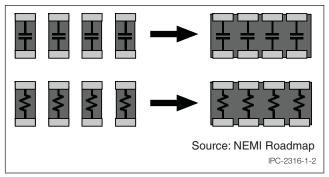

| Figure 1-2  | Passive Arrays 1                                                                                                                                                                                                      |

| Figure 1-3  | IPC, NEMI and JISSO Common Language for Embedded Components 2                                                                                                                                                         |

| Figure 1-4  | Embedded Distributed Capacitor 3                                                                                                                                                                                      |

| Figure 1-5  | Singulated Embedded Passives<br>Construction                                                                                                                                                                          |

| Figure 3-1  | Embedded Passive Selection Process<br>with Cost as a Driver                                                                                                                                                           |

| Figure 3-2  | Embedded Passive Board Cost Tradeoff<br>Model 10                                                                                                                                                                      |

| Figure 3-3  | Distribution of Fabricated Resistor Values 11                                                                                                                                                                         |

| Figure 4-1  | Effect of Squares on Resistance 13                                                                                                                                                                                    |

| Figure 4-2  | Maximum Power Dissipation as a Function of Resistor Area for Thin-Film Material                                                                                                                                       |

| Figure 4-3  | Embedded Resistor Land Patterns on a<br>Power or Ground Layer 15                                                                                                                                                      |

| Figure 4-4  | Design Recommendations for Elements<br>of the Resistor Pattern 15                                                                                                                                                     |

| Figure 4-5  | Misregistration of Subtractive Metal Thin-<br>Film Resistor Images                                                                                                                                                    |

| Figure 4-6  | Thin-Film Additive Resistor Construction 16                                                                                                                                                                           |

| Figure 4-7  | Process Flow for PTF Additive Techniques 17                                                                                                                                                                           |

| Figure 4-8  | Subtractive Process 17                                                                                                                                                                                                |

| Figure 4-9  | Four-Layer (1/2/1) HDI Printed Board with<br>PTF Resistors on Layer 2 – Inset: PTF<br>Printed Resistor                                                                                                                |

| Figure 4-10 | Typical Land Pattern for PTF Resistor                                                                                                                                                                                 |

| Figure 4-11 | Annular Resistor 18                                                                                                                                                                                                   |

| Figure 4-12 | CV vs. Number of Prints 19                                                                                                                                                                                            |

| Figure 4-13 | Linearity of Resistance vs. Resistor Length<br>for Two PTF Inks and, for Comparison, an<br>Alternative Resistor Technology                                                                                            |

| Figure 4-14 | Relative Resistance (actual resistance/<br>theoretical resistance) as a Function<br>of Resistor Length, for 0.25 mm-wide<br>Resistors Printed Parallel to the<br>Squeegee with 2 kohm/square ink                      |

| Figure 4-15 | Relative Resistance (actual resistance/<br>theoretical resistance) as a Function<br>of Resistor Width, for 0.25 mm- and 0.5<br>mm-long Resistors Printed Parallel to the<br>Squeegee with 1 kohm/square ink           |

| Figure 4-16 | Effect of "Fingers" on Relative Resistance 21                                                                                                                                                                         |

| Figure 4-17 | Segmented Resistors for Improved<br>Linearity of Resistance with Width 22                                                                                                                                             |

| Figure 4-18 | Percent Resistance Change after 600 h in 85/85 and 24 h in Air at 125 °C for 0.5 mm Wide Resistors Printed with 10 k $\Omega/\Box$ Ink and Terminated on Bare Copper and Silver and Nickel/Palladium Surface Finishes |

| Figure | 4-19  | Trimmed PTF Resistor                                                                                                             | 23 |

|--------|-------|----------------------------------------------------------------------------------------------------------------------------------|----|

| Figure | 4-20  | Resistor Layer of a Board with 56 Embedded Resistors Ranging from 10 $\Omega$ to 1.5 $M\Omega$                                   | 24 |

| Figure | 4-21  | SEM Cross-Sectional View of Plated<br>Resistor Embedded in a Test Board                                                          | 24 |

| Figure | 4-22  | Printed Linear Resistors                                                                                                         | 25 |

| Figure | 4-23  | Printed Serpentines                                                                                                              | 25 |

| Figure | 4-24a | Laminated Innerlayer Core with Thin-Film Resistor on One Side                                                                    | 26 |

| Figure | 4-24b | Etch Copper and Define Width of Copper Traces                                                                                    | 26 |

| Figure | 4-24c | Etch Exposed Resistor Material Down to Laminate and Define Resistor Width                                                        | 26 |

| Figure | 4-24d | Etch Copper to Define Resistor Length                                                                                            | 26 |

| Figure | 4-24e | Multilayer Embedding of the Resistor                                                                                             | 26 |

| Figure | 4-25  | Pretrim Target and Tolerances                                                                                                    | 27 |

| Figure | 4-26  | Typical Large Panel Mother Board                                                                                                 | 28 |

| Figure | 4-27  | Panelization of Small Printed Boards                                                                                             | 28 |

| Figure | 4-28  | Optimal Resistor Pattern                                                                                                         | 28 |

| Figure | 4-29  | Test Pad Sizes and Spacing                                                                                                       | 29 |

| Figure | 4-30  | Separations between Feature                                                                                                      | 29 |

| Figure | 4-31  | Artwork Registration Challenges                                                                                                  | 29 |

| Figure | 4-32  | A Section of Printed Board Innerlayer Panel<br>with Ni-P Plated Resistors Trimmed by Ink<br>Jet Printing of a Conductive Polymer | 30 |

| Figure | 4-33  | Guideline for Trimming Resistors By Varying Drop Pitch in Print Direction                                                        | 30 |

| Figure | 4-34  | Guideline for Trimming Resistors by Varying the Number of Print Passes                                                           | 30 |

| Figure | 5-1   | Types of Materials to Form Embedded Capacitors                                                                                   | 33 |

| Figure | 5-2   | Technology verses Application for<br>Singulated Capacitors                                                                       | 33 |

| Figure | 5-3   | Capacitance Range for Material Types                                                                                             | 34 |

| Figure | 5-4   | Sequential Lamination of a Single<br>Layer Pair                                                                                  | 34 |

| Figure | 5-5   | Sequential Lamination of a Two<br>Layer Pair                                                                                     | 35 |

| Figure | 5-6   | Noncopper Features of a Distributed<br>Capacitance Power and Ground Plane                                                        | 35 |

| Figure | 5-7   | Process Flow for PTF Discrete Capacitors                                                                                         | 36 |

| Figure | 5-8   | Discrete PTF Capacitor Feature Size<br>Tolerances                                                                                | 36 |

| Figure | 5-9   | Process Flow: Thick-Film Capacitor                                                                                               | 37 |

| Figure | 5-10  | Process Flow: Thin-Film Ceramic<br>Capacitor                                                                                     | 38 |

| Figure | 5-11  | CFP Mezzanine Capacitor Flow [1]                                                                                                 | 39 |

| Figure | 6-1   | Single Layer Spiral Inductor on Organic<br>Substrates                                                                            | 40 |

| Figure | 6-2   | Multilayer 2.5-Turn Spiral Inductor                                                                                              | 40 |

| Figure | 6-3   | Computation of Inductance Using<br>Empirical Expression                                                                          | 40 |

#### Tables

| Table 3-1 | Common Thick and Thin-Film Ceramic<br>Technologies                                                                            |

|-----------|-------------------------------------------------------------------------------------------------------------------------------|

| Table 3-2 | Passive Component Selection Criteria9                                                                                         |

| Table 5-1 | Dielectric Constants for Various Materials 32                                                                                 |

| Table 5-2 | Capacitance of Various Common Discrete<br>Form Factors vs. Thickness and Dielectric<br>Constant of Planar Capacitor Materials |

| Table 5-3 | Capacitor Applications and Requirements 33                                                                                    |

|           |                                                                                                                               |

### **Design Guide for Embedded Passive Device Printed Boards**

#### 1 SCOPE

**1.1 Statement of Scope** This document is a guide to established and emerging embedded passive materials and technologies. It should not be used as an endorsement of any particular material or company product.

**1.2 Purpose** The purpose of this document is to give users and designers of printed boards the necessary information for incorporating embedded passive components into their applications. In addition, it also assists the user in understanding some of the physical and thermal characteristics of the embedded component materials so that their designs can achieve maximum stability and performance.

**1.3 Terms and Definitions** Terms and definitions shall be in accordance with IPC-T-50 and as stated herein.

*Passive Components* – Passive components usually refer to resistors, capacitors and inductors but can also include thermistors, varistors, transformers, temperature sensors, and almost any nonswitching analog device that perform the following functions:

- Provide or absorb energy to maintain a constant voltage or current.

- Filter signals to provide safe signals to other circuits.

- Control impedance.

- Sense signals to transmit information to other circuits.

- Delay or synchronize signals to provide timing to other circuits.

**Discrete** – A single passive element in its own leaded or surface mount technology (SMT) package. Figure 1-1 shows an example of a single resistor, capacitor, or inductor in a 0402 size (generally defined as a 1.0 mm by 0.5 mm [0.040 in by 0.020 in] package). The majority of discrete passives have two electrical contacts that are also used for soldering to the board.

**Passive Array** – A passive array comprises multiple passive components of like function, which are formed on the surface of a separate substrate and packaged in a single SMT case (see Figure 1-2). The case is then mounted on the primary interconnect substrate of the system. Examples include an array of capacitors or an array of resistors.

**Passive Networks** – Passive networks comprise multiple passive components of more than one function, which are formed on the surface of a separate substrate and packaged in a single SMT case. The case is then mounted on the pri-

Figure 1-1 Discrete Passives

Figure 1-2 Passive Arrays

mary interconnect substrate of the system. These passive networks typically have some internal connections to form simple functions such as terminators or filters.

**Integrated Passive Component** – Multiple passive components that share a substrate and package. Integrated passive components may be housed inside the layers of the primary interconnect substrate, which would give them the subdesignation of an *embedded passive component*. Alternately, these components may be on the surface of a separate substrate that is then placed in an enclosure and